基于PCIe总线的数据采集卡设计与实现

肖明国,董明利,2,刘 锋,2,娄小平,2,祝连庆,2

(1.北京信息科技大学 光电测试技术北京市重点实验室, 北京 100192;2.生物医学检测技术及仪器 北京实验室, 北京 100192)

基于PCIe总线的数据采集卡设计与实现

肖明国1,董明利1,2,刘 锋1,2,娄小平1,2,祝连庆1,2

(1.北京信息科技大学 光电测试技术北京市重点实验室, 北京 100192;2.生物医学检测技术及仪器 北京实验室, 北京 100192)

为了实现对多路高速光信号采集,利用FPGA设计基于PCIe总线的数据采集系统;对PCIe总线低速Slave通道与高速DMA通道的关键算法进行了研究;首先,介绍了数据采集卡的硬件构成及基本工作原理,提出了PCIe总线算法需要解决的数据传输问题;然后,分析数据采集卡PCIe总线低速Slave通道和高速DMA通道原理以及实现的关键算法;通过Modelsim和SignalTap工具分别对数据传输算法进行功能验证和在线仿真;最后,将设计数据采集卡互联PCIe上位机进行实际测试;实验结果表明,本设计PCIe总线采用X4接口模式,数据传输系统的数据上传峰值速率为615.38MB/s,可以满足稳定可靠、高带宽、模块化等要求。

PCIe总线;数据采集卡;FPGA;高速数据传输

0 引言

现在的计算机、嵌入式设备中大量使用的总线有PCI、CPCI、VME及它们的扩展。随着系统对带宽要求的逐步提高,高速串行总线越来越多的被采用。传统并行总线标准维护组织如PICMG、VITA,已将高速串行互连技术引入PCI、CPCI和VME总线中,使高速串行总线得到更广泛的应用。PCIe总线就是高速串行总线,第三代IO总线标准,串行总线的特点让PCB信号线减少,布线难度减小、布线性能提高、PCB空间利用效率更高、连接器尺寸更小,而且系统带宽也更高,这提高了设计灵活性,节约了系统成本。PCIe总线使用点到点互连技术,每一个PCIe终端都拥有独立数据连接,各个设备之间并发的数据传输相互独立,避免了其他设备干扰,在稳定性、带宽、可扩展性方面优势明显。

本设计采用PCIe总线互联,利用Altera公司的Cyclone IV GX系列EP4CGX50 FPGA芯片实现,该型FPGA内集成有PCIe硬核,支持PCIe 1.0协议及X4模式,单条通路数据传输率为2.5 Gbps,理论带宽1 GB/s。

实验证明PCIe总线应用于本设计在满足多路高速光信号数据采集要求的同时,基于FPGA的设计可增大系统灵活性,稳定性,板卡的速度快,可扩展性强,系统集成度高。

1 系统构成及工作原理

1.1 数据采集卡硬件构成

本设计数据采集系统采用多板卡可插拔结构,PCB物理结构相同,如图1所示,在上位机通过设备号区分。板卡采用双FPGA结构,外围模块由信号调理模块、多路高精度AD模块、信号校准模块,电源管理模块构成。FPGA1采用Altera公司的Cyclone IV GX系列芯片(内部集成PCIe硬核),完成PCIe总线应用层设计工作。

图1 数据采集卡结构框图

1.2 数据采集卡工作原理

数据采集卡需要采集信号为高速光信号[1-2],设计了基于PMT传感器的多增益多通道信号调理电路,外接PMT模块通过SPI总线和FPGA2交互,PMT输出模拟信号通过屏蔽线接入信号调理模块。信号校准模块由两块DA芯片产生,一块产生高精度电压信号,另一个块控制DA的电压输出,信号转成差分信号后作为信号调理模块的校准信号。电源管理模块实时检测采集卡上关键电压信号。FPGA1(带PCIe硬核)完成多路AD数据参数提取、数据封装、PCIe总线数据传输功能[3-4]。

上位机根据数据采集卡工作状态做出响应、采样频率为80 M的多路高精度AD采集数据,在FPGA中进行数据预处理,然后通过PCIe总线实时上传。

2 PCIe总线实现关键算法

为了实现基于PCIe的数据传输算法,设计了PCIe数据传输结构框图,如图2所示。PCIe硬核是FPGA固有模块,LM配置模块采样PCIe配置空间信号,包括最大读请求、最大负载、总线号及设备号等信息,供TLP数据包装配使用。交互层是一座数据转换的桥梁,将PCIe硬核多个信号进行组装,在应用层有接收、发送模块、DMA读写模块以及Slave从模块[5]。

图2 PCIe数据传输结构框图

设计使用的PCIe硬核完成PCIe总线的物理层、数据链路层设计,这样应用层数据传输算法实现就尤为关键,这里主要包括Slave从模块和DMA写模块的设计,这些设计直接关系到PCIe总线的实际带宽,系统的稳定性,可移植性[6-7]。

针对设计数据采集卡控制命令复杂、带宽要求高的特点,在PCIe总线的应用层设计了Slave读写模块和DMA写模块。Slave模块传输数据采集卡的各种控制命令、状态信息。这些命令数据量不大,要求快速响应。

多路并行AD产生的大量数据预处理后采用固定格式进行封装,用DMA通道上传,DMA结束后发送MSI(内存信号中断)数据包给上位机,完成本次DMA操作。

2.1 Slave实现算法

Slave模块接收上位机的内存读、内存写数据包,根据接收到的数据包完成相应数据操作,如果接收到的TLP数据包是控制命令,直接将这些命令下发到底层模块,由各自底层模块解析处理。如果接收到的TLP数据包为DMA命令,将相应的命令写入DMA控制寄存器,DMA模块根据控制寄存器的状态完成DMA操作。为实现Slave模块功能,设计了图3所示状态机。

在RX_IDLE状态时,根据接收请求信号(rx_req)状态,读取数据包类型,进入RX_DESC_ACK状态。在RX_DESC_ACK状态读取数据包的长度、地址、Tag,同时判断数据包类型,如果是存储器读请求(MRd)TLP,程序将进入RX_START_CPL状态,将数据包地址、数据请求长度字段从内存中读出,组织带数据的完成(CPLD)TLP数据包的发送。如果接收数据包为存储器写请求(MWr)TLP,进入RX_DV_PAYLD状态,然后读出TLP数据包中数据。

图3 Slave模块主状态机

2.2 DMA写模块实现算法

DMA写模块读取DMA控制寄存器状态,通过发送存储器写请求TLP数据完成DMA功能。PCIe总线的DMA操作需考虑数据地址对齐[8]、4K边界、数据包拆分等问题。

有一种方法是约定DMA命令是双字对齐且不跨越4 KB边界,这是DMA数据传输效率很高的一种处理方法。但是这样会限制驱动端程序的灵活性、可移植性。

本设计参考PCIe规范,有效地解决了地址对齐、4K边界对齐及数据拆分问题。在PCIe规范中用4位的First BE和Last BE字段分别表示向前对齐向后对齐[8],相应位为1,则对应的字节有效。

向前X字节对齐使用Headx(Y)函数:

Headx(Y)=Y-(YmodX)

(1)

向后X字节对齐使用Tailx(Y)函数:

Tailx(Y)=Headx(Y)+X-1

(2)

其中:Y是实际地址;X是字节对齐单位。

DMA写模块从DMA控制寄存器中获得PC端地址(Address),长度(Length),单位为双字(DW),结束地址为End_Address。

End_Address=Address+Length-1

(3)

在数据读TLP中,长度(length)字段以DW(双字)为基本单位,通过First DW BE 和Last DW BE字段屏蔽首尾没有对齐的数据。因此L中存放的长度并不是TLP使用的实际长度。

用M表示数据TLP中发送的数据长度

M=(Taillx(B)-Headx(A)+1)≫2

(4)

其中:M的单位为双字,X在应用中为4,通过以上公式可以方便的算出DMA写TLP中Length的长度。

本设计中最大负载(Max_payload)为0x20DW(双字),即DMA写时每个TLP数据包不能超过128个字节,然后根据M的实际大小判断数据的拆分方式。

在算法中利用公式(2)计算TLP数据包的Length(长度),X为4,即双字对齐,当M在1到20之间时,确定相应First BE和Last BE参数。当M大于20时,根据TLP的起始地址A,计算距离此地址最近的128字节对齐的地址,其他TLP以0x80字节对齐,每个内存写请求TLP数据包的长度为128个字节,最后一个数据包的起始地址0x20个DW对齐,结束地址为B。

采用以上方法数据包的发送效率很高,因为0x20是0x1000的公约数,不会超越4 KB。因此设计了DMA写模块状态机框图,如图4所示。

在Idle状态,如果接收FIFO中有数据,进入到RD_DW0状态读出DMA控制寄存器状态,包括源地址、发送长度。在RD_QW1状态更新下一个DMA描述表地址,计算DMA发送完成后的最大地址并进入到TX_LENGTH状态,如果此时程序没有在发送消息信号中断(MSI),按照上文拆包原理计算发送长度,如果此时程序正在发送MSI数据包,则程序返回Idle状态。在TX_LENGTH状态,判断数据发送长度,在START_TX状态,激活发送READY信号进入MWR_REQ状态。在MWR_REQ状态发送帧和数据有效信号,然后进入MWR_DV状态发送数据。在MWR_DV状态计算DMA的实际发送长度,如果数据发送完毕则进入DONE状态机,发送MSI中断,完成完整的DMA写模块。

图4 DMA写模块状态机

3 仿真实验与结果

为了验证上文Slave模块和DMA模块程序的逻辑功能的正确性以及FPGA综合布线后时序收敛,设计了Modelsim功能仿真和SinalTap在线仿真[9]。

3.1 Modelsim仿真实验

本设计数据采集卡为EP(Endpoint)端,Modelsim仿真要求模拟RC端(Root Complex),通过给EP端发送各种测试数据包来进行仿真。

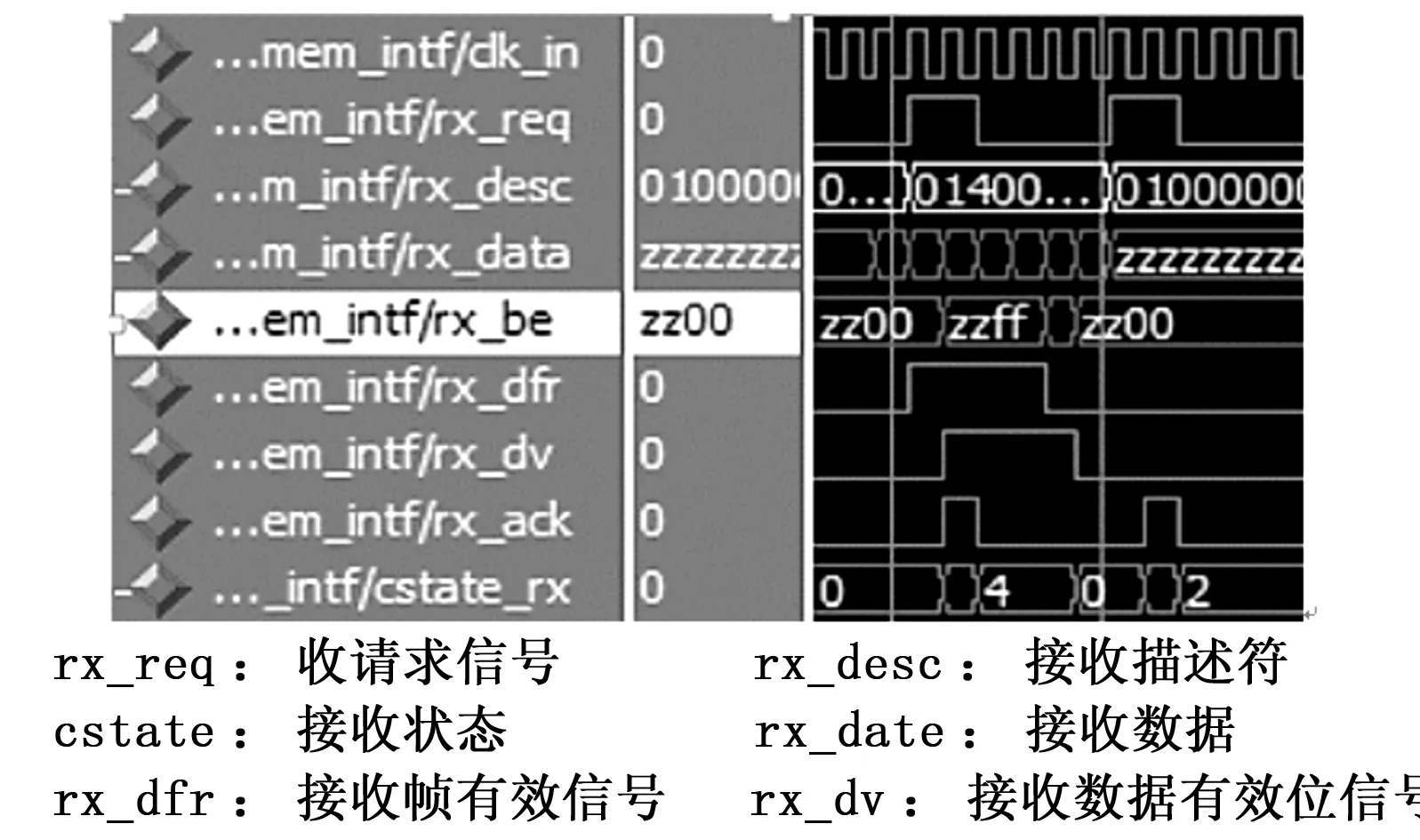

考虑到仿真波形的复杂性,论文提取了几个特征信号来表示相应功能,如图5所示,仿真图描述了RC端给EP端发送数据包时EP端接收到的信号波形图。从仿真图中可以看出Slave模块满足数据接收逻辑功能。

图5 Slave模块仿真波形

图6是DMA写模块数据包仿真图,描述了DMA写模块发送内存写数据包的关键信号波形图,由波形图可知,DMA写模块的逻辑功能正确。

图6 DMA写模块仿真波形

3.2 SignalTap仿真实验

功能仿真完成后,进行综合布线,加载Altera公司提供的逻辑分析仪IP核,用SignalTap工具进行在线仿真,实验时要求硬件连接PC上位机,通过PC端驱动程序运行DMA命令,在PC机上通过SignalTap界面观察信号的波形,图7为DMA写模块的在线仿真波形图。发送请求为高时置位帧有效信号,然后数据有效信号置位,然后开始数据发送。从发送数据(tx_desc)状态可以看出TLP包头为3DW,为带数据的存储器写请求,发送长度为0x20个双字。第一个数据包的发送地址0x9EFD1068,第二个包的发送地址为0x9EFD10E8,发送数据为0,此可知系统DMA写操作满足设计时序。

图7 DMA写模块在线仿真波形

3.3 测试实验

为了实际测试PCIe数据采集卡的数据传输性能,在PC端编写相应驱动程序测试硬件,通过在驱动中进行多次DMA读请求,通过开始结束时间戳来计算DMA数据上传带宽。

实验结果证明:在PC端驱动程序驱动下系统运行正常,工作稳定,测试结果显示数据传输系统PCIe接口数据上传峰值带宽为615.38 MB/s,满足设计需要。

4 结论

本文根据多通道高速光信号采集系统的复杂性,高宽宽特点,以及设计的灵活性、稳定性、低成本性要求,利用带PCIe硬核的FPGA设计了基于PCIe总线的数据采集板卡,首先分析了采集卡的硬件架构、工作原理,然后根据要求设计了基于PCIe总线的Slave从模块、DMA模块,详细分析了本设计TLP数据包拆分原则以及4 K边界对齐问题。实验结果证明:基于PCIe接口数据采集卡设计满足实际应用要求。

[1] Liu X,Huo Z ,Yun H , et al . Application of flow cytometry to rapid detection of bacteria [J]. Microbiology China , 2014,41(1): 161-168.

[2] 裴智果,王 策,陈忠祥,等.用于流式细胞仪的数据采集系统设计与实现[J].电子测量技术,2015(7):84-88.[3] 马晓荣,吴银川.一种多通道数据采集系统设计研究[J].电子设计工程,2012,20(19):14-1.

[4] 马 航,季振宇,史学涛,等. 一种基于FPGA控制的多路并行数据采集设计方法[J]. 医疗卫生装备,2014(2):1-3.

[5] Altera Corporation.IP Compiler for PCI Express UserGuide[Z/OL].http://www.altera.com/literature/ug/ug_pci_express.pdf, 2010.[6] A High Speed DMA Transaction Method for PCI Express Devices[J]. Journal of Electronic Science and Technology of China,2009,04:380-384.

[7] 薛巨峰,黄爱娟.基于PCIe总线的多路复用DMA高速传输系统的设计[J].电子技术,2015(5):87-91.

[8] 郭政慧,王 岩.内存对齐对网络通信程序的影响[J].实验室研究与探索,2010,29(5):68-70.

[9] 郝晓鹏.基于SignalTap Ⅱ和Modelsim的联合仿真技术[J].计算机与网络,2014,(13):46-48.

PCIe Bus Data Acquisition Card Design and Implementation

Xiao Mingguo1, Dong Mingli1,2, Liu feng1,2, Lou Xiaoping1,2, Zhu Lianqing1,2

(1.Beijing Key Laboratory for Optoelectronic Test Technology, Beijing Information Science & Technology University,Beijing 100192, China; 2.Beijing Laboratory for Biomedical Detection Technology and Instrument, Beijing 100192,China)

In order to achieve multi-channel high-speed optical signal acquisition, a data acquisition system based on PCIe bus is established and its applied algorithms such as low-speed Slave channel and high-speed DMA channel are investigated. First, based on hardware structure and basic operating principle of data acquisition card, the algorithms of data transmission problems for PCIe bus are presented.Then,the principles and algorithms of low-speed Slave channel and high-speed DMA channel are analyzed. Function simulation and online simulation of the data transmission algorithm is successfully fulfilled with Modelsim and SignalTap.Finally,plug the data acquisition card into PC for the actual test.Experimental results indicate that the data acquisition system’s peak bandwidth based on PCIe bus with X4 mode is 615.38 MB/s. It can satisfy the system requirements of strong stabilization, high bandwidth, as well as modularization.

PCIe bus; data acquisition card; FGPA; high-speed data transmission

2015-10-12;

2015-11-06。

北京市属高等学校创新团队建设与教师职业发展计划项目(IDHT20130518);教育部长江学者和创新团队发展计划(IRT1212);北京市教委科研计划项目(KM201511232006)。

肖明国(1989-),男,湖北襄阳人,硕士研究生,主要从事生物医学检测仪器方向的研究。

1671-4598(2016)03-0252-03DOI:10.16526/j.cnki.11-4762/tp

TP

A