载波水平移相SPWM控制器的研究

陈 干 苟锐锋 刘 宁 何 岸

(西安西电电力系统有限公司,西安 710065)

载波水平移相SPWM控制器的研究

陈 干 苟锐锋 刘 宁 何 岸

(西安西电电力系统有限公司,西安 710065)

级联多电平拓扑结构广泛用于高压变频调速、无功补偿以及电气化铁路牵引等众多领域,本文对基于此类拓扑结构的载波水平移相SPWM调制控制技术进行了Matlab仿真分析,验证了载波水平移相SPWM调制方法的可行性以及理论分析的正确性。在此基础上应用FPGA器件及其开发环境通过软件编程实现载波水平移相SPWM波形生成,进而设计了三相级联载波水平移相SPWM控制器,并通过代码仿真验证了本方案的可行性。

载波水平移相;FPGA;逆变器;SPWM

基于多载波的 SPWM技术是多电平变换器较常用的调制策略之一,是两电平SPWM技术在多电平变换器中的直接拓展[1]。目前实现多载波 SPWM一般采用载波水平移相(Phase Shifted SPWM,PS-SPWM)和载波垂直移相(Level Shifted SPWM,LS-SPWM)两种技术,前者由于具有等效开关频率高、输出电压谐波含量小、信号传输带宽较大以及控制方法简便等优良特性而广泛应用在级联H桥多电平变流器中。

生成 SPWM脉宽调制波有多种方法,从采用HEF4752、MA818等专用SPWM芯片到单片机或数字信号处理器等,但是随着各种新型SPWM技术的发展对控制芯片提出的更高要求,特别是基于多载波的SPWM技术需要同时输出多路PWM波,数字信号处理器芯片最多只能产生 12路,不能满足要求。FPGA器件处理复杂时序和组合逻辑功能强大,具有现场可编程、代码通用性好、易于扩展等特点[2],对于实现多载波SPWM调制波比较适合。本文按照三相级联H桥多电平主电路的SPWM控制特点,设计了基于不对称规则采样法的载波水平移相SPWM控制器,采用FPGA编程仿真技术实现完整功能。本控制器作为外设与DSP处理器接口,实现多路SPWM信号输出,适用于不同级数H桥串联的控制。

1 载波水平移相SPWM原理模型

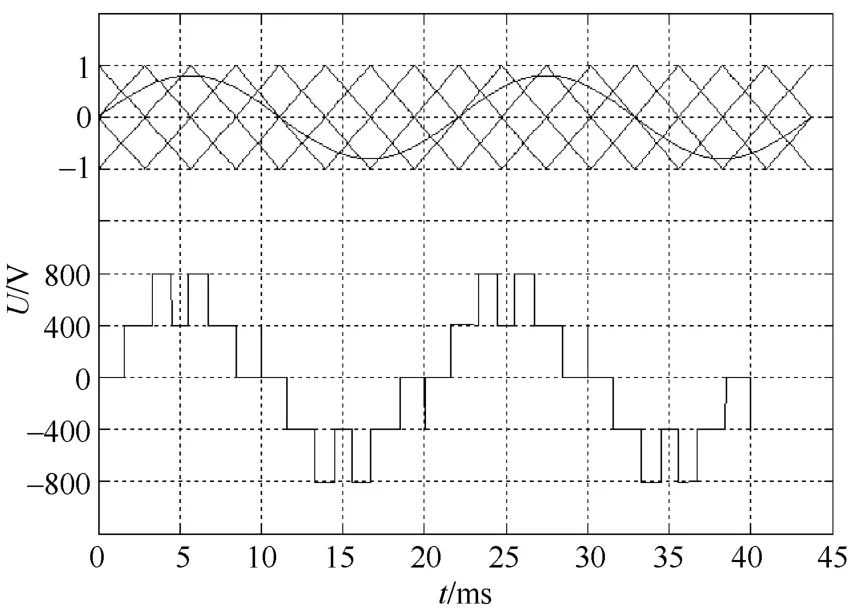

载波水平移相 SPWM调制每个模块的输出脉冲信号都由三角载波和正弦调制波比较直接产生,所有模块使用同一正弦调制波,相邻模块的载波用移相角错开,这就使得各模块产生的SPWM脉冲的基波相位、幅值均相同,但是脉冲不重合,故各模块叠加的最终输出电压等效开关频率大幅提高,可在不提高开关频率的前提下减少输出谐波。对于 n个单元的H桥串联变换器,可以采用2n个载波与一个调制波相交所形成的n个两电平SPWM波进行叠加来实现2n+1多电平输出,各个载波之间角度相差π/n。图1所示为载波水平移相5电平调制及输出电压波形图,主电路采用2个H桥串联,4个载波相位互差π/2。若以该5电平按Y型联接形成三相输出,则输出线电压可以叠加得到9电平电压。

图1 单相5电平逆变器及其电压波形

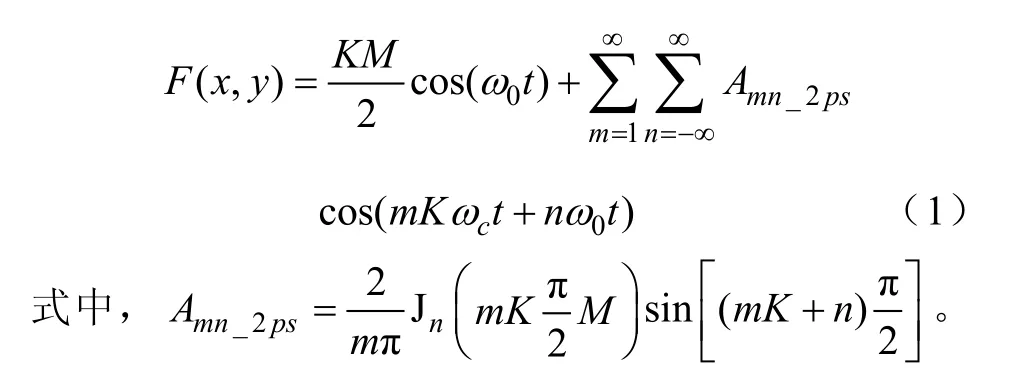

文献[3]中对调制度为M,载波频率为ω0,调制波频率为ωc的K个水平移相的两电平叠加后的电压波形,采用双边傅里叶变换进行理论分析得出,大量不是K整数倍的载波倍数m所对应的载波频率及其边带频率会被消除,输出电压中只包含K整数倍的载波倍数 m所产生的特征谐波,式(1)为其输出电压数学表达式,Jn表示n阶Bessel函数。

由式(1)可见:①在任何调制比下每个 H桥保持相同的输出电压和开关频率,总的输出基波电压幅值是所有两电平基波电压之和KM/2,因而各桥功率相等;②等效载波频率表示为 mKωc,提高 K就可以提高载波频率,使载波倍数的谐波更容易被滤除。载波水平移相多电平SPWM的上述特点使之非常适合模块化多电平变换器。

2 载波水平移相SPWM控制器设计

FPGA实现的载波水平移相SPWM控制器可以节省DSP处理器的宝贵运算资源,为控制系统执行控制策略、提高快速响应能力和精准度提供硬件保障。为此,载波水平移相SPWM控制器需要包含与DSP处理器的接口、SPWM波形发生器、脉冲输出保护接口、正弦波波形发生器等功能模块。图2所示为单相n级联载波水平移相SPWM控制器功能示意图,DSP控制FPGA产生所需的SPWM脉冲,按照载波比和调制度的要求经过计算,DSP将周期寄存器TBPRD、相位寄存器TBPHS、级联数n以及各个表单元的 CMPA比较值等控制信息发送给FPGA,FPGA内的逻辑电路即可输出n组水平移相的H桥SPWM波。三相SPWM的其他两相除了调制波相位相差2π/3外与之相同。

图2 载波水平移相SPWM控制器功能图

2.1 时间基准模块

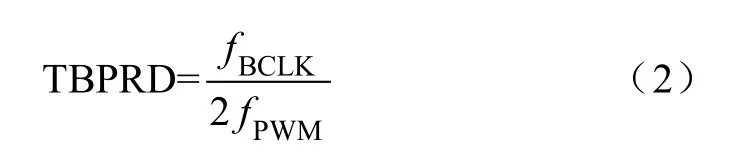

由增减计数器 TBCTR实现三角载波,时间基准周期寄存器 TBPRD和时间基准计数器共同控制PWM的频率,16位增减计数器TBCTR在时间基准时钟 TBCLK下进行自动增减计数,在计数器TBCTR的值等于零和等于时间基准周期寄存器TBPRD值时分别输出CTReqPRD和CTReqZER脉冲信号。基准时钟周期 TBCLK来自锁相环输出,跟随电网频率的动态变化。式(2)给出了周期寄存器TBPRD值的计算公式,其中fBCLK为对应于基准时钟周期 TBCLK的基准时钟频率,fPWM为三角载波的频率,因此可以通过改变 TBPRD的值来获取不同的三角载波频率。

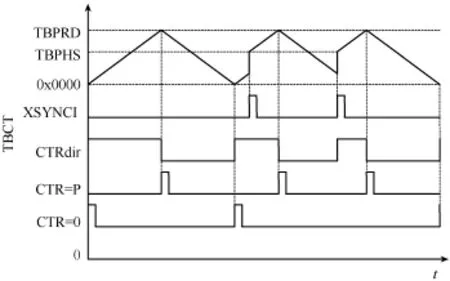

如图3所示,相位寄存器TBPHS的值在同步信号XSYNCI到来时被写入计数器TBCTR当前值,当模式控制寄存器PHSDIR为1时工作在同步立减计数模式,当模式控制寄存器PHSDIR为0时工作在同步立增计数模式。

图3 时间基准波形图

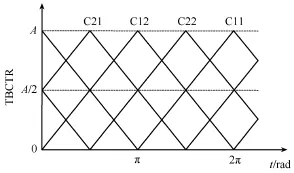

移相三角载波组的产生方法是采用多路计数初值不同的增减计数器来实现的,由于2n路三角载波的相位互差π/n,各个计数器的初值和计数方向也就不同。图4所示为五电平级联电路的4路三角载波,C11、C12与正弦调制波比较产生第一个 H桥的SPWM控制信号,C21、C22则对应第二个H桥的SPWM控制信号。以此类推,FPGA丰富的IO资源足够满足多级H桥级联的需要,工程应用中可根据实际要求配置不同数量驱动板卡对有用的信号进行放大驱动。

图4 5电平移相三角载波

设三角载波的最大值为A,最小值为0,从图4可以看出,C11的初值为A且减计数,C21的初值为 A/2且增计数,C12的初值为 0且增计数,C22的初值为 A/2且减计数。从几何关系可以证明对于任意数量三角载波移相,以初值为A减计数的C11为参考,其他三角载波的计数方向和初始值均可确定。若三角载波相位落后角φ 小于π 为增计数,且其初值应为A-φA/π,若三角载波相位落后角φ 大于等于π 而小于等于 2π为减计数,且其初值应为(φ -π)A/π。因此FPGA设计中接收来自DSP的三角载波数量以及基准频率,即可产生控制不同级联数的H桥换流器多路SPWM脉冲。

2.2 计数比较模块

SPWM调制基本思想是当正弦调制波幅值大于三角载波时输出高电平,当正弦调制波幅值小于三角波时输出低电平。虽然自然采样法有较高的精度,但是求解导通点需要解一个超越方程,因其计算量大通常不被采用。在对称规则采样法基础上提出的不对称规则采样法形成的阶梯波和正弦波逼近程度更好,特别是当载波比N =3或3的倍数时输出的电压中不含偶次谐波分量。

正弦调制波的离散值被送入比较寄存器CMPA,与增减计数器TBCTR的值进行比较产生信号输出。为防止比较寄存器值被软件异步更改而出错,FPGA软件设计中使用映射比较寄存器与增减计数器进行比较操作,而映射寄存器只在三角载波的零点和顶点由CMPA刷新。比较值CMPA必须在0x0000~TBPDR之间,每个PWM周波发生两次比较事件,如果比较值等于0x0000或者TBPDR时,每个PWM周波只发生一次比较事件。SPWM波的占空比等于比较寄存器 CMPA与周期寄存器TBPRD的比值,因而只要比较寄存器 CMPA的值按正弦规律变化就可以产生SPWM波输出了。对于三相SPWM,由U相延迟2π/3、4π/3而得到V、W两相调制波,共用一组三角载波产生移相多载波SPWM波形。

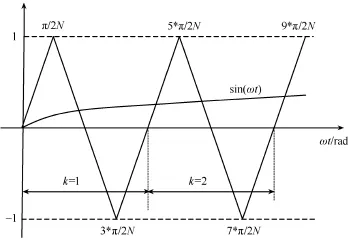

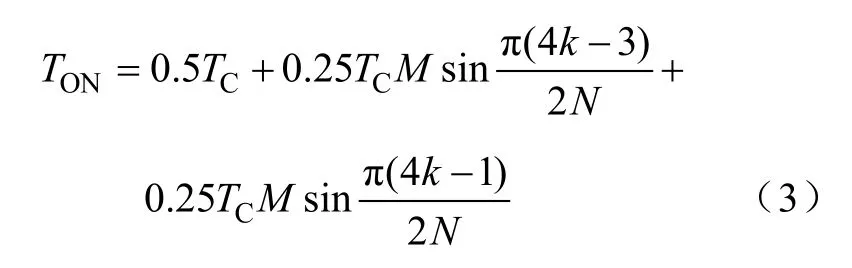

图5 不对称规则采样法

如图5所示,不对称规则采样法在每个三角载波周期采样两次,分别在三角载波的顶点和底点进行采样。式(3)给出触发导通时间的求解公式,式中M为调制比,N为载波比,TC为三角载波周期,k取值为 1,2,…,N。显然 TC的乘积因子值域为(0,1),从而调制过程中CMPA的值在TBPRD以内。当选定载波比N后正弦函数在三角载波各顶点和底点时刻的采样值事先计算,制成数据表格存于FPGA的RAM块中被调用,从而提高运算速度。三相正弦波产生由锁相环模块产生,可以实时跟随电网电压,也可以工作在异步模式。

2.3 死区控制模块

设置死区时间是为防止H桥臂直通而采取的必要办法,死区时间的设置要考虑功率器件的开通关断时间和驱动传输等环节的延迟,FPGA的设计为保证上阀与下阀的开通关断留有可调的缓冲时间[4]。死区模块以比较模块的输出ePWM_N为输入信号,生成ePWMxUP信号和ePWMxD信号,在死区模块里对 ePWM_N取反生成 ePWMxDN信号。ePWMxUP和ePWMxDN分别用于上下桥的控制,且可通过DBRED、DBFED独立设置上升和下降沿死区时间。

2.4 保护模块

当引脚 TZ被外部故障检测信号拉低后,一个基准时钟宽度的低电平就可以触发故障保护逻辑。由PFGA编程控制在发生故障时SPWM控制信号输出为高电平、低电平,这一点考虑配合驱动电路的逻辑正反特点来设计。

3 仿真结果

载波比N越大,输出电压中谐波频率越高,谐波经过低通滤波后的衰减越大,输出电压的THD值越低,波形越接近标准正弦波。但是为了避免桥臂直通短路需要加入死区控制时间会随着载波频率的增加而增强,从而导致了输出电压THD增大,因此工程上选取载波比需要综合考虑功率器件的最大允许开关频率、死区时间、输出电压THD指标等要求,一般功率较大的设备载波比较小[5]。本文仿真验证为突出显示SPWM波形特征,选取载波比N为9,调制比M取0.8,死区时间为2.5μs,使用ISE11.1及Modelsim仿真工具对上述设计进行代码仿真,得到相应的输出波形。

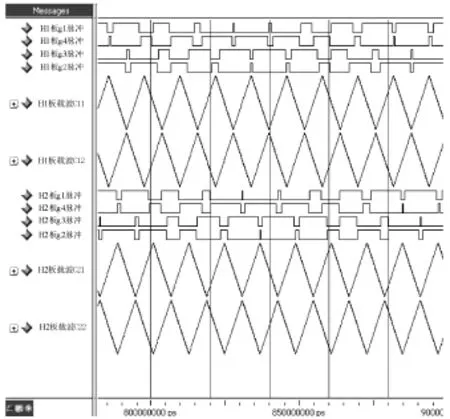

图6所示为2个H桥串联形成5电平SPWM波的实例,H1桥载波C11和C12相差180°,H2桥载波C21和C22相差180°,这两组载波错开90°形成4个等相差的三角载波,共用同一个正弦调制波比较产生8路SPWM波输出。按单极性调制法每一个三角载波产生一个桥臂的两个SPWM信号,例如H1桥载波C11与正弦调制波比较产生H1桥g1和g4控制信号,g1和g4信号之间可以设置死区时间。可见SPWM波形占空比随正弦规律变化,实现了不对称规则采样下移相多载波SPWM控制功能。

图6 单相5电平多载波SPWM波形

4 结论

通过仿真分析验证了移相多载波 SPWM调制算法的可行性,研究的主要创新点在于采用 FPGA程序模块化设计实现了不对称规则采样法控制的移相多载波SPWM输出功能,对于不同级联级数的单相或者三相拓扑结构有普遍适应性,通过与DSP的接口方便实现输出电压幅值和相位的调节,特别适合级联多电平逆变器。以FPGA和DSP为核心的控制系统设计具有硬件资源丰富、配置灵活等优点,对于H桥串联拓扑类型结构的电力电子产品研发设计提供了技术支撑。

[1]王云亮.电力电子技术[M].北京:电子工业出版社,2013.

[2]田耘,徐文波.Xilinx GPGA开发实用教程[M].北京:清华大学出版社,2008.

[3]周京华,陈亚爱.高性能级联型多电平变换器原理及应用[M].北京:机械工业出版社,2013.[4]蔡学波,章国宝.基于IGBT的链式SVG的研究[J].电子设计工程,2011,19(18):137-140.

[5]曹长松,李曼.逆变器 SPWM载波频率选取的计算方法[J].电力电子技术,2012,46(5):62-65.

[6]王衡,李纵,李文彬,等.基于 Matlab和 FPGA的SPWM 波形的实现[J].舰船电子工程,2013,33(7):49-50,75.

[7]任辉,吴观茂,樊冠林.基于DSP的SPWM调制的实现[J].煤矿机械,2006,27(9):183-185.

[8]李帆,薛士龙,耿攀,等.基于TMS320F28335的单极性SPWM的实现[J].通信电源技术,2014,31(2):1-3,15.

Research on Carrier Level Phase Shift SPWM Controller

Chen Gan Gou Ruifeng Liu Ning He An

(Xi'an XD Power System Co.,Ltd,Xi'an 710075)

Cascade multilevel topology is widely used in high voltage variable frequency speed regulation,reactive power compensation and electrified railway traction etc.This paper on such topological of the carrier level phase-shift SPWM modulation control technology based on Matlab simulation analysis,which verifies the feasibility and correctness of the theoretical analysis of the carrier wave SPWM modulation method.On the basis of the application of FPGA device and its development environment through software programming to realize the level of carrier phase shifting SPWM waveform generation,then design the three-phase cascade level of carrier phase shifting SPWM controller,The feasibility of this scheme is verified through code simulation.

carrier based phase shifted SPWM; FPGA; inverter; SPWM

陈 干(1978-),男,工程师,主要从事高压直流输电换流阀和无功补偿设备的研究和设计工作。

—— “T”级联