基于多路并行插值的高频信号产生方法研究

邢长昕+钱博

【摘 要】为满足无线通信过程中产生高频、高精度通信信号源需求,深入研究了基于多路并行插值的高频信号产生机理,在ISE软件环境下采用verilog硬件描述语言对高频信号发生器进行了设计, 基于XILINX V6XC6VLX240T-2ff1156 FPGA进行了实现。测试结果表明,该信号发生器能输出稳定的高频、高精度通信信号。

【关键词】多路并行插值;高频信号;verilog

0 引言

随着通信技术的高速发展,数字信号处理理论和方法已成为众多研究领域的重要研究基础,被广泛应用于航空航天,通信等领域。随着通信业务的增多,有限的频带资源难以满足日益增长的通信业务量需求。为提高高频段的应用,通信信号的带宽和频域不断增大,需产生更高频率的信号。因此,进行高频信号产生方法的研究具有实际应用价值[1]。

使用FPGA器件进行数字系统设计,不仅可以简化设计流程,而且可以降低整个系统的体积和成本,增加系统的可靠性[2]。鉴于此,本文基于多路并行插值技术,采用FPGA硬件平台进行了高频信号产生方法研究,并进行了仿真验证。

1 插值基本原理

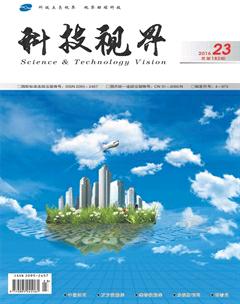

2路插值原理如图1所示, a图表示在八分之π相位时相位抽取得到的相位信息, b图表示另一种相位抽取得到的相位信息, c图表示两种相位插值后得到的信号相位信息。

多路并行插值产生高频信号的思路为:首先产生N路低采样率高频信号分量,通过对各信号分量相位进行控制,确保每路信号分量以低采样率采出高频信号的M个相位,且信号分量间的采样相位彼此交错;通过将N路低速信号分量共N*M个相位按顺序依次进行插值,并输出至单个DA,使得DA输入端呈现采样率为N倍的高频信号,从而实现高频信号的插值。

2 多路并行插值高频信号发生器设计

2.1 整体结构

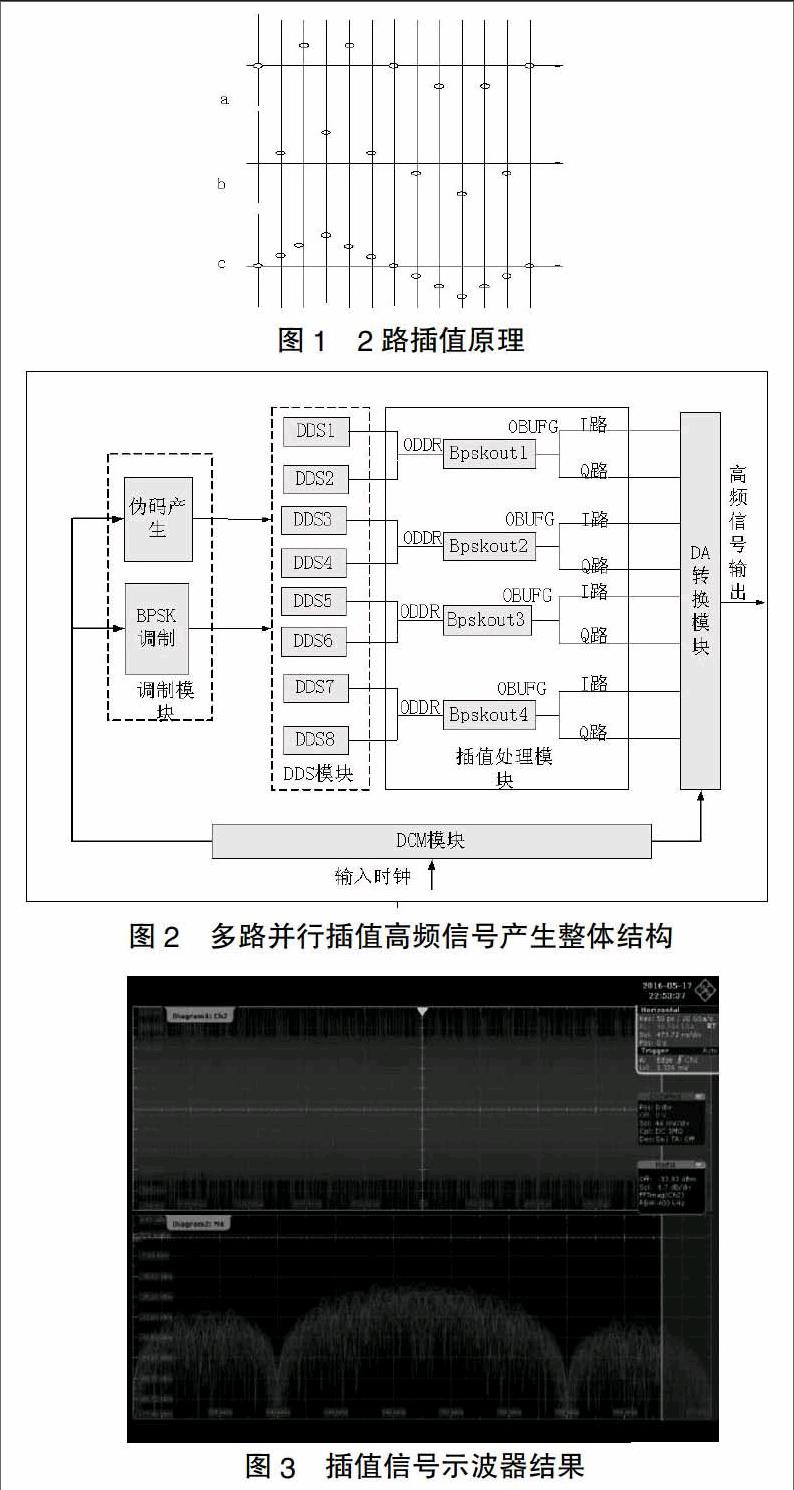

多路并行插值高频信号产生的整体结构如图2所示,共包含5个关键模块:DCM模块,BPSK调制模块,DDS模块,插值处理模块和DA转换模块。其中,DCM模块为其他各模块提供不同的时钟驱动;BPSK模块实现对高频信号的调制;DDS模块产生了8路DDS IP 核和实现了相位控制;插值运算模块完成了多路并行插值;DA转换模块将数字高频信号转变为模拟高频信号输出。

2.2 关键子模块设计

2.2.1 插值运算模块

高频信号产生的关键在于插值运算模块的实现。DDS模块产生8路低采样率高频信号分量,频率控制字通过对各信号分量进行相位控制,每路信号分量以低采样率采出高频信号分量的8个相位。各信号分量的采样相位彼此交错,而OBUFDS是将标准单端口信号转换成差分信号。通过OBUFDS产生差分信号对进行插值。八路低速高频信号分量插成四路低速高频信号分量,差分信号对经过ODDR输出到DA转换模块,在DA转换模块中数字高频信号转换成为采样率为2GHZ的模拟高频信号。

2.2.2 bpsk调制模块

Bpsk调制模块的主要功能是对信息码与伪随机序列模二和后数据流的bpsk调制。输入时钟250MHz,伪码产生模块主要完成伪随机序列的产生,模块根据既定的伪码多项式和伪码初相在伪码时钟的作用下产生连续的伪随机数据流。设计采用模块式码序列发生器,它的模二在各级触发器之间,模二加的动作是同时并行的,延时小,工作速度高。

2.2.3 DDS生成模块

DDS生成模块包括产生8路DDSIP核和相位控制字,系统输入时钟频率CLK为250MHz,载波频率为150MHz,输入为30位的频率控制字。八路并行的DDS都以系统时钟频率工作,在系统时钟和频率控制字的作用下进行插值,产生高频信号。相位控制字模块为计算DDSIP核的相位控制字P1。

3 仿真验证

本设计采用XLINX XC6VLX240t -2ff1156 FPGA进行实现,调制方式采用bpsk调制,输入时钟250MHz,实现插值产生的150MHz信号的示波器显示结果如图3所示。

从图3可见,正确产生了中心频率为150MHz、带宽20MHz的直扩信号。

4 结语

本文在深入研究高频信号多路插值产生原理基础上,利用可编程逻辑器FPGA实现了基于多路并行插值的高频信号产生功能。可通过调节相关参数获得所需频率的信号。仿真结果表明,成功实现了稳定的高频、高精度通信信号。

【参考文献】

[1]杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子和信息学报,2010,32(3).

[2]赵丽娜,郭宝增,刘少鹏,等.基于FPGA的DDS基本信号发生器的设计[J].电子设计工程,2012,20.

[3]杨建华,于小宁,朗宝华.DDS技术和FPGA在多功能信号源中的应用[J].西安工业大学学报.2012,32.

[4]于洪辉.基于FPGA的函数波形发生器设计[J].机电技术,2012,35(2).

[责任编辑:王伟平]