基于分时复用策略的EtherCAT从站IP核设计及实现*

宋 宝,徐 健,刁思勉,唐小琦

(1.华中科技大学 机械科学与工程学院,武汉 430074;2.中国地质大学(武汉)研究生院,武汉 430074)

基于分时复用策略的EtherCAT从站IP核设计及实现*

宋宝1,徐 健1,刁思勉2,唐小琦1

(1.华中科技大学 机械科学与工程学院,武汉 430074;2.中国地质大学(武汉)研究生院,武汉 430074)

在分析工业以太网EtherCAT协议基础之上,针对现今EtherCAT从站采用专用ASIC或者商用IP核实现的成本高、不灵活等问题,提出了一种基于通用FPGA的实现方法。该方法根据数据帧驱动特性的分时复用策略,将EtherCAT从站IP核中的各个功能模块任务进行分类,利用FPGA的并行特性进行模块任务的串并行调度,实现了在无数据帧缓存的条件下EtherCAT从站IP核。实验结果表明,基于该方法设计及实现的IP核不仅具有良好的兼容性和稳定性,还具有更为优良同步特性和快速响应特性。

EtherCAT从站;分时复用;IP核

0 引言

现场总线技术在自动化系统中得到了越来越广泛的应用,特别是在基于实时以太网的现场总线控制系统中,如高端数控加工、机器人控制等实时领域[1-2]。实时工业以太网协议EtherCAT由于其具有高效率、支持多种拓扑、同步性能好等特点,广泛应用在各类设备当中[3]。

EtherCAT控制系统的要求EtherCAT从站控制器具有协议兼容一致性、低延时地快速响应性、持续地稳定可靠性和高精度的同步性[4-5]。EtherCAT从站的实现可以采用从站专用控制芯片或者IP核,如采用Beckhoff公司的ET1100进行EtherCAT伺服驱动器和数据采集系统设计[6-8],采用TI公司的AM335x进行运动控制和驱动软件的研究[9-10],未曾见有文献提及EtherCAT从站IP核的设计方法及思路。

因此,为解决专用芯片和商用IP核成本高、系统集成不灵活等问题,本文提出了一种基于通用FPGA实现EtherCAT从站控制器的方法。该方法基于数据帧驱动特性的分时复用策略,将EtherCAT从站IP核中的各个功能模块任务进行分类,利用FPGA的并行特性进行模块任务的串并行调度,实现了在无数据帧缓存的条件下EtherCAT从站IP核,具有平台灵活性好、成本低等优势。

1 EtherCAT从站IP核的分时复用策略

以从站控制器收发数据通道中的数据帧特性进行分析,如图1所示,在一个定时周期Tcycle_time内,从站会收到周期性数据帧和若干非周期性数据帧,这些数据帧之间的间隔tδframe由主站控制器设定,其最小值为960ns,考虑物理层链路的抖动为tjitter,帧长为tframe,数据帧处理延时为tdelay。为使从站控制器处理连续数据帧时双口RAM不冲突,应该满足以下条件:

其中,tdelay直接反映了从站控制器的响应特性,其值越小越表示其响应特性越好。

图1 从站收发数据帧特性分析

为确保在实现协议功能的前提之下,尽量减小tdelay,提出了一种基于数据帧特性驱动的多任务分时复用调度策略,如图2所示。基于数据帧驱动特性的从站IP核的任务可以根据数据帧进行分类和划分,利用FPGA的并行操作特性可以实现各类任务之间的串并行调度,实现无缓存数据帧条件下的多任务处理,避免了传统存储转发的长延时,从而极大程度地减小了tdelay。

从站IP核根据双口RAM抢占分时复用特性将各个功能模块的任务划分为两类,一类是基于数据帧驱动的模块任务,比如双口RAM数据的上传和下载,CRC32校验等;而另一类是并行与整个从站IP核的运行过程,不以数据帧为驱动特性的模块任务,比如PHY链路的状态管理,PDI接口等。根据整个从站IP核实现的分时复用的快速响应策略,数据帧从PHY芯片到达FPGA后,经过PHY链路管理模块将数据rxd/rxdv送至数据帧接收端口,之后同时根据帧结构驱动的分时复用策略执行双口RAM操作和CRC32校验两个模块的任务。

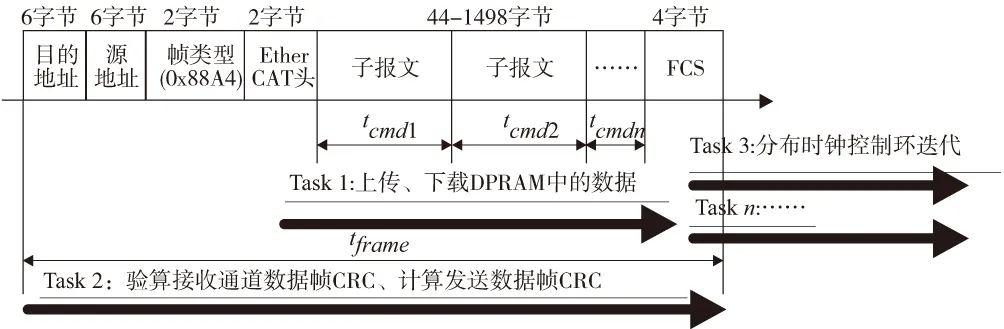

图2 数据帧分时复用驱动策略

其中,双口RAM操作模块无缓存地产生发送数据帧,直接驱动CRC32计算模块,计算新产生数据的CRC数值,附于帧尾后转发至下一节点。另一个CRC32校验任务从帧头部分一直持续到帧尾部分,若帧尾CRC校验正确,则按照优先级次序依次抢占调用双口RAM。同时根据帧类型驱动的分时复用策略执行数据帧内容驱动的任务模块,如分布时钟控制环、SII EEPROM接口操作和应用层状态更新等任务。

以EtherCAT数据帧驱动为例,其格式如图3所示。利用数据帧分时复用的驱动特性,将从站IP核中的功能模块任务按照EtherCAT数据帧结构的定义进行分时调用。其中,每个子报文所占的时间为tcmdn,数据帧只有在子报文的有效数据范围内才会上传和下载双口RAM中的数据,因此,为了满足无缓存数据的数据帧发送,tcmdn即为子报文抢占调用双口RAM的时间;同时,该数据帧驱动了全数据帧范围的任务,从帧头至帧尾部分,数据帧驱动CRC验算模块,验算接收通道数据帧CRC,并计算发送数据帧CRC;在数据帧结尾,CRC验算成功后开始执行周期性类型帧的驱动任务;当然, EtherCAT从站IP核中同时驱动并不以数据帧来驱动的模块,其并不影响无缓存数据的数据帧发送。

图3 数据帧驱动特性的从站IP核调度

因此,基于数据帧驱动特性的分时复用策略实现了在无缓存数据帧的条件下,从站IP核直接进行低延时地处理和转发,从而极大程度上减小了tdelay,确保了从站控制器的快速响应特性;其次,实现了EtherCAT协议所要求的从站控制器的各个功能模块,并且利用FPGA的并行操作特性可以方便集成在从站控制器当中,确保了协议兼容的一致性;当然,各个模块任务在以数据帧驱动特性为核心的调度之下,避免了各个功能模块间抢占调用双口RAM产生的冲突,提高了整个IP核的执行效率和稳定性;最后,以数据帧驱动特性作为支持分布时钟的控制环输入,可以在更新参考时钟后及时进行控制环的迭代来校准本地系统时间,实现各个节点之间的高精度的同步性能。

2 EtherCAT从站IP核实现关键技术

基于数据帧分时复用驱动的从站IP核收发数据时序图如图4所示,以RMII为例,数据帧在每次缓存完一个字节后进行产生CRC计算信号使能CRC校验模块计算一次产生CRC结果,依次类推,到有效数据接收完成后计算产生数据的校验值;同时,在原有数据帧接收完成帧尾后判断是否进行相应任务的操作。另一方面,双口RAM的操作模块根据接收通道中的数据产生发送数据txd_reg[1..0],与CRC校验相同,CRC计算模块计算该帧的CRC数值,将其置于帧尾并产生发送数据帧txd至下一节点。由图中可以看出,发送数据txd[1..0]相对于接收数据rxd[1..0]的tdelay仅有两个时钟周期,满足了从站控制器的快速响应性能要求。EtherCAT从站IP核的分布时钟控制环同步作为周期性数据帧驱动的一个模块子任务,其同步算法流程图如图5所示。其中,本地时钟local_time由上电系统启动后开始运行,分布时钟控制的同步任务就是使本地系统时钟与参考系统时钟一致,包括两方面的内容,其一是初始偏移量Toffset的补偿,其二是实时动态补偿漂移的过程。当含有参考时钟的数据帧到来,锁存本地系统时间副本tlocal_copy_sys_time和tsys_ref作为本周期的分布时钟控制环的输入,计算本地时钟漂移:

Δt=tlocal_copy_sys_time-Tdelay-tsys_ref

其中,Δt表示本地系统时钟与参考系统时钟的漂移量,根据控制算法流程,在以后的控制环的Δt个刷新周期内,每次补偿1ns来补偿Δt的时钟偏移量。以周期性数据帧进行每个周期的分布时钟控制环输入,可以使本地系统时钟与参考时钟保持动态一致,从而使各个节点同时产生SYNC/Latch同步信号。

图4 从站IP核收发数据时序图

图5 从站IP核同步流程图

3 系统测试及结果分析

为验证测试基于分时复用策略的EtherCAT从站IP核,针对基于此方法设计的TSV-HL伺服驱动器进行了响应性能、同步性、稳定性和兼容性测试。

首先,搭建了利用FPGA主站分别测试从站IP核和ET1100快速响应的实验平台,仿真测试结果如图6所示,以主站发送使能和接收使能之间的间隔作为两种方案响应能力的评价指标,其中,IP核方案的响应时间为740ns,而ET1100的响应时间为920ns。从中可以看出,基于分时复用策略的EtherCAT从站IP核具有优越的快速响应能力。

图6 快速响应能力测试对比结果

图7 同步信号产生仿真图

以Beckhoff公司TwinCAT软件作为主站测试了两轴TSV-HL伺服驱动器的同步性能,其观测采样同步产生信号的仿真图如图7所示,其采样时钟为100MHz。其中,主站同时使能SYNC0和SYNC1同步信号,周期为1ms,SYNC1滞后SYNC0信号1000ns,从产生的SYNC信号可以看出单轴仿真测试的同步信号输出达到了主站的控制要求。

利用示波器余辉功能,通道1以参考节点SYNC0信号作为触发条件,通道2观测另一节点的SYNC0信号,测试结果图如图8所示。可以看出相对于参考节点的平均误差大致为-20ns,抖动大致为±20ns,相比较于采用ET1100方案的某伺服驱动器的±300ns而言,具有较为优良的同步性能。

图8 两轴同步信号SYNC示意图

以TwinCAT+单轴TSV-HL伺服驱动器进行稳定性测试,以2ms的通信周期进行连续12h不间断地运行,测试其丢帧和错帧等情况,测试结果如图9所示,可以看出不论从TwinCAT监测还是从站IP核中的错误计数器监测,都不存在丢帧和错帧的现象,从而反应出基于分时复用策略从站IP核的稳定性。

图9 稳定性测试结果

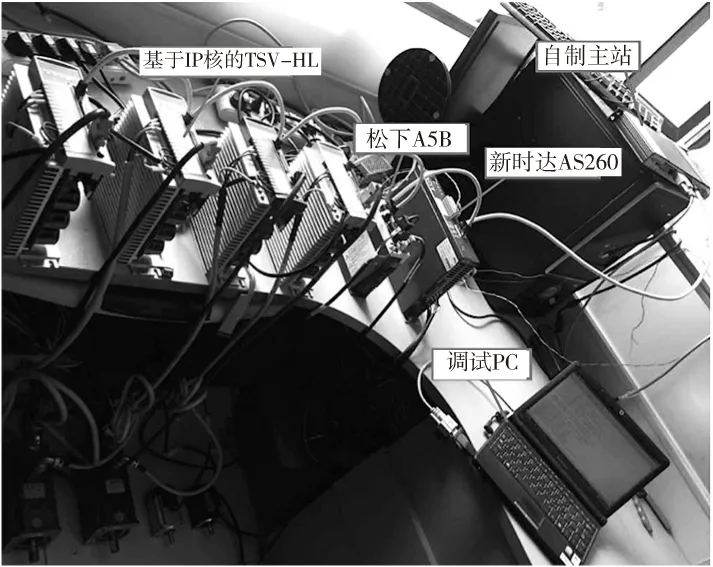

为测试从站IP核的兼容性,搭建了如图10所示的测试平台,包括自制主站、新时达AS260伺服驱动器、松下A5B伺服驱动器和四台TSV-HL伺服驱动器,测试平台能够正常无故障地运转,表明从站IP核能够兼容在标准的EtherCAT网络中,能够适应标准EtherCAT接口设备的互操作性连接。

图10 兼容性测试平台

4 结束语

实验结果表明,本文提出的基于分时复用策略的EtherCAT从站IP核设计和实现方法,能够在通用低成本FPGA平台的基础之上实现EtherCAT通信接口的功能,具有良好的兼容性和稳定性;并且有相对于专用ASIC方案而言,具有更为优良的同步特性和快速响应特性,对灵活低成本在设备上集成EtherCAT接口具有良好的借鉴意义,具有广泛的工程应用前景和市场价值。

[1] 冯世宁, 马杰, 赵雪飞. 若干种实时以太网标准的比较[J]. 南京师范大学学报: 工程技术版, 2010, 10(2): 88-92.

[2] Vitturi S, Peretti L, Seno L. Real-time Ethernet networks for motion control[J]. Computer Standards & Interfaces, 2011, 33(5): 465-476.

[3] 徐健, 宋宝, 唐小琦. EtherCAT 与 Modbus 协议转换网关的设计及实现[J]. 组合机床与自动化加工技术, 2015(4): 71-73.

[4] Kim K, Sung M, Jin H W. Design and implementation of a delay-guaranteed motor drive for precision motion control[J]. Industrial Informatics, IEEE Transactions on, 2012, 8(2): 351-365.

[5] Cena G, Bertolotti I C, Scanzio S. Evaluation of EtherCAT distributed clock performance[J]. Industrial Informatics, IEEE Transactions on, 2012, 8(1): 20-29.

[6] 李文虎, 李叶松, 王江城. 伺服驱动器 EtherCAT 接口设计[J]. 电气传动, 2011, 41(7): 51-55.

[7] 李木国, 王磊, 王静, 等. 基于 EtherCAT 的工业以太网数据采集系统[J]. 计算机工程, 2010, 36(3): 237-239.

[8] 郭忺. 实时 EtherCAT 通讯的交流伺服驱动器研究[D]. 广州:华南理工大学, 2014.

[9] 赵巍. 基于 EtherCAT 总线的运动控制器通信系统设计与实现[D]. 哈尔滨:哈尔滨工业大学, 2013.

[10] 任计羽. EtherCAT 从站软件的设计与实现[D]. 成都:中国科学院研究生院 (光电技术研究所), 2014.

(编辑赵蓉)

Design and Implementation of the EtherCAT Slave IP Core Based on Time Division Multiplexing Strategy

SONG Bao1, XU Jian1, DIAO Si-mian2,TANG Xiao-qi1

(1.School of Mechanical Science and Engineering, HuaZhong University of Science and Technology, Wuhan 430074, China;2. Graduate School, China University of Geosciences, Wuhan 430074, China )

In the analysis of industrial Ethernet EtherCAT protocol basis for today EtherCAT slave or commercial use of special ASIC IP core to achieve the high costs, inflexible and other issues, a common FPGA-based implementation method is proposed. The method according to the driving characteristics of the data frame of time division multiplexing strategy, classifying the EtherCAT slave IP Core individual functional modules mission, carrying out modules tasks with serial and parallel scheduling using FPGA parallel feature to achieve in the absence of data-frame buffer conditions under EtherCAT slave IP Core. Experimental results show that the design and implementation based on the method of IP Core not only has good compatibility and stability, but also has more excellent synchronization characteristics and fast response.

EtherCAT slave;time division multiplexing;IP Core

1001-2265(2016)04-0026-03DOI:10.13462/j.cnki.mmtamt.2016.04.007

2015-06-12

“高档数控机床与基础制造装备”科技重大专项(2012ZX04001041)

宋宝(1974—),女,湖北黄冈人,华中科技大学副教授,研究方向为数控技术、嵌入式系统,(E-mail)songbao@mail.hust.edu.cn。

TH166;TG659

A