扫描SAR成像中SPECAN算法的FPGA实现*

柯 磊,庞 龙

(1.攀枝花学院交通与汽车工程学院,四川攀枝花 617000;2.中国传媒大学信息工程学院,北京 100024)

扫描SAR成像中SPECAN算法的FPGA实现*

柯 磊**1,庞 龙2

(1.攀枝花学院交通与汽车工程学院,四川攀枝花617000;2.中国传媒大学信息工程学院,北京100024)

为满足扫描成像合成孔径雷达(SAR)系统小型化和低功耗的迫切需求,给出一种频谱分析(SPECAN)算法的现场可编程逻辑门阵列(FPGA)实现,整个成像流程被划分为多个时分的阶段并分配到可复用的运算单元和控制逻辑中,并且提出一种基于FPGA的优化处理结构,将所有的信号处理功能集成在单片FPGA中。在实验与验证部分,通过FPGA处理结果与MATLAB运算结果的对比,以及实际成像试验结果表明了设计正确性和结构的工程实用性,适用于机场跑道、汽车高速公路的检测和定位。

扫描合成孔径雷达;频谱分析算法;FPGA实现

引用格式:柯磊,庞龙.扫描SAR成像中SPECAN算法的FPGA实现[J].电讯技术,2016,56(3):319-323.[KE Lei,PANG Long.FPGA imP1ementation of SPECAN a1gorithm in ScanSAR imaging[J].Te1ecommunication Engineering,2016,56(3):319-323.]

1 引 言

扫描合成孔径雷达(Scan Synthetic APerture Radar,ScanSAR)的宽测绘带能力是通过对各扫描波束形成的子带图像进行距离向拼接实现的,广泛应用于自然灾害评估、海洋气候预测等场合[1-2]。频谱分析(SPectra1 Ana1ysis,SPECAN)算法广泛应用于ScanSAR成像中,与其他成像算法如距离多普勒(Range-DoPP1er,RD)算法和线性调频变标(ChirP Sca1ing,CS)算法相比,具有处理流程简化并易于工程实现的优点。

SPECAN算法的实时处理非常具有挑战性,因为整个处理流程牵扯到高实时性要求的运算任务、复杂的控制和调度逻辑。SAR实时信号处理系统可以使用多片信号处理器(Digita1 Signa1 Processor,DSP)作为工程实现的硬件平台[3-5],但DSP时序控制能力较弱,过高的功耗会给系统可靠性带来严重威胁。相比之下,现场可编程逻辑门阵列(Fie1d Programmab1e Gate Array,FPGA)具有更低的功耗和更强大的实时处理能力,并且随着片上系统(System on ChiP,SoC)技术的发展,FPGA的成本与开发难度也在不断降低,使得FPGA不断地取代DSP成为雷达系统平台的首选平台[6-8],从而满足系统小型化和低功耗的需求。

本文基于对运算模块和控制逻辑的可重配置与复用的设计原则,提出一种优化的SPECAN算法的实现结构,并且针对扫描SAR的应用实例,将整个信号处理流程成功的在单片FPGA中进行实现。最终的试验结果表明了整个扫描SAR系统的正确性,并且验证了提出的结构的工程适用性。

2 SPECAN算法处理流程

SPECAN算法由对线性调频信号的拉伸处理发展而来的,通过在方位向使用快速傅里叶变换(Fast Fourier Transform,FFT)和去斜处理来进行频谱分析。典型的信号处理流程如图1所示,获得高分辨率图像需要经过以下步骤:一是距离维数字脉冲压缩;二是多普勒中心频率估计;三是距离徙动校正;四是多普勒斜率估计;五是方位向去斜和FFT处理;六是图像几何拼接处理。

图1 SPECAN算法的信号处理流程Fig.1 The signa1 Processing f1ow of SPECAN a1gorithm

在SAR成像系统中,线性频率调制(Linear Frequency Modu1ation,LFM)信号通常作为发射信号,因此SPECAN算法通过数字脉冲压缩获得距离高分辨率。在工程实现中,数字脉冲压缩通常在频域中实现,包括FFT、与参考因子的复乘和FFT逆变换(Inverse FFT,IFFT)处理。

由于雷达目标平台运动的多普勒效应,需要进行距离徙动校正,在频域中通过与相位因子的复乘来完成。因此,构建相位因子需要在方位向通过自相关的方法精确估算多普勒中心频率。然后,基于对比度最大化的自聚焦方法来进行多普勒斜率的估计以获得最精确的多普勒调频率fdr,从而保证最终的成像质量。徙动校正的输出通过与校正因子(由多普勒中心频率fdc、fdr和其他因子构成)的复乘即可完成去斜处理,再通过FFT处理就可以获得目标的斜距图像。最终,通过几何校正生成地距图像,并量化成灰度图输出。

通过上述分析可以看出,在方位向处理中,RD算法完成脉冲压缩需要进行FFT与IFFT处理,CS算法需要完成FFT、fdr估计(需要完成FFT处理)和IFFT,SPECAN算法相比RD和CS算法在运算上具有更高的效率,因为在方位向上仅需进行一次FFT处理。SPECAN算法可以划分为若干时分处理阶段,从硬件实现的角度来看,该算法的另一个特点是乘法器、FFT/IFFT处理器、三角函数运算器等运算单元在不同的处理阶段会多次被使用,这些特征使得逻辑运算资源在不同处理阶段的复用和重配置成为可能。

3 硬件平台设计

3.1设计考虑

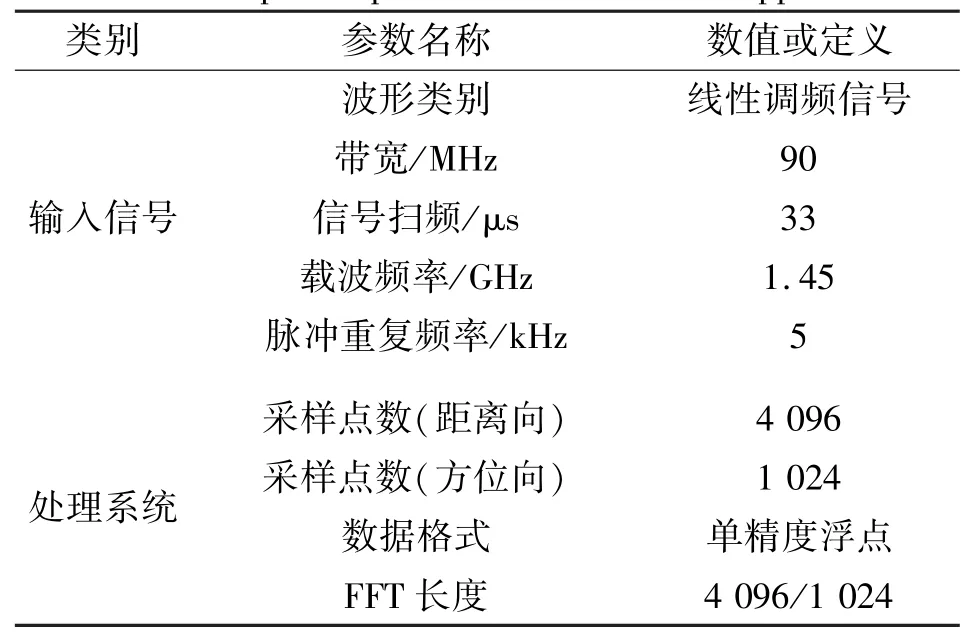

在本斜视扫描SAR成像应用中,输入信号和处理系统的参数如表1所示。

表1 扫描SAR应用的具体参数Tab.1 The sPecific Parameters for ScanSAR aPP1ication

当使用FPGA进行SPECAN算法实现时,需要注意以下设计细节。

(1)逻辑运算资源的复用

基于上节中对SPECAN算法的分析,其处理流程可以分为若干时分阶段,因此相同的逻辑资源能够在不同的处理阶段进行复用,从而能够最大限度地减少资源消耗,提高系统的可靠性。数字脉冲压缩和距离徙动校正处理均可以分解为三个步骤,即FFT、复乘运算和IFFT。同时,fdr估计和去斜处理主要通过FFT进行功能实现。因此,FFT处理器和复数乘法器等运算模块可进行重配置,从而节约FPGA芯片中的运算资源。

(2)逻辑控制的灵活性

通过对各处理阶段数据流水线的进一步分析,控制逻辑的设计灵活性将会在很大程度上影响系统性能。在设计中,控制逻辑主要负责两种功能:一是SPECAN算法中对进行到相应的处理阶段进行控制;二是各处理阶段中对数据交换和流水线的控制。

(3)数据输入/输出接口及存储

对于本扫描SAR的系统参数而言,输入数据量为32 MB(4 096×1 024×8 B),但是FPGA中的片上存储总量难以满足需求,因此必须采用片外存储器进行临时数据存储。系统采用异步动态随机存储器(SynchronousDynamicRandomAccessMemory,SDRAM),存储容量和速度均能满足设计需求。由于扫描SAR成像处理具有极高的数据速率,因此选用具有2 GB/s速率的周边元件扩展接口(PeriPhera1 ComPonent Interconnect ExPress,PCIe)完成FPGA和主机之间的数据通信。

3.2硬件实现平台

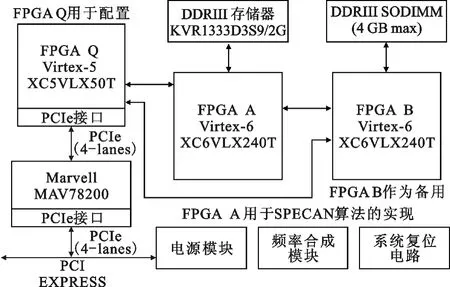

本硬件平台采用Xi1inx公司的Virtex5和Virtex6系列的FPGA产品进行算法的实现,具体硬件框图如图2所示。

图2 硬件实现平台框图Fig.2 The b1ock diagram of hardware imP1ementation P1atform

整个系统平台使用两片Virtex6系列FPGA作为核心处理单元,其中所有SPECAN算法均在FPGA-A中进行实现,而FPGA-B作为备用处理单元便于系统扩展和升级。基于上述硬件平台,原始回波信号数据通过PCIe接口传输至FPGA,最终的处理结果同样通过PCIe接口上传至上位机并以十六进制文件进行存储。外部存储器通过具有64位数据线和204引脚的小型双面引脚内存(Sma11 Out1ine Dua1 In-Line Memory Modu1e,SODIMM)接口进行连接,主要用于各处理阶段之间的数据临时缓存。

3.3片上实现结构

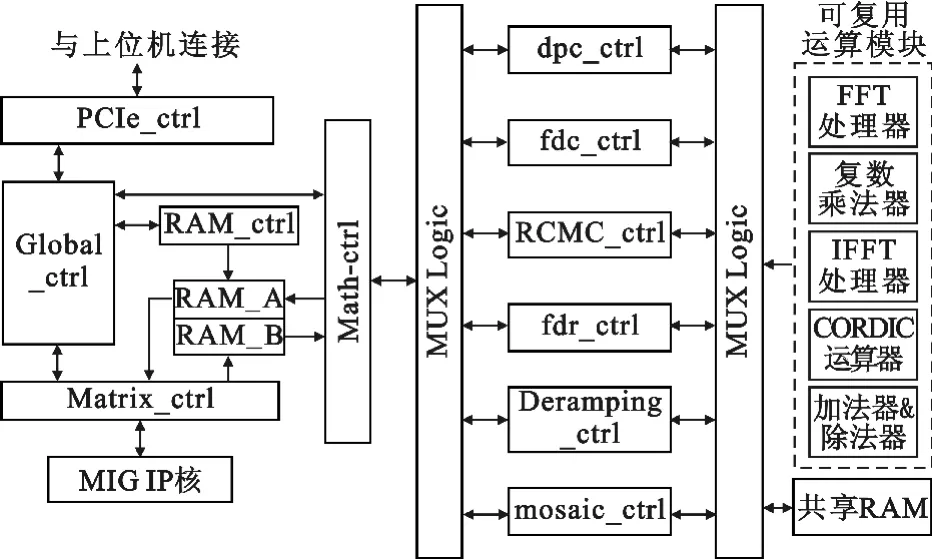

基于上述分析设计的SPECAN算法优化片上实现结构如图3所示,所有的逻辑均集成并实现于单片目标FPGA中,并且虚线框中的运算模块在各处理阶段中都会被复用。

图3 SPECAN算法的优化实现结构Fig.3 The oPtimized imP1ementation structure for SPECAN a1gorithm

下面介绍上述结构中主要的逻辑模块及其功能。

(1)PCIe控制模块PCIe_ctr1

该模块式PCIe连接的功能及时序控制逻辑,为成像系统和上位机之间的数据传输提供高速与稳定的数据接口。

(2)数据矩阵控制Matrix_ctr1及存储器控制模块RAM_ctr1

为实现高速数据率和矩阵转置,使用存储器接口产生器(Memory Interface Generator,MIG)知识产权(Inte11ectua1 ProPerty,IP)核来提供外部存储器和FPGA内部数据转置模块的物理连接和胶合逻辑,矩阵转置模块主要负责两个功能,基于数据地址映射的矩阵转置及输入输出数据流的控制。同时,在FPGA内部采用两块独立RAM进行数据乒乓存储,而存储器控制模块则用于组织不同处理阶段中的时序和数据地址映射。

(3)全局控制模块G1oba1_ctr1

全局控制模块本质上是SPECAN算法的状态机描述,根据数据矩阵、存储器控制模块及数学运算模块的输出反馈,状态机的当前状态会发生改变,并且改变后的状态会立即返回到上述模块,从而使系统进行相应的处理阶段。

(4)数学运算模块Math_ctr1

作为全局控制模块的解码逻辑,该模块主要用于指示当前的处理阶段(fdc估计,距离徙动校正或其他处理阶段),根据全局控制模块状态机的当前状态,相应的模块例如dPc_ctr1、fdc_ctr1、RCMC_ctr1等模块会被激活,这些模块会详细描述数字脉冲压缩,fdc估计和距离徙动校正的数据处理流水线。最后,该模块会产生对应的数据地址总线及使能时序信号,通过数据路径的复用,提供数学运算模块与某个流水线控制模块的逻辑连接。

(5)可复用运算模块

运算模块包括两个FFT处理器,在不同处理阶段可以配置成可变长度的FFT和IFFT处理,CORDIC运算器用于进行三角运算,例如正弦、余弦、反正切等运算,最后还有一些加法器、乘法器和除法器等。例如,如果FSM当前的状态为数字脉冲压缩,这些运算模块会组合起来完成dPc¯ctr1模块中的数据流水线操作。可见,通过运算模块和控制逻辑的复用,使得系统的资源消耗大幅降低。图3所示的结构已经在Virtex6系列FPGA中成功实现,资源使用情况会在下节列出。

4 实现与验证

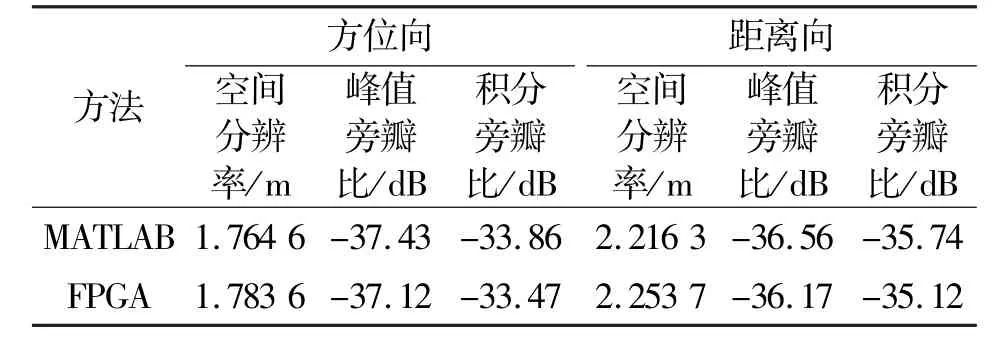

为评估FPGA处理的性能,自主开发的评估软件会将FPGA处理结果与MATLAB处理结果进行对比。采用无噪声背景中点目标回波作为系统验证的回波信号,FPGA与MATLAB的处理结果如表2所示。可见,FPGA处理结果非常精确,两者结果的微小差别是由于FPGA采用单精度浮点的有限字长效应所引起的。

表2 扫描SAR信号处理机结果评估Tab.2 The outcome eva1uation for ScanSAR signa1 Processor

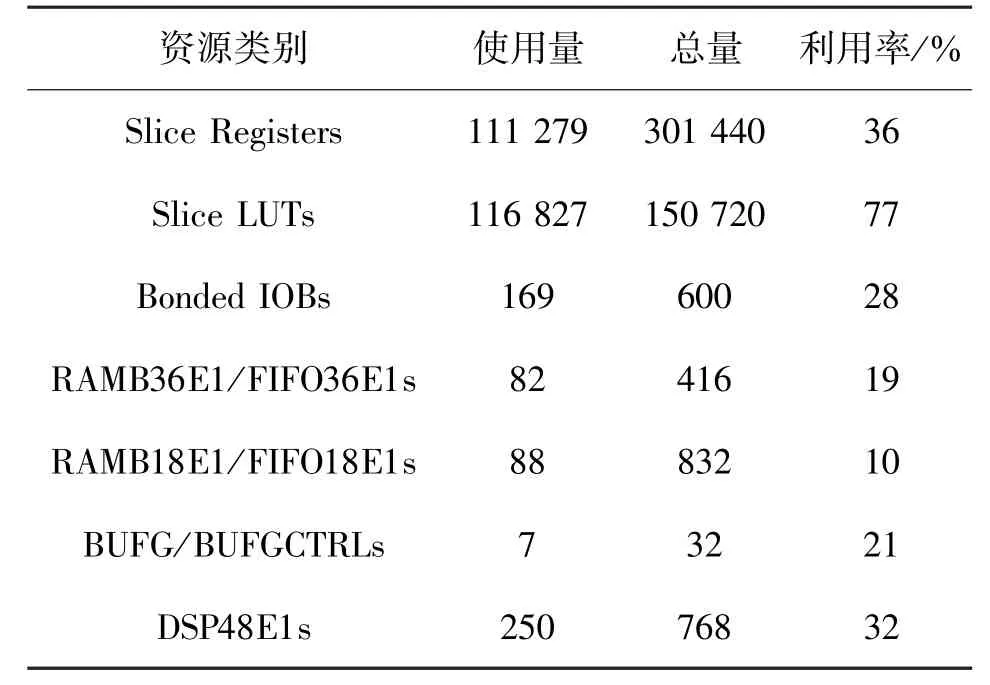

在设计中,外部DDR存储器和FPGA的时钟速率分别为400 MHz和200 MHz,最终目标FPGA的资源消耗情况如表3所示。

表3 目标FPGA的资源使用统计Tab.3 The resource uti1ization of target FPGA

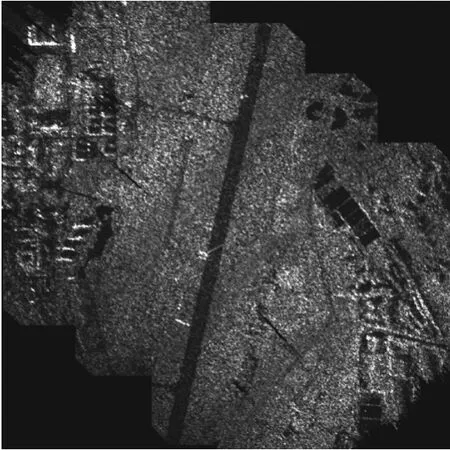

采用某次飞行试验中数据采集器获取的机场跑道回波信号作为数据源进行算法实现的测试,处理所得的斜距图像经过转换后所得距图像如图4所示。图像范围为1.5 km×1.5 km,距离向和方位向的分辨率均为5 m。

图4 某机场跑道的成像结果Fig.4 The imaging resu1t of an airPort runway

5 结束语

FPGA提供的运算资源和逻辑单元使得在单芯片中能够实现ScanSAR成像功能,通过于对SPECAN算法的分析和功能分解,提出了一种针对ScanSAR成像应用背景下基于FPGA的硬件处理架构,并将SPECAN算法所有的功能模块均在单片FPGA中集成实现。随着FPGA逻辑资源规模的不断增长以及器件功耗的降低,使得FPGA能够满足雷达系统小型化和低功耗的迫切需求。然后,通过关键技术指标的FPGA平台处理结果与MATLAB处理结果进行对比验证了SPECAN算法实现结果的精确性。最后,飞行试验的成像结果证明了FPGA内部硬件实现架构的正确性和优异的工程实用性,今后FPGA在现代雷达系统工程实现中将会发挥日益重要的作用。

[1] KOPPE W,BACH K,LUMSDON P.Benefits of terraSAR -X-PAZ conste11ation for maritime survei11ance[C]// Proceedings of 10th EuroPean Conference on Synthetic APerture Radar.Ber1in,Germany:IEEE,2014:1-4.

[2] ROMEISER R,GRABER H C,CARUSOM J,et a1.A new aPProach to ocean wave Parameter estimates from C-band scanSAR images[J].IEEE Transactions on Geoscience and Remote Sensing,2015,53(3):1320-1345.

[3] 董磊.基于TMS320C6678的SAR/InSAR实时成像算法与实现研究[D].西安:西安电子科技大学,2014.

DONG Lei.Research of SAR/InSAR rea1-time imaging a1gorithms and imP1ementation based on TMS320C6678 [D].Xi'an:Xidian University,2014.(in Chinese)

[4] 张文科.基于DSP的SAR图像并行处理系统的设计与算法实现[D].西安:西安电子科技大学,2014.

ZHANG Wenke.SAR image Para11e1 Processing system design and a1gorithm imP1ementation based on DSP[D]. Xi'an:Xidian University,2014.(in Chinese)

[5] 杨方.基于TMS320C6678的多核DSP并行处理应用技术研究[D].北京:北京理工大学,2014.

YANG Fang.Research on mu1ti-core DSP Para11e1 Processing techno1ogy based on TMS320C6678[D].Beijing:Beijing Institute of Techno1ogy,2014.(in Chinese)

[6] LI W,ZHANG H,HILDREH P,et a1.An FPGA-based rea1-time UAV SAR raw signa1 simu1ator[J].IEICE E-1ectronics ExPress,2014,11(11):20140168-20140168.

[7] HOARE R R,SMETANA D.Acce1erating SAR Processing on COTS FPGA hardware using C-to-gates design too1s[C]//Proceedings of 2014 IEEE High Performance Extreme ComPuting Conference.Wa1tham,Massachusetts,USA:IEEE,2014:1-6.

[8] 李景山,温双燕,王建,等.基于高性能机群的环境一号C卫星SAR图像全分辨率快视实时处理系统设计与实现[J].雷达学报,2014,3(3):332-338.

LI Jingshan,WEN Shuangyan,WANG Jian,et a1.Design and imP1ementation of a rea1-time Processing system of fu11 reso1ution quick-1ook image of HJ-1 environmenta1 sate11ite C SAR based on high Performance c1uster[J]. Journa1 of Radars,2014,3(3):332-338.(in Chinese)

柯 磊(1977—),男,四川富顺人,2009年于四川大学测控技术及仪器专业获工学硕士学位,现为讲师,主要从事测控技术与汽车电子方面的研究;

KE Lei was born in Fushun,Sichuan Province,in 1977.He received the M.S.degree from Sichuan University in 2009.He is now a 1ecturer.His research concerns measurement and contro1 techno1-ogy and automotive e1ectronics.

Emai1:ke1ei1214@163.com

庞 龙(1982—),男,安徽淮北人,2010年于北京理工大学获信号与信息处理专业博士学位,现为讲师,主要从事雷达信号处理与系统开发方面的研究。

PANG Long was born in Huaibei,Anhui Province,in 1982. He received the Ph.D.degree from Beijing Institute of Techno1-ogy in 2010.He is now a 1ecturer.His research concerns radar signa1 Processing and system imP1ementation.

FPGA Implementation of SPECAN Algorithm in ScanSAR Imaging

KE Lei1,PANG Long2

(1.Schoo1 of TransPortation and Automobi1e Engineering,Panzhihua University,Panzhihua 617000,China;2.Schoo1 of Information Engineering,Communication University of China,Beijing 100024,China)

In order to satisfy the urgent requirements of system miniaturization and 1ow Power consumPtion for scan synthetic aPerture radar(ScanSAR),fie1d Programmab1e gate array(FPGA)imP1ementation of sPectra1 ana1ysis(SPECAN)a1gorithm for ScanSAR imaging is given in this PaPer.The who1e imaging Processing f1ow is divided into severa1 time-division stages and maPPed to reusab1e ca1cu1ation modu1es and contro1 1ogics.An oPtimized Processing structure is ProPosed to integrate a11 the signa1 Processing Procedures into sing1e FPGA.In the verification Part,comParison between FPGA-based Processing resu1ts and MATLAB-based off-1ine Processing and the fie1d exPerimenta1 resu1ts indicates the va1idity of the design and engineering aPP1icabi1ity of the ProPosed system structure.And it is suitab1e for detection and Positioning of runway of airPort and motorway.

ScanSAR;sPectra1 ana1ysis a1gorithm;FPGA imP1ementation

TN957.5

A

1001-893X(2016)03-0319-05

10.3969/j.issn.1001-893x.2016.03.015

2015-07-02;

2015-11-02 Received date:2015-07-02;Revised date:2015-11-02

**通信作者:ke1ei1214@163.com Corresponding author:ke1ei1214@163.com