基于SoC FPGA的中频数字接收机设计与实现*

刘 丹 龚晓峰

(四川大学电气信息学院 成都 610000)

基于SoC FPGA的中频数字接收机设计与实现*

刘丹龚晓峰

(四川大学电气信息学院成都610000)

为实现车载式接收机小型化、低功耗的要求,基于Altera公司SoC架构Cyclone V系列芯片,采用软硬件协同的设计方法,完成了宽带中频数字接收机的设计。该设计集成A/D芯片、DDR3存储芯片、GPS芯片等外围电路,在FPGA部分实现了中频信号扫频、单包或连续采集、数字下变频、频谱分析,在ARM处理器部分搭建了Linux操作系统,实现了ITU参数测量、音频解调、场强计算等功能,FPGA与ARM之间采用AXI总线传输数据,实测传输速率达到7.2Gb/s,保证了数据的连续性与实时性。

SoC; FPGA; HPS; 数字中频接收机

Class NumberTN92

1 引言

目前数字中频接收机在频谱管理、卫星通信等领域有着广泛的应用。要达到实时的数字信号处理要求,需要处理器具备较高的数据带宽和处理速度,这对于单FPGA、单DSP或x86架构CPU来说都不容易实现,而FPGA+DSP或FPGA+x86的方案则无可避免地导致电路面积增大、功耗上升[1]。为此,本设计提出一种采用Altera公司的Cyclone V SoC系列芯片完成中频接收机的方案。该系列的芯片优势在于它在FPGA架构中集成了基于ARM的硬核处理器系统(HPS),包括双核ARM Cortex-A9处理器、外设和存储器接口,采用了TSMC的28nm低功耗(28LP)工艺进行开发。HPS和FPGA架构之间的大吞吐量数据通路实现了双芯片解决方案无法提供的互联性能。处理器和FPGA之间没有了外部I/O通路,大幅度降低了系统功耗。该芯片同时实现了硬核知识产权(IP)的性能和低功耗特性,以及可编程逻辑的灵活性,非常适合手持式、车载式数字中频接收机的实现。

2 接收机硬件设计

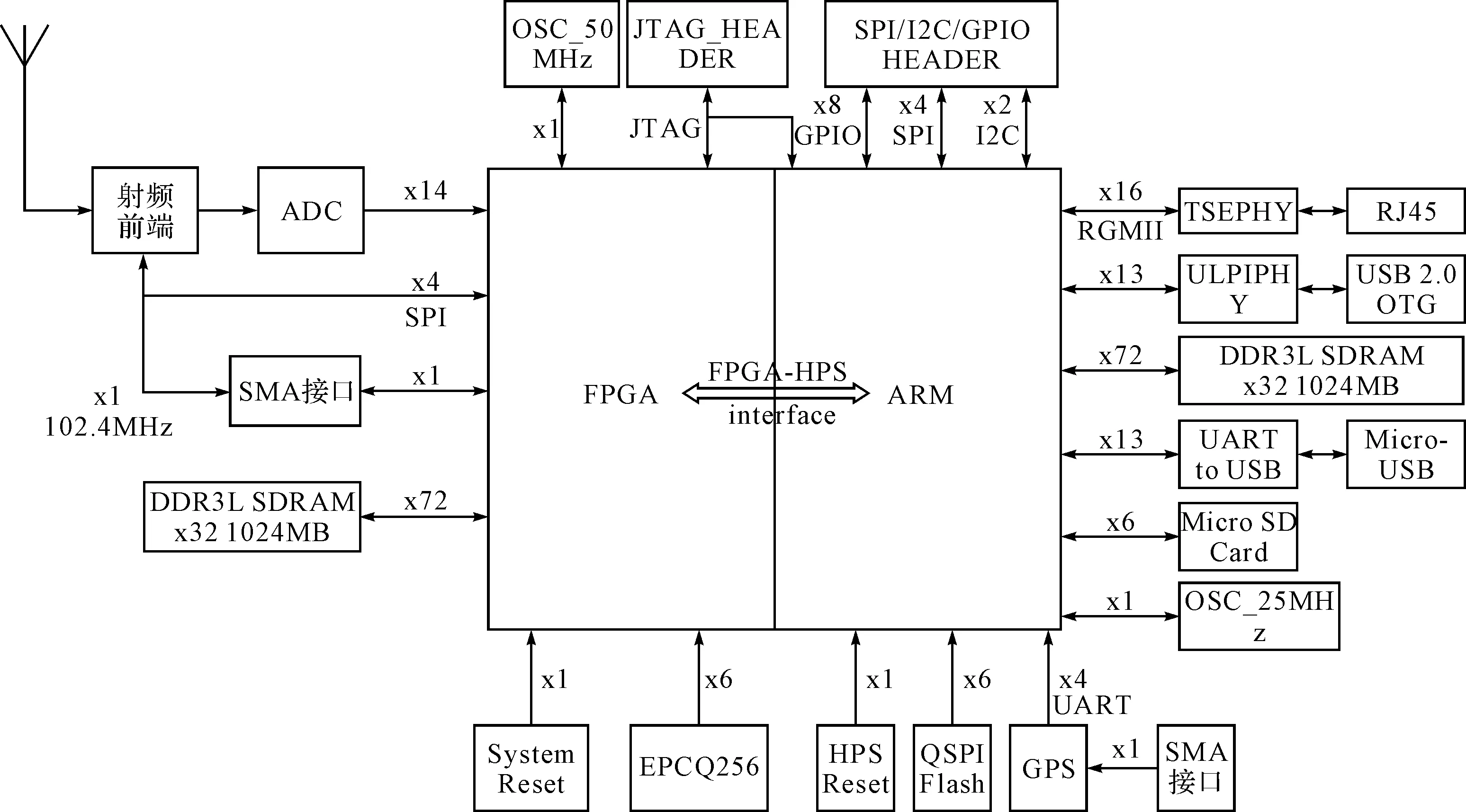

该中频数字接收机的硬件设计总体框图如图1所示,天线接收20MHz~8000MHz全频段射频信号至射频前端,射频前端将射频信号模拟下变频至中频后输入至中频数字接收机。接收机ADC模块采用LINEAR公司的14bit A/D芯片LTC2207[2],中频信号固定为76.8MHz,最大信号带宽为40MHz,根据带通采样定理,AD采样速率确定为102.4MHz[3]。

FPGA的配置数据存储在SRAM单元中,由于SRAM是易失性的存储器,掉电后编程信息立即丢失,因此为了保证FPGA在重新上电后,能自动加载配置数据,在该设计中通过Altera公司专用的FPGA配置芯片EPCQ系列存储器,以主动串行模式(AS)对SRAM进行配置[4]。另外还在FPGA端配置了1GB的DDR3 SDRAM,以用作数据的缓存。

在HPS(Hard Processor System)端中,核心为ARM Cortex-A9 双核处理器,外设包括1GB DDR3 SDRAM、网口[5]、GPS模块、SD卡槽、USB 2.0接口、Flash、SPI接口槽、I2C接口槽。

3 FPGA固件设计

接收机需实现三种工作模式:扫频模式、单包采集模式、连续采集模式。扫频模式类似于频谱仪的扫频,自动切换相邻频点,通过频点与采集带宽的配合实现全频段信号的扫描。单包采集模式应用于采集大带宽信号时,缓存一大段数据量后上传分析。连续采集模式应用于采集小带宽信号时,如FM解调等功能,实现数据的不间断上传分析。三种模式的调度都由主控模块完成。

图1 接收机硬件设计框图

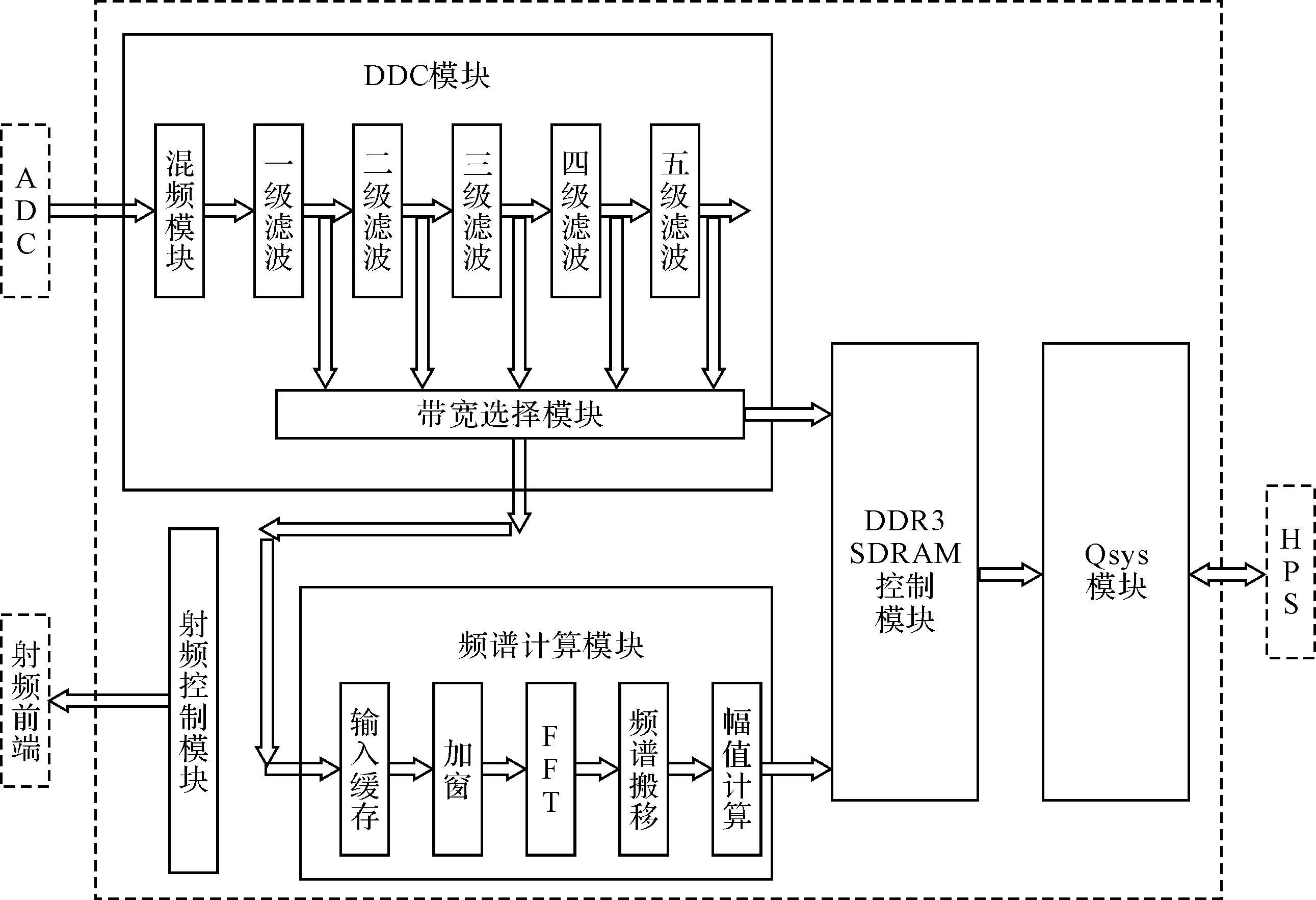

图2 FPGA固件设计框图

FPGA固件结构框图如图2所示,主要包括射频控制模块、DDC模块、频谱计算模块、SDRAM控制模块、Qsys模块。射频控制模块通过SPI协议控制射频前端工作。DDC模块完成对数字中频信号的下变频处理,得到零中频IQ信号。IQ信号输入至频谱计算模块进行频谱分析,得到信号的频谱幅值数据。最后把IQ信号与频谱数据缓存至SDRAM中,由ARM控制是否上传数据。SDRAM控制模块主要包括DDR3 SDRAM Controller with UniPHY核及Avalon_MM协议实现。Qsys模块作为与HPS端交互接口模块,实现了FPGA与HPS交互的AXI协议。

3.1数字下变频模块(DDC)

实信号的频谱具有共轭对称性,所以对于一个实信号,只需由其正频部分就能完全加以描述,不会丢失任何信息。由数字信号正交变换理论可知,一个实信号x(t)的正频率分量所对应的信号z(t)是一个复信号,其实部为原信号x(t),而其虚部为原信号x(t)的Hilbert变换。若一个实的窄带信号表示为

x(t)=a(t)·cos[ω0t+θ(t)]

(1)

那么该窄带信号的正频部分的解析表示为

z(t)=a(t)·cos[ω0t+θ(t)]+

ja(t)·sin[ω0t+θ(t)]

(2)

用极坐标形式可表示为

z(t)=a(t)·ej[ω0t+θ(t))]=a(t)·ejθ(t)·ejω0t

(3)

式中,ejω0t称为信号的载频分量,它作为信息载体不含有用信息。将式(3)乘以e-jω0t,把载频下移ω0,变成零载频,其结果称为零中频信号,即有:

zB(t)=a(t)·ejθ(t)

=a(t)·cosθ(t)+ja(t)·sinθ(t)

=zBI(t)+jzBQ(t)

(4)

zBI(t)、zBQ(T)分别称为零中频信号的同相分量和正交分量。零中频信号可以完整的表示原始的实的窄带信号x(t)。

模拟信号x(t)经过AD变换后,得到数字信号:

x(n)=a(n)·cos[ω0n+θ(n)]

(5)

该信号的有用信息也可以由其零中频信号获得,将其展开有:

x(n)=zBI(n)·cos(ω0n)-zBQ(n)sin(ω0n)

(6)

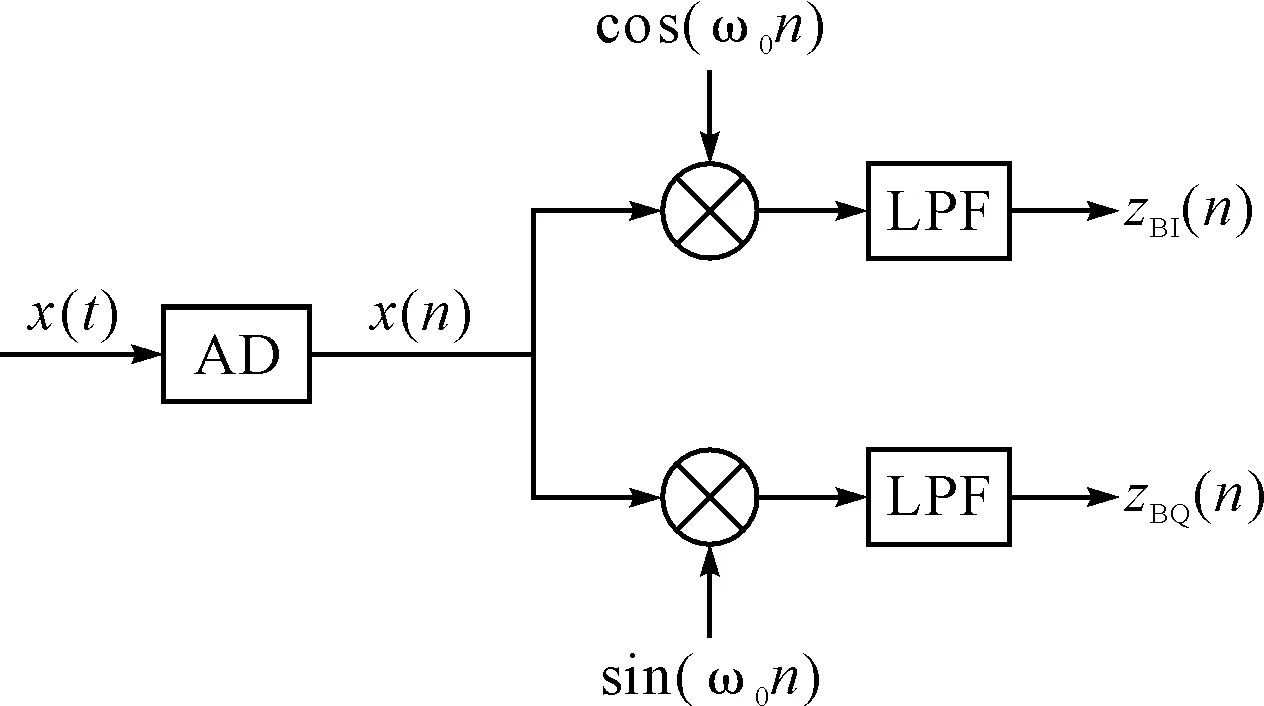

zBI(n)、zBQ(n)分别为零中频信号的同相分量和正交分量,cos(ω0n)、sin(ω0n)为载频分量,与本振信号cos(ω0n)、sin(ω0n)混频后,经过低通滤波器即可提取出zBI(n)、zBQ(n),如图3所示。

DDC模块主要分为数字混频模块与滤波器模块。设计要求混频精度需达到1KHz,若用查表法的话需耗费大量的存储资源,因此采用CORDIC算法实现[6]。

图3 数字混频正交变换

滤波器模块需支持带宽1KHz~40MHz共18种滤波带宽的数字低通滤波器,且需要根据滤波带宽降低信号速率,也即需要滤波的同时对信号进行抽取。由于需要进行18种不同滤波带宽的滤波,因此不采用IP核完成滤波的方案,而是采用复用乘、加法器完成FIR滤波器的方案。把18种滤波带宽分为8组,每组完成两到三种滤波带宽,把滤波因子存入ROM表中,通过地址的切换进行滤波带宽的切换,每级滤波的同时通过抽取降低信号速率。

3.2频谱计算模块

频谱计算模块主要完成对DDC模块输出的零中频信号的频谱幅值的绘制。由于不同滤波带宽的信号速率不一致,因此在频谱计算模块输入端加入FIFO缓存。在FFT分析中为减少频谱泄露的影响,采用不同的窗函数对信号进行截取,不同的窗函数产生泄露能量的大小不一样,频率分辨能力也不一样,为此提供了四种窗函数进行选择:汉明窗、汉宁窗、Kaiser窗、Blackman窗[7]。复数FFT运算由IP核完成,为节省资源,数据流模式选用Buffered Burst模式,FFT长度为2048点,处理结构为Quad Output,一个并行FFT引擎,这种配置方案可以保证支持所有信号速率下连续频谱的计算[8]。FFT核得出的频谱数据与频率并不是对应的,需要通过频谱搬移模块把DC分量移至频谱中心,要做的就是把FFT计算后的序列前半部分与后半部分对调。

由于无线通信信号的动态范围相当大,大信号相对于小信号的功率,甚至能达到几百万倍。因此为方便表示与计算,信号功率、幅值通常不再利用其绝对数值表示,而采用对数形式。幅值计算公式如下:

(7)

式中,A为频谱幅值;R、I分别为FFT后数据实部、虚部;N为采样点数。

3.3DDR3 SDRAM控制器

Cyclone V器件采用了专用的硬核存储控制器(HMC),与传统使用内核逻辑实现的存储控制器相比,硬核存储控制器效率更高、延时与功耗更小。普通的DRAM存储器接口效率通常在70%左右,而Altera的硬核存储控制器的效率可高达92%。而且将传统的软核控制器固化为硬核,不仅节省了系统功耗,还通过减少信号链路长度、降低HMC电路电容,从而降低了电路的总体动态功耗[9]。

在例化SDRAM控制器IP核时,需要勾选Enable Hard_EMIF,工作在全速模式(Full-rate)下。最后硬核存储控制器对比软核存储控制器的耗费资源节省了四分之三。

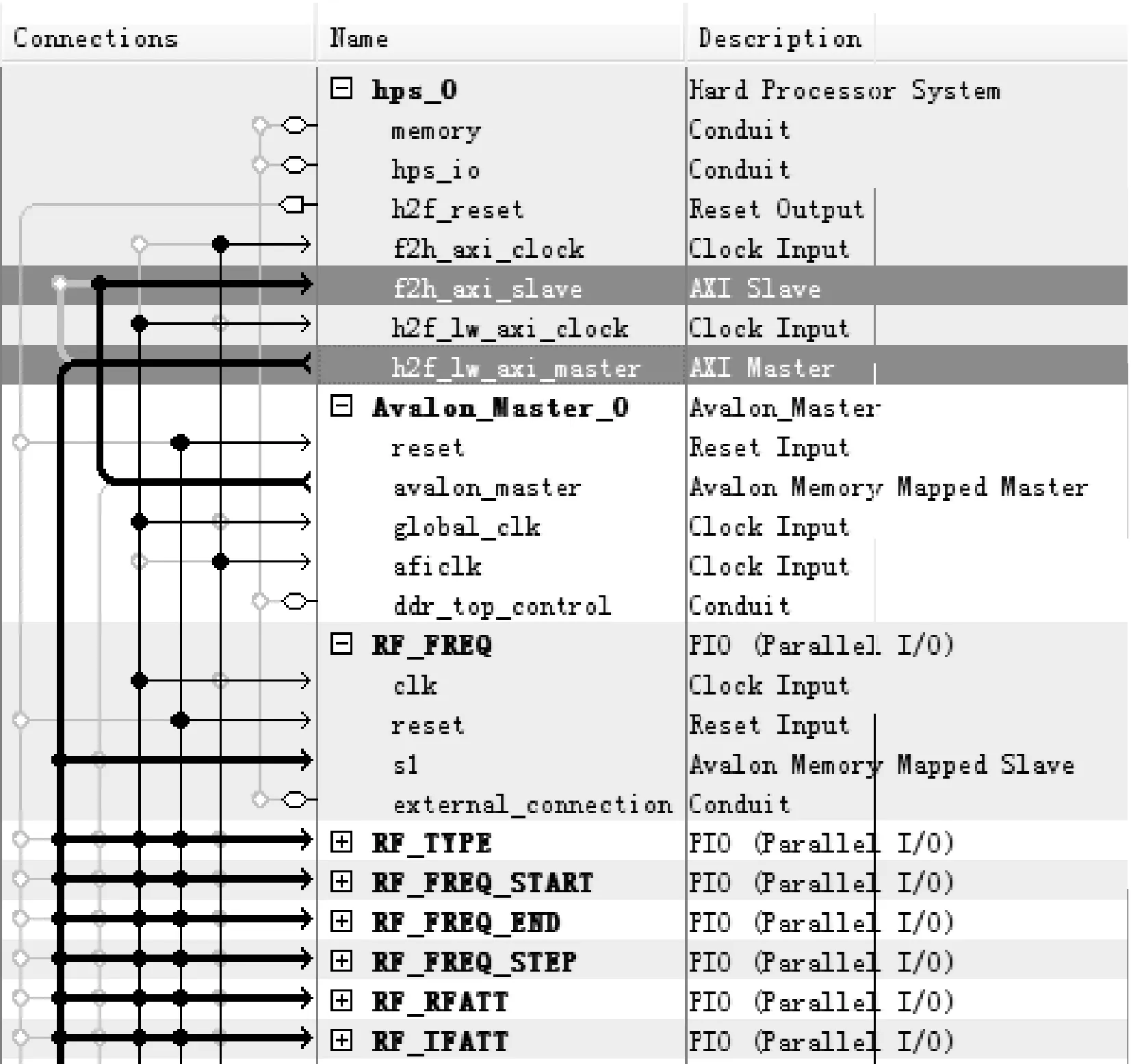

3.4Qsys系统

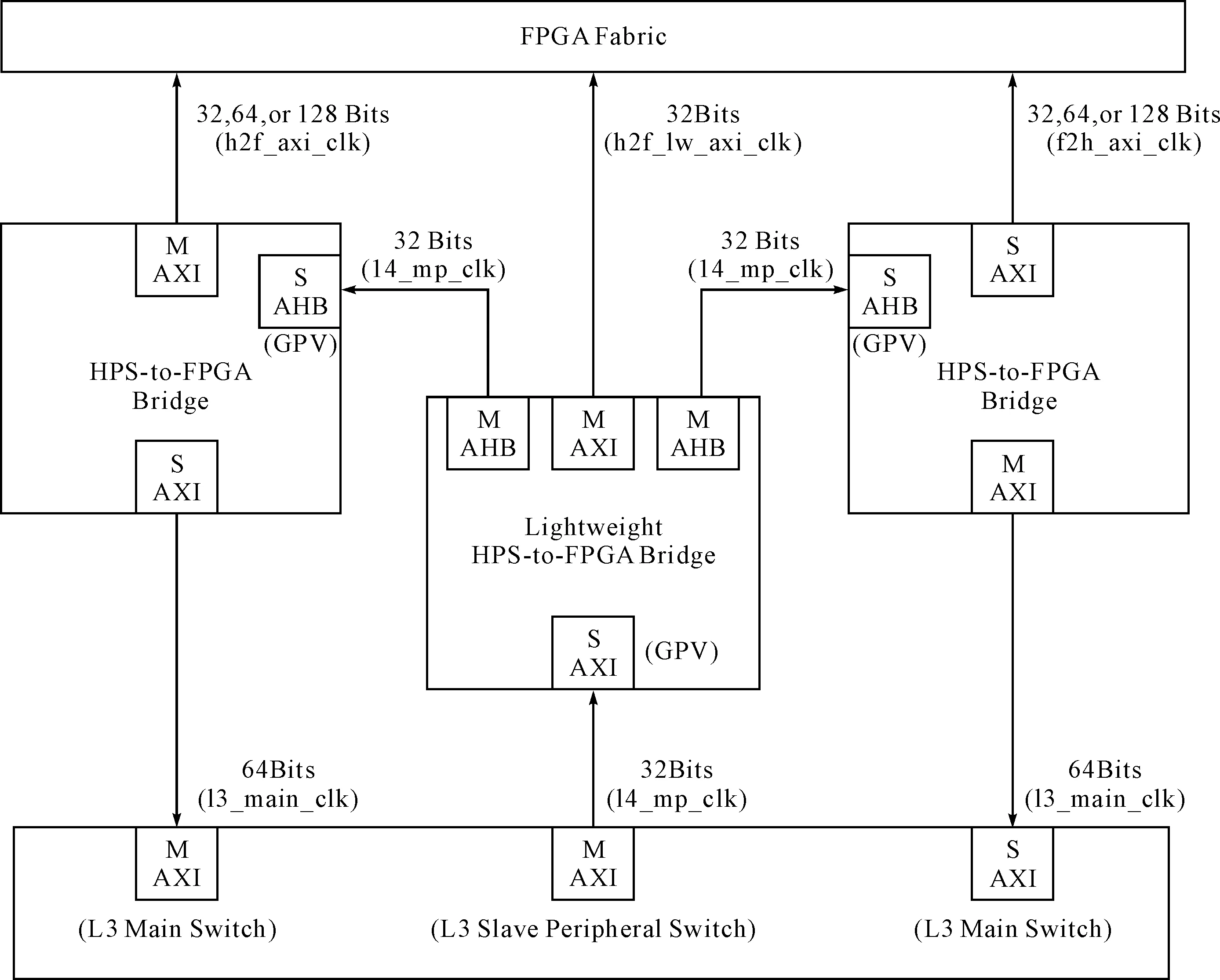

为实现FPGA与HPS之间的存储器共享和数据传输,Altera SoC FPGA提供了两种方式用于FPGA和HPS通信。他们是FPGA to SDRAM和AXI bridge接口。FPGA to SDRAM 接口是HPS内部的SDRAM控制器提供给FPGA访问HPS内存的接口。AXI bridge是FPGA和HPS总线之间数据交互的接口,包括FPGA-to-HPS Bridge、HPS-to-FPGA Bridge和Light-weight HPS-to-FPGA Bridge[10]。

图4 HMC简图

图5 AXI桥

在本设计中IQ信号数据与频谱数据通过FPGA-to-HPS AXI bridge传输,各模块参数、状态通过Light-weight HPS-to-FPGA Bridge传输。AXI Bridge 在HPS端使用的是AMBA AXI协议,用户在FPGA逻辑设计时可以使用AXI协议与HPS通信。另外Qsys接口也实现了AXI协议到Avalon-MM协议的自动转换,所以用户可以在Qsys中实现Avalon-MM接口与AXI Bridge的IP直接互连[11]。

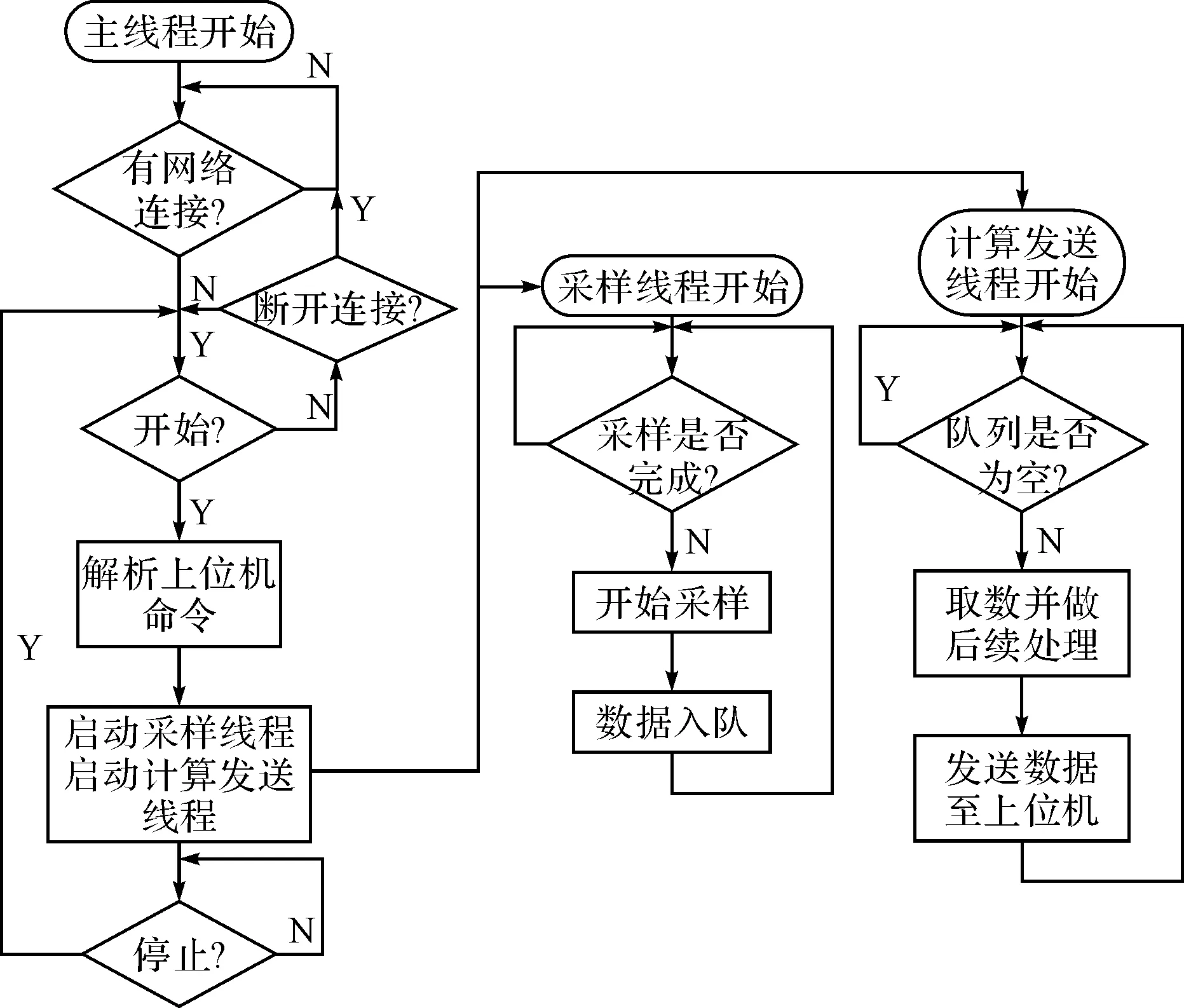

4 HPS软件设计

HPS端通过以太网与上位机交互,接收上位机命令,解析后通过Light-weight HPS-to-FPGA Bridge传送相应指令给FPGA;并根据FPGA回传状态,读取IQ、频谱数据,实现后续计算如ITU测量、音频解调,最终再把数据打包通过以太网送至上位机。ARM端程序分为三个线程:主线程、采集线程和计算发送线程。主线程负责接收并处理上位机命令,采样线程负责与FPGA交互,采样IQ与频谱数据,计算发送线程负责对所取得的数据进行后续处理并打包发送。

图6 Qsys AXI 连线图

图7 线程工作流程图

5 接收机运行及测试

测试在数字中频板上进行,搭建监测环境,连接信号源、射频前端、中频板、上位机。中频板实物如图8所示。

图8 数字中频板

上位机软件工作界面如图9所示,分别显示了频谱、IQ信号、IQ星座图、场强图。

图9 上位机软件

6 结语

本文基于软件无线电的思想与原理,着眼于实现小面积、低功耗的要求,采用Altera 公司的SoC FPGA,设计了一个宽带中频数字接收机。既具有传统FPGA硬件可编程、数据吞吐率高的优势,又能使用双核ARM Cortex-A9处理器执行复杂的信号处理算法。其适用于高性能、低成本、低功耗、对电路面积敏感的工业应用与无线电领域的应用。

[1] 何鹏,郝绍杰.基于片上系统的电磁频谱监测接收机设计[J].电子质量,2014(4):80-83.

HE Peng,Hao Shaojie. The Design of Electromagnetic Spectrum Monitoring Receiver Based on SOPC[J].Electronics Quality,2014(4):80-83.

[2] 吴丽丽.LTC2207在ARM与FPGA控制下的采集应用[J].单片机与嵌入式系统应用,2011,11(12):40-43.

WU Lili. Acquisition Application of LT02207 under Control of ARM and FPGA[J]. Microcontrollers & Embedded Systems,2011,11(12):40-43.

[3] 李琛.ADC的前端设计[J].电子质量,2014(5):33-35.

LI Chen. The Design of ADC Front-end[J]. Electronics Quality,2014(5):33-35.

[4] 王灵芝,林培杰,黄春晖.FPGA的配置及其接口电路的设计[J].电子测量与仪器学报,2007,21(2):109-112.

WANG Lingzhi,LIN Peijie, HUANG Chunhui.Configuration of FPGA and Design of Its Interface Circuit[J]. Journal of Electronic Measurement and Instrument,2007,21(2):109-112.

[5] 杨新华,王用玺,刘欣.基于FPGA的以太网高速数据传输系统的设计[J].仪表技术与传感器,2013(12):80-83.

YANG Xinhua, WANG Yongxi, LIU Xin. Design of Ethernet High-speed Data Transmission System Based on FPGA[J]. Instrument Technique and Sensor,2013(12):80-83.

[6] 张红涛,宁晋哲,慈国辉.基于FPGA的数字下变频器的设计[J].现代电子技术,2014(15):73-75.

ZHANG Hongtao, NING Jinzhe, CI Guo-hui. Design of digital downconverter based on FPGA[J]. Modern Electronics Technique.2014(15):73-75.

[7] 杨文兴,杨俊智,周强.窗函数的选择对时频域测试分析的影响[J].新技术新工艺,2014(3):101-102,103.

YANG Wenxing, YANG Junzhi, ZHOU Qiang. Influence Analysis of Time-frequency Window Function Selection Test[J]. New Technology & New Process,2014(3):101-102,103.

[8] 窦秀梅,赵振纲.基于IP核的FPGA FFT算法模块的设计与实现[J].无线电工程,2008,38(8):29-31.

DOU Xiumei, ZHAO Zhengang. Design and Implementation of FPGA FFT Algorithm Module Based on IP Core[J]. Radio Engineering of China,2008,38(8):29-31.

[9] 刘春雅.Cyclone V FPGA在高带宽存储接口中的应用[J]. 电子设计工程,2014,22(10):97-99.

LIU Chunya. High-bandwidth memory interface application based on cyclone V FPGA[J]. Electronic Design Engineering,2014,22(10):97-99.

[10] 杨晓安,罗杰,包文博.基于Xilinx Zynq的物距测量系统设计与实现[J].现代电子技术,2014(15):123-126.

YANG Xiaoan, LUO Jie, BAO WenBo. Design and implementation of an object distance measurement system based on Xilinx Zynq[J]. Modern Electronics Technique,2014(15):123-126.

[11] 钱俊,符意德,逯沛龙.双目视觉的图像采集模块设计[J].计算机与数字工程,2015,43(4):725-728.

QIAN Jun, FU Yide, LU Peilong. Design of Image Acquisition Module of Binocular Vision[J]. Computer and Digital Engineering,2015, 43(4):725-728.

Design and Realization of the IF Digital Receiver Based on SoC FPGA

LIU DanGONG Xiaofeng

(College of Electric Information, Sichuan University, Chengdu610000)

In order to reduce the volume of broadband IF receiver, a design based on Altera SoC architecture Cyclone V series chips is put forward. This design realizes through the method of software and hardware coordination. Circuit design integrates DDR3 memory chip, GPS chip and other peripheral circuits. In the part of FPGA, the scan, single package or continue sampling of IF signal, DDC, spectrum analysis are realized. In the part of ARM, ITU parameter measurement, audio demodulation, field density calculation and so on in Linux system are realized. The FPGA and ARM integrate on SoC transmit data by AXI bus, data rate between them reaches 7.2Gb/s. Therefore, it ensures the continuity and real-time of data.

SoC, field programmable gate array, hard processor system, digital intermediate frequency receiver

2016年3月10日,

2016年4月28日

刘丹,男,硕士研究生,研究方向:无线电频谱监测。龚晓峰,男,教授,硕士生导师,研究方向:检测技术与自动化装置、无线电监测。

TN92DOI:10.3969/j.issn.1672-9722.2016.09.044