一种改善器件性能的Halo工艺

徐 政,李红征,赵文彬

一种改善器件性能的Halo工艺

徐 政,李红征,赵文彬

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

短沟效应是MOS器件特征尺寸缩小面对的关键挑战之一。Halo结构能够有效抑制短沟效应,合理的Halo区掺杂分布可以改善小尺寸器件性能。在对Halo注入条件进行优化的过程中,不仅考虑了Halo注入倾角和注入能量对器件常温特性和高低温特性的影响,还考虑到工艺波动,比较了多晶条宽变化对器件参数的影响。为了增加不同条件的可比性,以室温下的饱和电流作为基准,通过调节注入剂量,使不同Halo注入条件在室温下的饱和电流都相等。结果表明,对于130 nm多晶栅长,注入倾角60°,注入能量100 KeV时器件特性有最好的温度稳定性和工艺容宽。

Halo;短沟效应;离子注入;掺杂分布;多晶条宽

1 引言

随着集成度的不断提高,器件特征尺寸不断减小,出现了一系列新的物理效应和有待解决的问题。当沟长不断缩小时,栅压引起的沟道耗尽区与源衬、漏衬pn结引起的耗尽区发生重叠,导致阈值电压降低。在MOSFET沟道区的电场分布中,漏端电场很强,而源端电场较小,这种电场的不均匀分布,使得源端的低电场制约了电子速度,也就成为限制驱动电流的主要因素。另一方面,器件尺寸缩小,而电源电压基本保持不变,使栅氧化层垂直方向的电场迅速增加,沟道长度的缩小也使沟道区的横向电场增大,使热载流子效应变得严重,影响器件的可靠性,导致器件驱动电流减小,甚至最终使器件失效。针对这些问题,可以通过使用Halo结构,缓解电荷的共享问题,抑制短沟效应(SCE)和漏致势垒降低(DIBL)效应,提高栅控的能力[1]。

然而,Halo结构在改善SCE效应等问题的同时,还会出现反向短沟效应(RSCE),驱动电流降低,沟道区边缘的高掺杂会引起较大的BTBT(band-to-band tunneling)电流和GIDL(gate induced drain leakage)电流等。这些问题在很大程度上与Halo区的形状和掺杂分布有关,可以通过对Halo结构的优化来改善[2~3]。在优化Halo结构的研究过程中,工艺波动对参数的影响很大却往往被忽视。例如多晶条宽波动10%要比Halo注入剂量变化10%对器件参数的影响更大,并且在生产过程中,多晶条宽的波动幅度往往比注入工艺的波动幅度大。

因此,在评估Halo注入的效果时,还需要考虑器件参数随多晶条宽的变化,从而达到增加工艺容宽的目的。

2 器件结构

典型的对称Halo结构器件及其掺杂如图1所示,该结构同时包括了为克服HCE而采用的LDD结构。通过大角度倾斜注入与衬底相同类型的掺杂离子,在源/漏-衬底结附近形成Halo高掺杂区,该掺杂区能够有效降低泄漏电流。

图1 典型的NMOS Halo结构剖面及掺杂示意图

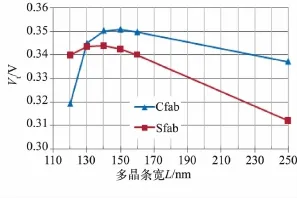

图2 使用Halo结构的Vt变化趋势

图2是2家fab在130 nm工艺节点阈值随沟长变化的对比。如图显示,沟长从130 nm变化到120 nm时,Sfab的阈值降低3.5mV,Cfab的阈值降低25.4mV。据此可以推断,在130 nm工艺节点,Sfab的参数稳定性优于Cfab。由此可见,合适的Halo注入条件可以增加工艺容宽,改善器件参数均匀性。

3 模拟分析和优化

对130 nm NMOS Halo结构,采用SILVACO工艺模拟软件ATHENA和器件模拟软件ATLAS分别进行了工艺和器件模拟。器件模拟中采用的模型有:载流子统计模型fermi、bgn,迁移率模型analytic、fldmob、cvt,复合模型srh、consrh、auger,隧道模型和载流子注入模型 fnord、hei,反型层表面退化模型nearflg,晶格加热模型lat.temp。栅介质使用SiO2,厚度2.9 nm。

进行工艺条件对比时,为了减小沟道杂质浓度对器件参数的影响,通过调整Halo注入剂量,使得不同注入条件在室温下的饱和电流相等,在此基础上比较Halo注入的倾角和能量对器件参数的影响。

对每个Halo注入条件,仿真了-55℃、25℃、125℃3个温度和110 nm、120 nm、130 nm、140 nm、150 nm 5种多晶栅长的饱和电流、泄漏电流、阈值。器件参数仿真的偏置条件如下:

Idsat∶Vg=Vd=1.2 V,Vs=Vsub=0;

Ioff∶Vds=1.2 V,Vg=Vs=Vsub=0;

Vt∶Vd=0.1 V,最大跨导法。通过比较器件参数的变化确定Halo注入的最佳倾角和能量。

3.1Halo注入倾角对器件参数的影响

4种工艺条件分别为:

Halo注入In,tilt=30°,energy=130 KeV,dose=4.0× 1013;

Halo注入In,tilt=45°,energy=130 KeV,dose=3.0× 1013;

Halo注入In,tilt=60°,energy=130 KeV,dose=3.6× 1013;

不做Halo注入,沟道注入In增加5.5×1012。

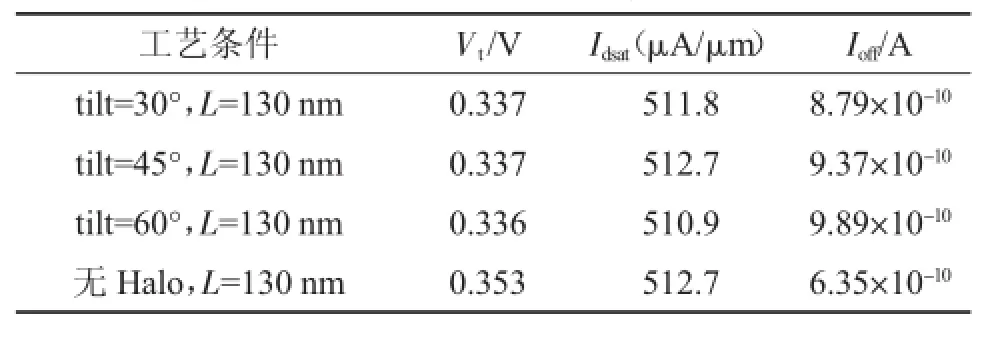

3.1.1常温器件参数

对于沟长130 nm的NMOS,通过调整Halo注入剂量,使不同工艺条件的室温Idsat近似相等,在512 μA左右。

表1 25℃NMOS器件参数

3.1.2器件参数的温度特性

图3 Idsat的温度特性

由图3可知,Idsat的温度特性对注入条件不敏感。

图4 Vt的温度特性

由图4可知,Vt的温度特性对注入条件不敏感。为了保持室温下各条件的Idsat一致,与其他条件相比,无Halo注入的阈值有差异,但是Idsat随温度变化的幅度差异不大。

图5 Ioff的温度特性

由图5可知,Ioff的温度特性对注入条件不敏感。

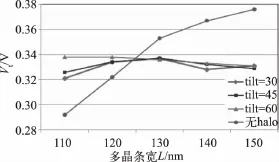

3.1.3器件参数的工艺敏感性

多晶条宽是工艺中的关键尺寸,条宽变化对器件特性影响很大[4]。为了考察工艺波动的影响,在其余条件不变的情况下,仅调整多晶条宽分别为110nm、120nm、 130 nm、140 nm、150 nm,比较不同注入条件下器件参数的变化。

从阈值、饱和电流、泄漏电流与栅长的关系看,未做Halo注入的参数变化最大,60°注入倾角的参数变化最小。

图6 阈值与多晶条宽的关系(25℃)

tilt=30°、45°、60°、无Halo注入4种条件下的阈值变化量分别为16 mV、11 mV、7 mV、84 mV。

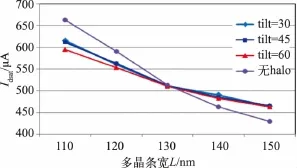

图7 饱和电流与多晶条宽的关系(25℃)

tilt=30°、45°、60°、无Halo注入4种条件的饱和电流变化幅度分别为32%、31%、29%、54%。

图8 泄漏电流与多晶条宽的关系(25℃)

tilt=30°、45°、60°、无Halo注入4种条件下的泄漏电流变化分别为22、20、15、236倍。

3.2Halo注入能量对器件参数的影响

对注入倾角60°,注入能量分别为100 KeV、130 KeV、160 KeV 3个条件,调整注入剂量,使各条件在25℃的Idsat近似相等。见表2。

3.2.1器件参数的温度特性

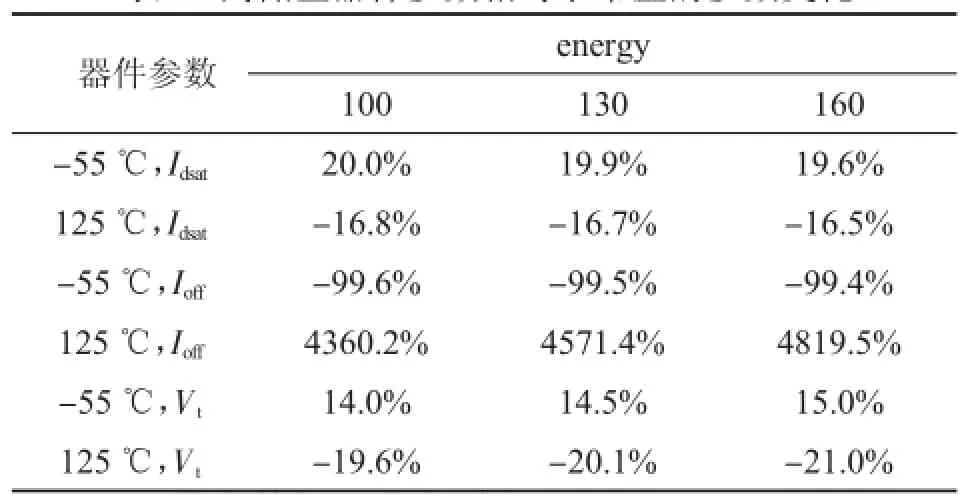

比较3种注入条件在-55℃、125℃相对室温的参数变化,3种注入条件之间的差别很小,详见表3。

表2 25℃NMOS器件参数

表3 高低温器件参数相对于常温的参数变化

3.2.2器件参数的工艺敏感性

为了考察工艺波动的影响,在其余条件不变的情况下,仅调整多晶条宽,分别为110nm、120nm、130nm、140 nm、150 nm,比较不同注入条件下器件参数的变化。

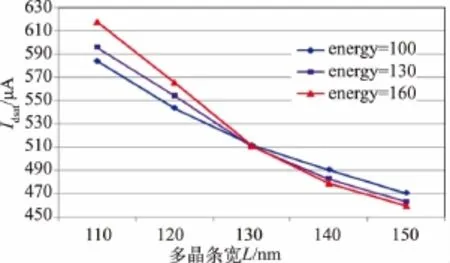

图9 阈值与多晶条宽的关系

能量为100 KeV、130 KeV、160 KeV 3种注入条件的阈值变化量分别为18 mV、7 mV、16 mV。

图10 饱和电流与多晶条宽的关系

能量为100 KeV、130 KeV、160 KeV 3种注入条件饱和电流变化幅度分别为24%、29%、34%。

能量为100 KeV、130 KeV、160 KeV 3种注入条件的泄漏电流变化分别为9、15、32倍。

图11 泄漏电流与多晶条宽的关系

从阈值、饱和电流、泄漏电流与栅长的关系看,100 KeV注入能量的参数变化最小。

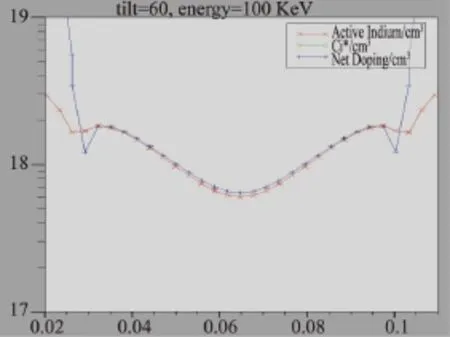

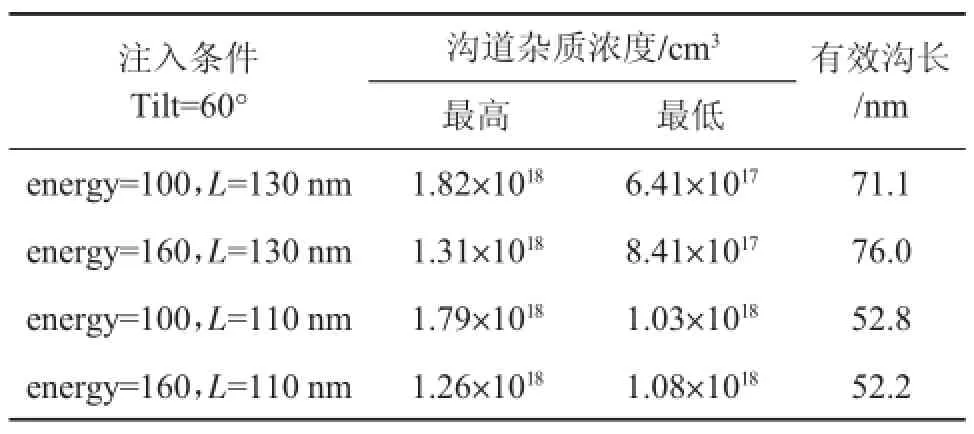

3.3沟道杂质分布比较

对器件参数随工艺条件不同产生的不同变化,从沟道杂质浓度分布来分析原因。

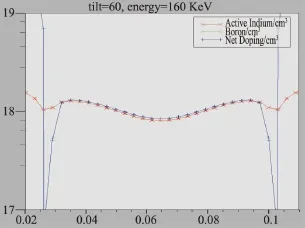

图12 L=130 nm、energy=160 KeV的沟道杂质分布

图13 L=130 nm、energy=100 KeV的沟道杂质分布

对图12、图13进行比较,不同注入条件在有效沟长、杂质分布上有区别。

表4 不同注入条件的沟道杂质分布对比

沟道杂质分布的差异造成了器件特性的差别,尤其体现在发生工艺波动(多晶沟长变化)时。

Halo注入使沟道杂质浓度不再是均匀分布,如果多晶条宽L较大,在靠近源漏结的沟道杂质浓度最高;如果L较小,多晶两侧的Halo注入在沟道中心叠加,使得杂质最高浓度出现在沟道中心。从表4的数据可以看出,多晶沟长减小时,沟道杂质浓度的最小值增加,最大值几乎不变。

不同注入条件比较的前提条件是在给定多晶条宽室温时的饱和电流相等,因此,不同注入条件在沟道中的杂质总量并不相等。从表4的数据可以看出,注入能量100 KeV比160 KeV的沟道杂质总量高,这是导致二者的器件参数随多晶条宽变化不同的根本原因。

4 结论

通过对不同Halo注入角度、注入能量的器件参数进行模拟,对仿真结果进行讨论分析,总结出工艺容宽大、适用于生产的Halo注入条件的一般建立方法。在多晶条宽和器件饱和电流、阈值、泄漏电流的约束条件下,提高靠近源漏结的沟道浓度,降低沟道中心浓度的杂质分布具有更大的工艺容宽。根据这个原则,对于多晶条宽从130 nm变到120 nm,优化Halo注入条件(In,tilt=60°,energy=100 KeV,dose=5×1013)的饱和电流、泄漏电流变化为6.3%和96%,常规注入条件变化为15.3%和599%。针对多晶条宽波动优化的Halo工艺条件,器件参数稳定性得到显著改善。

[1]田豫,黄如.超深亚微米非对称Haloldd低功耗新器件的研究分析[J].半导体学报,2003,24(5):510-515.

[2]汪洋,王兵冰,黄如,等.Sub-100 nm NMOS Halo工艺优化分析[J].固体电子学研究与进展,2006,26(4):445-449.

[3]王兵冰,汪洋,黄如,等.Halo注入角度对热载流子效应的影响及优化 [J].固体电子学研究与进展,2007,27(1):130-133.

[4]肖宏.半导体技术导论[M].第二版.北京:电子工业出版社,2013.1:244-246.

Study of Halo Technology in Improving Device Performance

XU Zheng,LI Hongzheng,ZHAO Wenbin

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

Short-Channel Effect(SCE)has long been deemed as one of the critical challenges facedin scaling down MOS devices.Halo structure effectively restrains SCE and improves the performance of small-size devices.During Halo implantation,tilt and energy impact on temperature property and process fluctuation,and POLY CD variety are considered.The paper compares various Halo implantation conditions with equal saturation current at room temperature.The experiment result shows that the best implant condition is 60°tilt and 100 KeV energy for 130 nm POLY CD,under which devices have the best temperature stability and process tolerance.

Halo;short channel effect;ion implantation;doping distribution;POLY CD

TN305.3

A

1681-1070(2016)09-0035-05

徐政(1971—),男,江苏涟水人,高级工程师,1994年毕业于电子科技大学,主要研究方向为集成电路工艺集成技术。

2016-6-3