基于FPGA的线性调频信号的脉冲压缩处理

卜 锋,姜晓波,张 鑫

(中国船舶重工集团公司第七二四研究所,南京 211153)

基于FPGA的线性调频信号的脉冲压缩处理

卜锋,姜晓波,张鑫

(中国船舶重工集团公司第七二四研究所,南京 211153)

当今雷达技术中,脉冲压缩技术体制很好地解决了脉冲探测传感器系统中作用距离和分辨能力之间的矛盾,因此该技术广泛用于雷达、声纳等系统。通过对FPGA硬件系统基本构架、软件开发、调试的基本流程的深入了解与掌握,完成了一种数字脉冲压缩处理器的设计和FPGA实现,包括系统架构设计、方案论证及仿真、算法实现、结果的测试等,为脉冲压缩技术的实际开发应用提供了更广阔的平台。

雷达;脉冲压缩;线性调频信号;FPGA;ISE

0 引 言

随着雷达系统在飞机、导弹、人造卫星及宇宙飞船等测控领域的广泛应用,雷达的作用距离、分辨能力、测量精度等性能指标随着飞行技术的高速发展也提出了越来越高的要求[1]。雷达系统的测距精度和距离分辨力对信号形式的要求是一致的,主要取决于辐射信号的频率结构。为了提高测距精度和距离分辨力,要求信号具有大的带宽,而测速精度和速度分辨力则取决于辐射信号的时域结构。此外,为提高雷达系统的发现能力,要求信号具有大的能量,也需要辐射信号具有大的时宽。由此可见,为了提高雷达系统的发现能力、测量精度和分辨能力,要求雷达信号同时具有大的时宽、带宽乘积。但是,在普通脉冲雷达中,雷达信号的时宽带宽积为一个常量(约为1),所以不能兼顾距离分辨率和速度分辨率两项指标。脉冲压缩雷达很好地解决了作用距离和分辨能力之间的矛盾,从而使其得以广泛用于雷达、声纳等探测系统。

1 脉冲压缩的原理

线性调频是最早和发展最充分的脉冲压缩技术。它通过在雷达大时宽脉冲信号中对载波频率进行调制以增加雷达的发射带宽,并在接收时进行脉冲压缩[2-7]实现匹配接收,从而完成时域信号能量和距离分辨力的统一。雷达系统工作的目的首先是要从含有噪声、杂波或人为干扰的接收信号中发现目标,这一过程实际上就是雷达信号最佳处理中的最佳检测问题。

设一线性滤波器的输入信号为x(t):

(1)

其中s(t)是雷达发射的确知信号,其频谱为

(2)

信号能量为

(3)

n(t)为均值为零的平稳白噪声,自相关函数为Rn(τ)=N0δ(τ)/2,则其功率谱密度为N0/2。设线性滤波器系统的冲击响应为h(t),其频率响应为H(f)。由叠加原理可得滤波器的输出响应为

(4)

由信号与系统及随机信号理论可知,滤波器对s(t)的响应ys(t)为

(5)

假设滤波器的输出信号成分在t0时刻形成了一个峰值,那么输出信号成分的峰值功率为

(6)

对上式应用Schwartz不等式可得

(7)

输出噪声的平均功率为

(8)

由式(3)和(7)整理可得

(9)

可见不等式(9)中等号成立时滤波器输出信噪比最大(SNRmax=2E/No)。而该式当满足式(10)时等号成立:

H(f)=KS(f)exp(-j2πft0)

(10)

对实信号s(t)而言,满足关系式S(w)=S(-w),则经傅里叶逆变换可得

(11)

式(10)就是要获得滤波器输出最大信噪比时滤波器的传递函数和与输入信号频谱之间应满足的关系,而式(11)是滤波器的冲激响应与输入信号时域波形之间应满足的关系。满足这种关系的线性滤波器称为匹配滤波器,即除了常数K和线性相位因子exp(-j2πft0)之外,匹配滤波器的频率特性恰好是输入信号频谱的共轭,其冲激响应由所要匹配的信号唯一的确定,并且是该信号的共轭镜像[8]。

匹配滤波器的作用是对输入信号s(t)完成一次相关运算。由h(t)与s(t)的强烈相关特性可知,在t=t0时刻,信号各频率分量同相叠加从而得到最大的输出,且输出只与信号能量有关。而输入噪声是随机的,各频率分量与H(f)间没有确定的关系,其输出功率只能是统计平均的结果。匹配滤波器的这种相关运算特性决定了它对平稳白噪声中确知信号的检测具有最优检测能力,是以输出信噪比最大为准则的最佳接收机[9]。匹配滤波器在许多场合都是一种最佳线性处理器,因此有着广泛的应用。

针对零中频低通系统,线性调频信号匹配滤波器的近似频率特性为

(12)

如果有信号(线性调频回波信号经过适当处理后)作用于滤波器输入端:

(13)

其中,fd为多普勒频移,匹配滤波器输出信号为

Y(f)=H(f)|S(f)

(14)

对Y(f)求傅里叶逆变换得到时域表达式y(t)为

(15)

2 FPGA的仿真与实现

2.1硬件平台系统的搭建

VerilogHDL是一种全方位的硬件描述语言,整个自顶向下或自底向上的电路设计过程都可以用VerilogHDL来完成。

ISE软件是由XILINX公司制作的专门针对FPGA硬件平台搭建的一款专业软件。ISim提供了集成到ISE内的、特性齐全的HDL仿真器。而ChipScope工具可在设计中直接插入逻辑分析器、系统分析器以及虚拟I/O小型软件内核,从而能够查看任意的内部信号或节点,包括嵌入式软硬处理器。系统以工作速度捕获信号,并通过编程接口输出,从而可大幅减少设计方案的引脚数。捕获到的信号随即通过分析工具进行显示和分析。

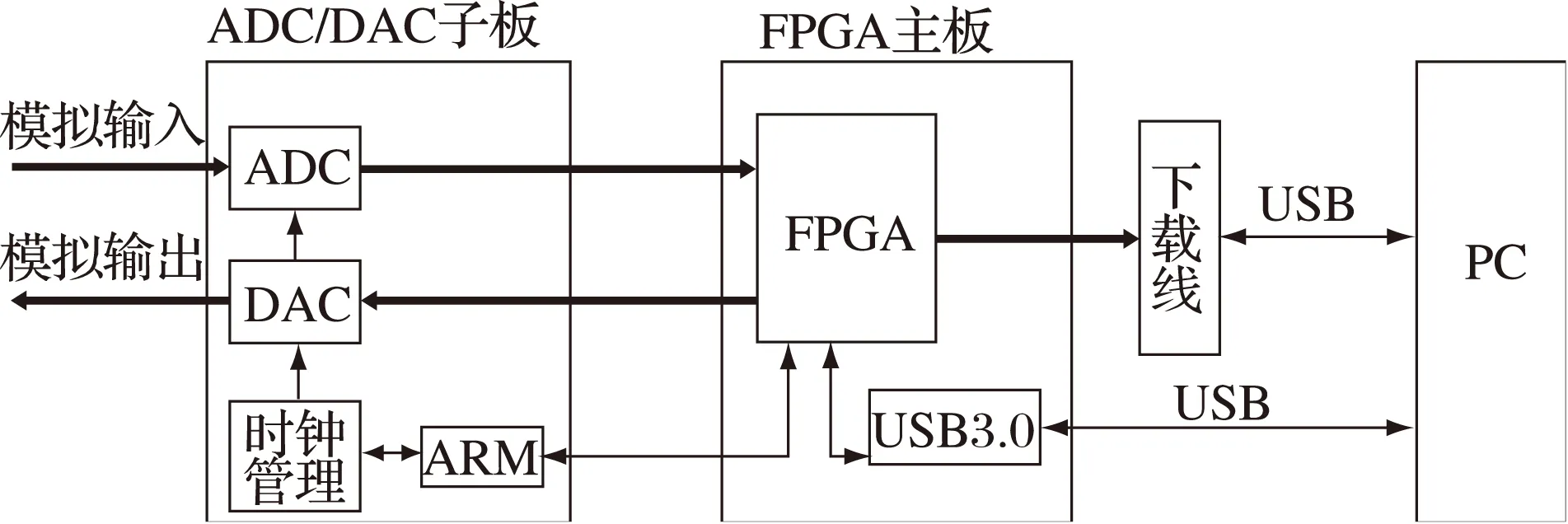

因此,本文也是基于FPGA的常规开发流程搭建的硬件架构系统,如图1所示。

图1 FPGA平台的硬件架构系统

由以上理论的推导得出,输入信号为线性调频脉冲信号,其表达式为

(16)

因而,根据硬件平台设定了相关参数如下:

fc=20 MHz,f0=15 MHz,fs=20 MHz,

B=4 MHz,T=16 μs,Tprf=500 μs

2.2ADS4249的ADC采样和中频采样实现及验证

ADS4249输入具有增益调节选择功能,从而可适应大动态范围的满量程模拟信号输入,同时还包含一个可以用于消除ADC直流零偏的偏移校正回路。ADS4249提供串行或并行控制接口,可对其工作参数进行配置,同时ADS4249采用DDRLVDS高速并行接口进行采集数据输出。

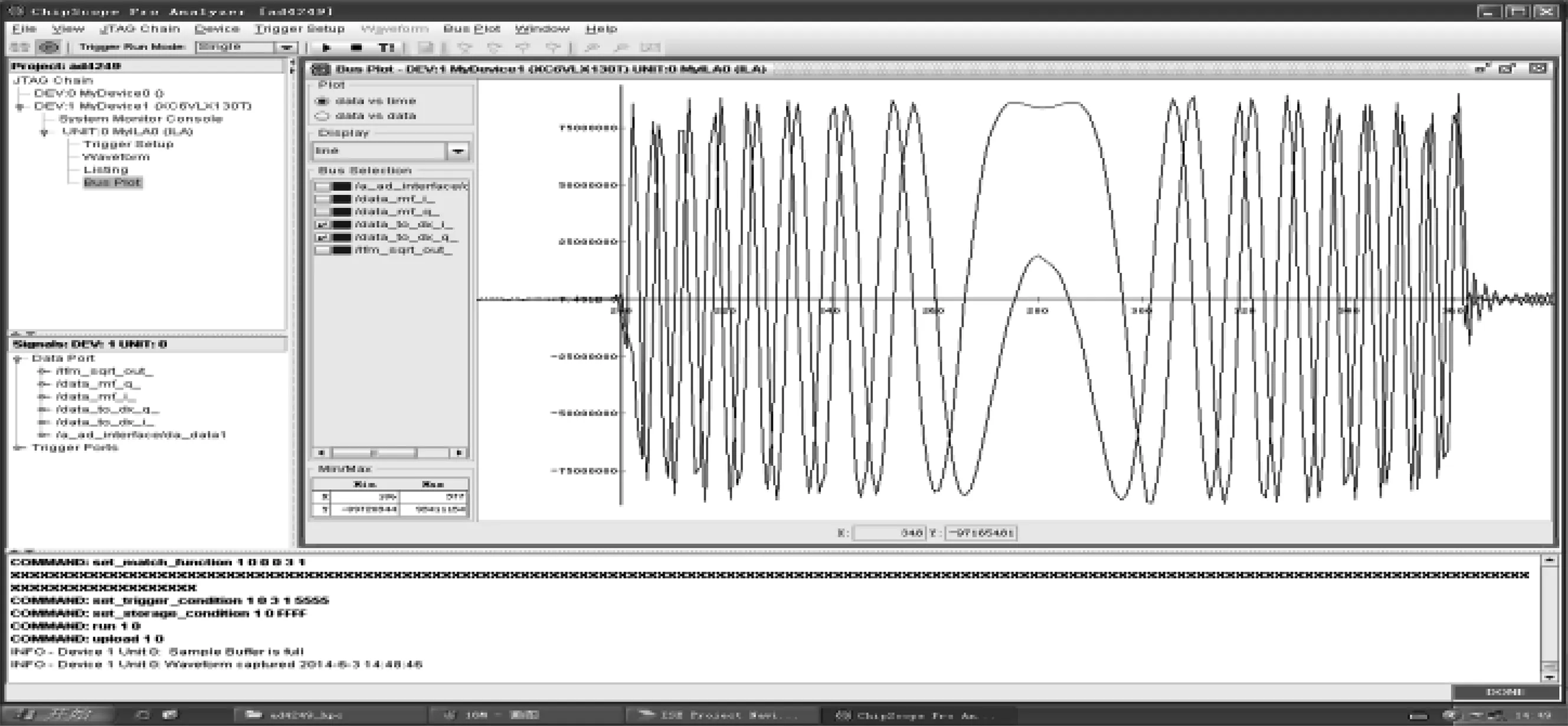

据此进行了ADC采集电路设计,然后将时钟采样频率的配置文件加载入LMK04804时钟发生器,得到ADS4249采样频率为20MHz。通过从信号源输出2MHz的正弦波信号,观察到Chipscope界面的图形,20MHz采样2MHz,所以每个周期有10个点,如波形图2。

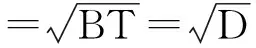

2.3LFM信号时域表示

图2中,f0=15MHz(中频频率),B=4MHz,T=16μs,Tprf=500μs。可以看出,这是一个带通信号。根据带通采样定理,带通信号的中心频率f0与采样速率fs满足fs=4f0/(2n+1)时,用fs进行等间隔采样所得到的信号采样值能准确地确定原信号。取n=1,从而fs=20MHz。

图2 ADS4249采样频率图

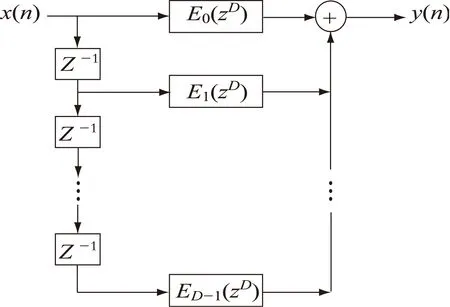

图3为多相滤波过程。按照相位均匀划分把数字滤波器的系统函数H(z)分解成若干个具有不同相位的组,形成多个分支,在每个分支上实现滤波。本次实验采用的是两路滤波,相差半个周期。

图3 多相滤波过程

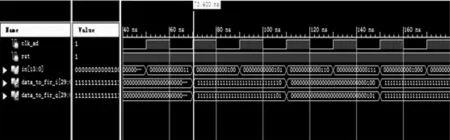

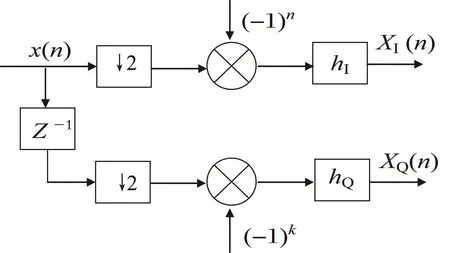

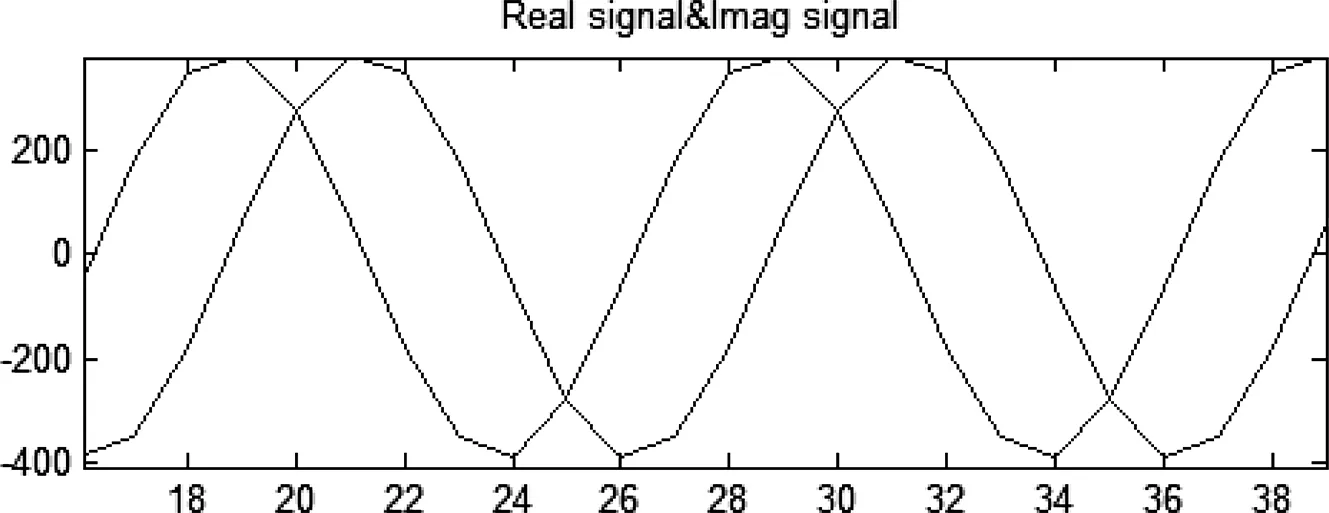

由图4可知,在经过时延滤波器之前,I、Q两路数据已经做到对齐。当采样频率满足fs=4f0/(2n+1)时,得到采样序列:

(17)

其中xBI(n)和xBQ(n)分别为信号的同相分量和正交分量。

(18)

(19)

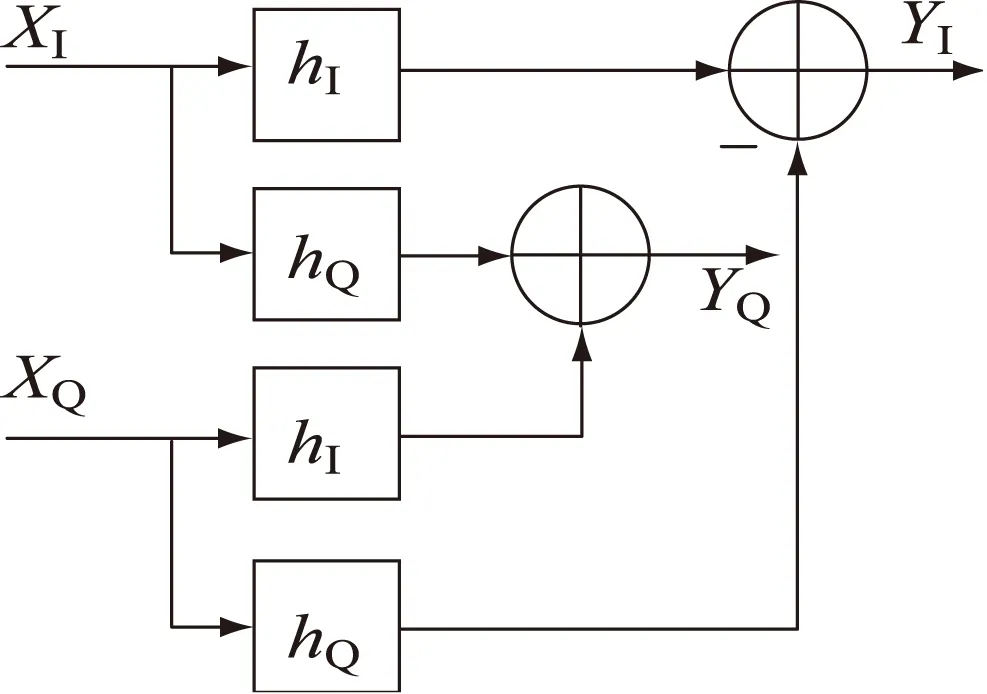

由于两倍抽取,所以得到的I、Q序列的数字谱相差一个延迟因子,体现在时域上相当于相差半个采样周期,所以需要采用延时滤波器加以修正。延时滤波器的冲激函数由理论给出:I路选择h3(n),Q路选择h1(n)原理图,如图5所示。

图4用modelsim仿真软件进行仿真两倍抽取

图5 加载延时滤波器的冲激函数原理图

最后得到的I、Q两路信号应该严格正交。用信号发生器产生16MHz正弦信号,经过采样后相当于进行了下变频,产生了一个2MHz的基带信号。再经过抽取,I、Q两路应该为相互正交的两个1MHz正弦波,见图6。同时利用chipscope进行实时采集信号得到波形图,如图7所示。从图7中可以看到I、Q两路信号,但是在ChipScope中实际观察的样子与仿真结果略有偏差,是因为初始相位的不确定性,但这不影响两路信号的正交性以及实验的结果。

图6matlab仿真结果

2.4匹配滤波以及求模输出验证

输出的两路信号求模,此时得到的就是脉冲压缩信号的时域数据。通过调用IPcore来实现高效滤波器的设计,如图8所示。取中频解调信号的高20位作为输入,差分系数量化为20位,每个滤波器通道输出40位。将I、Q两个通道的高31位两路相加,I、Q输出32位信号。

图8 匹配滤波器原理框图

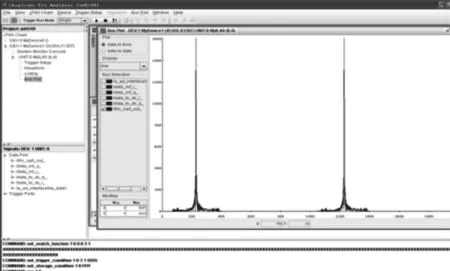

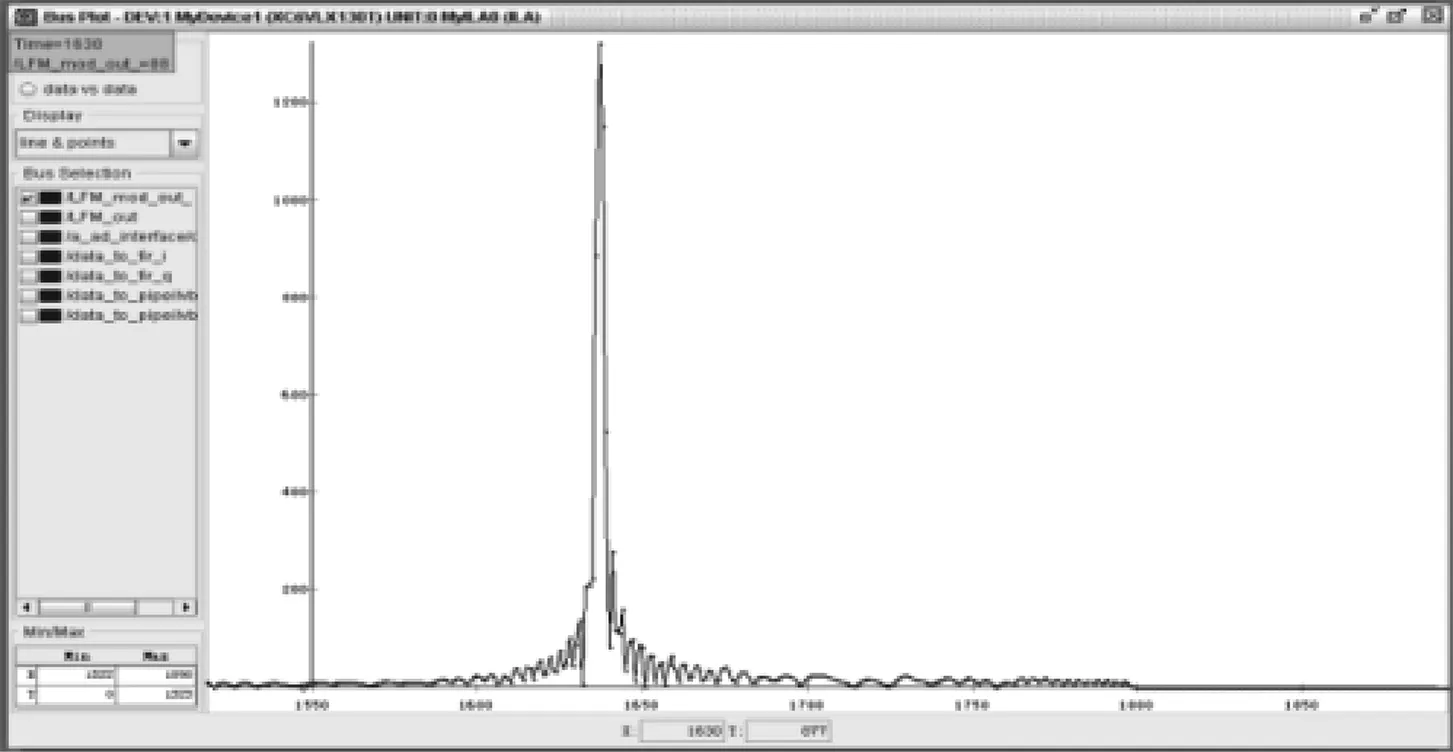

输入信号为线性调频信号,经过匹配滤波后,输出I、Q路为冲击信号如图9所示,由尖峰所在处可以得到回波信号的距离信息。I、Q两路通道平方、相加后输出65位信号,截取高32位取模输出。输入线性调频信号,经过求模输出模块后即可得到输出信号图,如图10所示。

图9 输出I、Q两路信号

图10 求模输出信号

线性调频脉冲信号通过匹配滤波器后,输出脉冲的包络近似为sinx/x函数形状,最大的第一旁瓣为主瓣电平的-13.2dB,其他旁瓣随其离主瓣的间隔x按1/x的规律衰减,旁瓣零点间隔为1/B。所以,计算主旁瓣比为20*log(333/1605)= -13.66dB,近似于理论值-13.2dB。

结果表明,本文所设计的脉冲压缩系统满足了预先的设计要求,并具备进步扩展的能力。

3 结束语

数字脉冲压缩技术相对于传统的模拟脉压具有很大的优越性,其精度高、灵活性大、可靠性好,易于大规模生产,已成为现代雷达脉压系统的发展趋势。但是,数字脉压处理器的计算量大,传统的多片DSP的硬件结构,电路较复杂、功耗大。为了克服这些缺点,基于FPGA实现的数字脉压处理器受到了国内外学者的青睐。此次对IP核的使用降低了芯片设计的技术难度,节省了很多时间。但是,相对的FIR数字滤波的算法并未实现深入的探讨与论证,这也是下一步研究的重点所在。本次设计与实现给雷达脉压系统的研究提供了更坚实的理论基础,仿真结果也与实际使用情况相符。另外,在论证过程中也体会到应本着系统在工程中的适用性原则,不能盲目追求更高的速率或精度,而应更多地考虑到资源与速度、资源与精度的折中问题,使之能够更好地在实践中发挥作用。

[1]向敬成,张明友.雷达系统[M].成都:电子科技大学出版社出版,1997:103-115.

[2]胡广书.数字信号处理——理论、算法与实现[M].北京:清华大学出版社出版,2003:10-11.

[3]李素芝,万建伟.时域离散信号处理[M].北京:国防科学技术大学出版社,1992:20-22.

[4]李洪涛,朱晓华,顾陈.VerilogHDL与FPGA开发设计与应用[M].北京:国防工业出版社,2012:30-31.

[5]清华大学无线电系快速傅里叶变换组.快速傅里叶变换[M].北京:人民邮电出版社出版,1980:20-25.

[6]丁鹭飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,2002:112-130.

[7]武剑辉.多波形频域脉冲压缩系统的研究[D].电子科技大学,2002:38-39.

[8]丁智权.线性调频信号的脉冲压缩系统设计与FPGA实现[D].电子科技大学,2007:30-32.

[9]潘琳.基于FPGA的雷达脉冲压缩系统的研究与实现[D].上海:上海大学,2008:20.

PulsecompressionprocessingofLFMsignalsbasedonFPGA

BUFeng,JIANGXiao-bo,ZHANGXin

(No.724ResearchInstituteofCSIC,Nanjing211153)

Inmodernradartechnologies,thepulsecompressiontechnologysolvestheproblemsbetweenthedetectionrangeandtheresolutioncapabilityinthepulsedetectionsensorsystemssatisfactorily.Therefore,thetechnologyiswidelyappliedtoradarandsonarsystems.Basedonthein-depthknowledgeandagoodcommandofthebasicstructureoftheFPGAhardwaresystem,thesoftwaredevelopmentandthebasicprocedureofthedebugging,adigitalpulsecompressionprocessorisdesignedbasedontheFPGA,includingthesystemarchitecturedesign,projectdemonstrationandsimulation,algorithmimplementation,andtestoftheresults,providingawiderplatformfortheactualdevelopmentandapplicationofthepulsecompressiontechnology.

radar;pulsecompression;LFMsignal;FPGA;ISE

2015-12-20;

2016-01-10

卜锋(1980-),男,工程师,研究方向:雷达发射技术;姜晓波(1980-),男,工程师,研究方向:雷达总体技术;张鑫(1981-),男,工程师,研究方向:雷达总体技术。

TN78

A

1009-0401(2016)03-0036-05