一种新型相控阵体制的波控单元设计

高东博

一种新型相控阵体制的波控单元设计

高东博

(中国电子科技集团公司第五十四研究所,河北石家庄050081)

针对一种新型相控阵传输体制的特点和要求,对相控阵设备中的波束控制单元的实现方法展开研究。设计硬件布局与实现方案,并对基于FPGA和单片机的嵌入式软件架构进行深入分析与讨论,重点研究T/R组件接口模块、定时动作模块等主要功能单元的设计方法,探讨波束控制单元的主要工作流程,给出了完整的设计与应用方案。试验结果表明,依据该方案研制的波控单元试验结果满足新型相控阵体制的信息传输要求。

波束控制单元;相控阵;T/R组件接口;模块化设计

引用格式:高东博.一种新型相控阵体制的波控单元设计[J].无线电工程,2016,46(5):49-52,84.

0 引言

一种新型相控阵信号体制具有信道频点高、切换时刻需预设存储以及定时控制等特点。波束控制系统是应相控阵雷达而产生的计算控制技术[1]。实际上,波束控制系统具有对阵面控制完整的数据收发通道[2],是每个相控阵天线系统的核心组成部分[3]。

采用新信号体制的相控阵系统目前并不多,已有的成果中的波束控制功能均是集成在其他控制电路中,没有独立的波束控制单元,技术移植和系统调试比较繁琐。本文针对新信号体制的技术特点,对波控单元的硬件和软件设计方案展开研究,增进波控单元的独立性和可移植性。

1 总体设计

波控单元承担控制计算机与天线后端的信道收发组件(以下简称T/R组件)之间的波控码传输、控制指令传输、工况信息传输的任务。波控单元需完成数据信息的硬件接口转换、通信协议转换等工作。因T/R组件数量众多,波控单元需要扩展许多数据线,需要FPGA或CPLD等现场可编程门阵列器件扩展数据接口;相控阵天线布设在户外,需要与室内机房的控制计算机采用稳定可靠的通信体制和协议;波控单元还需支持满足传输带宽要求的通信协议。

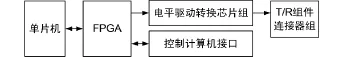

根据需求分析,波控单元采用单片机+FPGA的方式完成波控单元核心功能设计。其中单片机负责业务流程控制和数据协议解析,FPGA负责扩展数据接口和信号时序控制。波控单元外围配置足够数量的连接器和电平驱动转换芯片,连接T/R组件。波控单元的总体设计原理框图如图1所示。

图1 波控单元总体设计原理

2 硬件设计

基于这种新型相控阵体制的频点和幅度特性,相控阵天线阵列较小,天线中心间距只有几毫米,整阵面积非常小。T/R组件按照天线分布进行组阵,留给波控单元的空间非常小,仅有T/R组件阵列到电源模块之间的空隙,需要研制小型化、高集成度的波控单元来满足项目要求。

由于外部设备的数据线数量很多,本次设计使用1片单片机作为MCU,通过2片FPGA扩展与T/R组件、RS422串口、馈电单元的数据以及控制接口,总体掌控波控单元的业务流程和逻辑判断。

波控单元根据T/R组件的硬件接口对连接器进行选型。由于数量多、布局需留空隙等原因,连接器的大小成为制约波控单元最小面积的主要因素,同时考虑长期应用的稳定性,连接器选用带有紧固装置的产品。

波控单元随相控阵天线系统布设在户外,元器件选用要考虑环境适应性较高的工业级芯片和器材。

波控单元的硬件实现采用10层PCB设计,包含6个布线层和4个内电层,其中内电层包含2个参考地。另外2个电源内电层采用内缩设计,遵循“20H原则”,即多层PCB中的电源层的尺寸必须比其地层的尺寸小20H,而H是这2层板间的垂直距离[4]。20H原则在适用条件下能够降低EMI[5]。

元器件布局考虑数字电路和模拟电路的隔离,要注意高频数字元件要远离噪声敏感的模拟元件,敏感模拟电路上方禁止布线等规则[6]。

3 软件设计

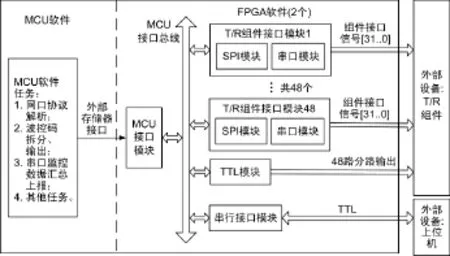

波控单元的总体软件架构示意图如图2所示。

图2 波控单元总体软件架构

MCU软件主要完成解析网口收到的业务信息、控制指令,解出波控码,通过外部存储器接口输出到FPGA中,汇总T/R组件的工况信息和告警信息,并通过网口上报等功能。在MCU软件中,所有FPGA接口模块的地址均使用预定义的方式进行声明,使用预定义可以改进程序设计环境,提高编程效率[7]。

FPGA软件主要完成T/R组件的接口模块设计、监控串口的接口模块设计以及授时定时模块设计等时序控制类任务。FPGA软件完成波控单元对外连接、外部通信和定时控制等主要业务功能,FPGA程序设计需要划分成一些独立的模块[8],是波控单元软件设计最重要的部分。

FPGA软件使用System Verilog语言编程,采用接口方式简化与MCU的时序关系,并统一FPGA内部各模块的接口。通过使用这种结构可以大大简化大型复杂设计的建模和验证,也可以为系统中每一个终端程序提供统一的接入方式,从而不需要对每一个终端程序进行接口的时序设计,节省了重复声明端口的劳动时间,避免了当设计规范变动时对所有模块的修改,从而有效预防了低级错误的产生[9]。

3.1 T/R组件接口模块设计

T/R组件接口模块的设计是整个波控单元设计的重点和关键所在,其设计质量直接影响系统的工作效率和稳定性。

由于全部射频通道高达576个,如果用MCU依次模拟波控码传输时序将占用大量的时间,影响系统性能。T/R组件接口模块的功能是在MCU的控制下分发波控码,将与T/R组件控制有关的时序操作全部放在FPGA中完成,如波控码传输、指令传输和工况接收解析,并且提供一组寄存器供MCU访问,从而达到控制T/R组件的功能。这就将单片机从时序模拟中解放出来,节省了大量的MCU占用时间,使得MCU可以将更多的时间用在计算、调度和数据处理上[10]。

T/R组件接口模块在 2个 FPGA内部共有48个实例,对应48个T/R组件。由于设计初始并不知道接口模块与真实T/R组件的对应关系,所以在接口模块设计时采用参数化设计,将接口模块的编号参数化,将访问地址与编号相关联。编程使用参数可以提高程序的可读性,也利于修改[11]。

T/R组件的接口模块用来连接T/R组件的波控码传输接口、四-十六译码器接口和异步串口。T/R组件的接口模块原理框图如图3所示。

T/R组件接口模块发送波控码的工作步骤如下:

①MCU通过外部存储器接口将12个通道总共32(其中27 bit有效)×12 bit的波控码写入FIFO;

②MCU通过外部存储器接口通知SPI_Encoder模块(CODE_READY),12个通道的波控码已经准备好;

③SPI_Encoder模块清零CODE_TX_OK信号,使能四-十六译码器,首先选通通道0;

④SPI_Encoder模块从FIFO中读出32 bit数据,截取低27 bit有效波控码,通过SPI接口按照时序发给T/R组件;

⑤SPI_Encoder模块操作四-十六译码器,选通通道1,重复步骤④,然后再选通下一个通道;

⑥SPI_Encoder模块完成全部波控码发送后,关闭四-十六译码器,将SPI接口信号线置为空闲状态,置位CODE_TX_OK信号,完成操作。

图3 T/R组件接口模块原理

T/R组件接口模块还包含一个异步串口收发模块,2根信号线TX和RX直接连接到T/R组件的异步串口上。其中,RX的部分接收来自T/R组件的数据信息,当有数据到达时,串口模块能够按照约定的接口格式进行解帧处理,将T/R组件上报的工况进行处理,提取出工况信息,并对其中的温度信息进行字符到数据的转换,存储在寄存器中。完成解帧后,模块会使能HAVE_RX_DATA信号。MCU会一直轮询全部T/R组件接口模块的Ctrl_reg寄存器,当发现某个HAVE_RX_DATA信号有效时,就会读取该模块的RX部分,获得已经完成数据转换的T/R组件的工况信息。这样将解帧的过程放在FPGA中进行,可以同时并行处理48个T/R组件的上报信息,大大节省了MCU的时间,不会影响其他重要流程的运行。

Ctrl_reg模块是T/R组件接口模块的控制/状态寄存器,MCU通过写这个寄存器来控制T/R组件接口模块的全部行为,同时通过读这个寄存器来了解T/R组件接口模块的当前状态。

SPI_Encoder模块对外的信号线包括:读FIFO数据的信号、SPI接口信号、与Ctrl_reg连接的信号和控制四-十六译码器的信号。

3.2 时间维护模块设计

波控单元必须在本地维护一个与系统同步且稳定准确的时间。波控单元通过与MCU的数据接口获得时间信息,并引入系统的秒脉冲信号作为本地周内秒更新的触发信号,并通过分频的方式在本地维护一个毫秒级时间,用做更准确的定时使用。

时间维护模块包括授时/守时单元和毫秒时钟产生单元2个主要部分。其中,授时/守时单元通过与MCU的接口获得精确到秒的系统时间,使用系统分发的秒脉冲(1 pps)信号作为触发信号进行守时,并输出秒级系统时间。毫秒时钟产生单元使用本地时钟分频产生1 000 pps的时钟,用来毫秒计数,并输出毫秒时间,同时使用系统分发的1 pps信号进行复位,防止分频产生的时钟积累与系统时钟的误差。

时间维护模块接收一次系统授时后,能够进行精确守时,为波控单元提供可靠的时间信息。

3.3 定时动作模块设计

T/R组件需按照系统规定的收发时隙进行发射通道和接收通道的切换,切换过程包括逻辑通道切换和收发通道电源控制的切换,其切换过程需遵循一定的时序要求,若时序错乱可能会造成通信中断或射频通道损坏的后果。如果收发通道切换过程中需更新波控码,则更要设计可靠的时序来保证波控码的及时更新。

定时动作模块输出4个信号:T信号代表发射通道的电源使能,R信号代表接收通道电源使能,T/R信号代表逻辑切换收发通道,DARY信号有效时使能新的波控码。由于系统对收发通道的使能控制并不一定是“收、发、收、发”依次切换,而且T、R 和T/R信号必须在极短时间内按照时序切换完成,且通常切换过程中都需要用DARY信号更新波控码,所以要求定时动作模块能够缓存定时动作指令,并按时准确执行。

一个健壮的程序应该对可能出现的异常情况进行防御性编程[12]。定时动作模块的保护性设计使得T和R信号不可能同时有效,即T/R组件的发射、接收通道不可能同时打开,从而防止发射通道的信号灌入接收通道,造成组件损坏。

4 业务流程设计

以原理框图的形式介绍波控单元在正式运行时主要用到的功能业务流程。

4.1 波控码分发功能流程

波控单元能够将控制计算机下发的波控码分发到每一个T/R组件。本功能是波控单元最主要的功能,单个T/R组件的波控码分发流程设计如下:

①单片机解析波控码指令,分离每个T/R组件的波控码;

②将分离出的波控码分别写入FPGA中的T/R组件接口模块,与真实的T/R组件相对应;

③启动模块发送功能,T/R组件接口模块会自动将缓存的波控码依次发给每个组件的12个通道中。

4.2 本机时刻维护功能流程

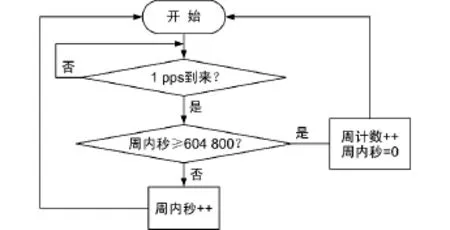

波控单元能够在本地维护周、周内秒和周内毫秒。功能实现流程分为2个独立的流程,周和周内秒维护流程如图4所示,使用系统提供的1 pps信号触发更新。周内毫秒维护流程如图5所示,使用FPGA内部的计数器计时更新,同时使用系统提供的1 pps信号对计数器复位,相当于每秒消除一次本地时钟与系统时钟的误差,保证系统的计时精度。

图4 周和周内秒维护功能流程

图5 周内毫秒维护功能流程

4.3 波控码传输校验功能流程

波控单元能够完成SPI接口的波控码传输校验功能,即发送完毕波控码后,再读取回来并做校验。本功能用来检验波控码传输通道的正确性,可对整个T/R组件阵列进行在线/离线的正确性验证。

本功能实现流程设计如下:

①接到控制计算机指令,生成校验用的波控码;

②启动波控码分发功能流程,将波控码分发给每个T/R组件的每个通道;

③控制波控码传输接口的时钟信号线继续输出时钟,控制波控码传输接口的数据信号线方向由输出转为输入;

④接收从T/R组件传回的波控码,与生成的校验波控码进行比对;

⑤记录比对结果并组帧上报给控制计算机。

5 系统集成

5.1 集成试验

波控单元与T/R组件阵列按照系统接线图进行连接,并与系统控制计算机通过网络进行通信,接收波控码和指令,回传系统工况和指令应答。

T/R组件接收波控码,按照波控码内的幅度、相位权值产生波束并发射。用仪器测得的数据恢复波束形状如图6所示。

图6 波束恢复

5.2 结果分析

从图6可看出,T/R组件正确执行了波控码规定的幅度和相位特性,生成了正确方向和大小的波束。

本文的研究内容能够将波控码数传、工况上报和指令下达的功能高度集成在仅仅0.06 m2的印制板上,使得整套系统的体积大大减小,电缆数量锐减为原系统的1%,数据流程也大大简化。

6 结束语

本文介绍了一个基于一种新型相控阵体制的波束控制单元设计方案和实例。该实例在ATmega128+EP4CE115(2片)+QuartusII9.1的平台下调试通过,能够满足系统对波控码传输的时效性、正确性和可校验性的要求。

本设计的核心模块均为参数化设计,设计语言为C语言和System Verilog语言,均为通用的嵌入式设计语言,能够方便地移植应用在其他相同体制的相控阵系统中。

[1] 张宇驰.基于FPGA平台的波控系统设计[D].南京:南京理工大学,2012:3-4.

[2] 郑 清.相控阵雷达波控系统技术研究[J].现代雷达,2006,28(4):53-55.

[3] 高云珠,王晟达.相控阵雷达波控系统研究[J].控制系统,2008,24(4-1):81-83.

[4] 黄秋元,鄢 凯,王 斌,等.四层PCB板中20H规则的辐射分析[J].武汉理工大学学报,2008,32(2):244-247.

[5] MONTROSE M.Analysis on the Effectiveness of the 20H Rule for Printed-circuit-board Layout to Reduce Edge-radiated Coupling[J].Electromagnetic Compatibility,IEEE Transactions,2005,47(2):227-233.

[6] 任腾龙.低功耗模数混合集成技术研究与设计实例[D].上海:复旦大学,2010:18-19.

[7] 谭浩强.C程序设计(第2版)[M].北京:清华大学出版社,1999:186-187.

[8] SMITH D R,FRANZON P D.面向数字系统综合的Verilog编码风格[M].汤华莲,田 泽,译.西安:西安电子科技大学出版社,2007:119.

[9] SUTHERLAND S,DAVIDMANN S,FLAKE P.System Verilog硬件设计及建模[M].于敦山,何 进,韩 临,等,译.北京:科学出版社,2007:209-240.

[10]马英昌,高东博.基于System Verilog的接口模块化设计方法[J].无线电通信技术,2013,39(5):51-54.

[11]王 伟.Verilog HDL程序设计与应用[M].北京:人民邮电出版社,2005:87-89.

[12]KOENIG A.C陷阱与缺陷[M].高 巍,译.北京:人民邮电出版社,2008:124-126.

Design of a Beam Steering Unit Based on BGNSS Phased Array System

GAO Dong-bo

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

The beam steering unit for a phased array system is designed,which includes the PCB layout,the chip selection and the built-in software architecture of FPGA and MCU.The research focuses on the design of FPGA modules,such as T/R module interface and action timer.The main flow chart of this beam steering unit and the whole design and application scheme are presented.The test result indicates that the beam steering unit based on this scheme satisfies the transmission requirement of the phased array system.

beam steering unit;phased array;T/R module interface;modularization design

TP322

A

1003-3106(2016)05-0049-04

10.3969/j.issn.1003-3106.2016.05.13

2016-01-02

高东博 男,(1984—),工程师。主要研究方向:卫星导航应用、数字信号处理。