基于FPGA的信道化接收机设计及工程应用

梁中英,沈炜

(广州海格通信集团股份有限公司广东广州510663)

基于FPGA的信道化接收机设计及工程应用

梁中英,沈炜

(广州海格通信集团股份有限公司广东广州510663)

基于最小化资源实现宽带多信道接收机的目的,采用基于多相滤波的信道化接收机设计结构,在分析原理的基础上,结合实际工程应用,使用Xi1inx公司的Virtex_4系列FPGA实现了256信道接收机的设计。设计中充分有效地利用了FPGA中的硬件资源(DSP48、B1ock RAM、OSERDES等),优化实现结构,提高资源利用率,工程应用证明该结构是可靠有效的。

多相滤波;信道化接收机;Xi1inx;FPGA

在电子对抗中,一般对侦察接收机的要求有:宽带接收、高灵敏度、大动态范围等。实现信号的全概率截获是非常重要的,模拟接收机已经很难满足上述要求,而数字信道化接收机的设计灵活,能够满足处理的要求[1]。鉴于该理论需要主运算器件具有并行处理的能力,而FPGA在硬件结构上具有极大的灵活性,可适用于这种需要并行处理的理论,所以在设计中选择FPGA对其进行实现。硬件实现结果显示,设计可以达到预期的要求。

1 复信号的信道化接收机的数学模型

实际信号处理中,首先通常需要对接收到的信号进行正交变换,将其变为复信号。复信号的信道划分如图1所示[2]。文中所提到的设计是将中频采样的信号进行正交插值后变为复信号进行后续处理,所以这里只讨论复信号的信道化接收机实现。

图1 复信号的信道化划分

图2 复信号滤波器组的低通实现

对复信号进行滤波时可以采用低通型滤波器组来实现,如图2所示。图中hLP(n)为原型低通滤波器,本振角频率ωk=其作用是将图1中的第K个子频带(信道)移至基带(零中频),然后通过后接的低通滤波器hLP(n)滤出对应的子频带,由于滤波后的信号带宽为2π/ D,故可进行D倍抽取,以获得低采样率的信号[3]。

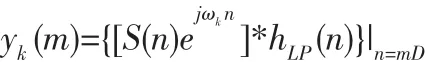

由图2可得第K路信道的输出为:

将式(1)代入上式得:

则:

其中DFT(.)表示离散傅里叶变换。根据上述推导过程,得到基于多相滤波结构的信道化接收机数学模型[4]如图3所示。

图3 复信号的信道化接收机框图

在图3中,第一个乘法器的本振信号,当D为偶数时取(_1)m,D为奇数时取1。从图中可以看出,此时不仅D倍抽取器已位于滤波器之前,而且现在每个信道的抽取滤波器不是原来的原型低通滤波器hLP(n),而是多相滤波器hp(m),其运算量降至了原来的1/D并且极大的提高了这种信道化接收机的实时处理能力。另外,图中的DFT可以采用其高效算法FFT来实现,运算速度可以大大提高。

2 宽带信道化接收机的FPGA实现

由图3的信号化接收机结构可以得出FPGA的实现框图如图4所示。

图4 信道化接收机FPGA实现框图

由图4可知,整个设计由6部分组成:符号变换、抽取器、通道滤波、复乘、FFT和输出模块。设计中选择Xi1inx公司的XC4VSX55来实现,XC4VSX55拥有硬件资源[5]:320个B1ockRAM,每个180Kbit,共5 760 Kbit;24 576个S1ices;512 个XtremeDSP;640个IO。下面介绍一下各个模块的实现。

2.1符号变换和抽取器的实现

本设计中D=256,图3中第一个乘法器的本振信号为,没有必要通过乘法器来实现,直接使用组合逻辑进行符号变换即可。设计中将符号变换模块在抽取之前实现,可以将一批数据(256个)同时实现符号翻转。符号变换由一个9位计数器来实现,当计数器小于256时,数据符号取反,反之,则不变。

若使用触发器实现抽取器,需要22*2*16*256=180 224 个1 bit触发器,即需要90 112个S1ice来实现,已经超出了FPGA的资源,此时触发器工作频率很低,但也不能复用。若使用数据选择器来实现,也需要占用大量的逻辑资源。设计中采用FIFO来实现抽取,只占用22个B1ockRAM和154个S1ices,154个S1ices用于控制FIFO的读写使能信号,主要应用FPGA的硬件资源(B1ockRAM),B1ockRAM既可以作为RAM使用,也可以作为FIFO来使用,并且不占用其它的逻辑资源。抽取器使用FIFO实现时,22个FIFO依次相连,如图5所示,每个FIFO中放入256个数据,当22个FIFO都已存放了256个数据时,第22个FIFO开始输出,其它FIFO也同时输出,对输出的并行数据进行通道滤波处理。

图5 抽取器及通道滤波的实现

使用FIFO来实现抽取器,具有如下优点:1)能够提高抽取的速度;2)节省逻辑资源,Virtex4系列FPGA中有大量的B1ockRAM,使用B1ockRAM来实现FIFO不占用额外的逻辑资源;3)有利于后级通道滤波的复用。

2.2通道滤波和复乘的实现

乘法器是FPGA中的重要资源,为了减少乘法器的使用数目,必须设法对乘法器进行复用。通道滤波时如果每个通道都用一个乘法器的话,共需使用256个乘法器,两个相同的结构在FPGA中实现,已经用尽了所选择的FPGA(XC4VSX55)的乘法器(512个),并且前端DDC部分还要使用乘法器,所以需要对乘法器进行复用。

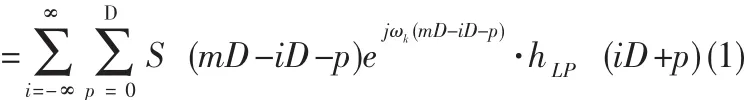

通道滤波使用Virtex4系列FPGA中的DSP48模块来搭建,因为DSP48模块不仅是一个18*18 bit的乘法器,还包含许多寄存器,加法器及相邻DSP48互连的接口。设计中充分利用其硬件资源,通道滤波模块复用256次,第1次输出是第0通道滤波后的数据,第2次输出是第1通道的数据,第n次输出是第n_1通道的数据。通道滤波是I,Q两路同时实现的,通道滤波结束后直接进行复乘。通道滤波结果是流水输出的,为FFT的输入提供了方便。

通道滤波的系数存放在22个B1ockRAM中,22个B1ockRAM采用统一的地址信号,如图7所示。设计中地址信号从0递增到255,然后返回到0,循环往复。

图6 DSP48模块结构

图7 系数输出框图

2.3FFT的实现和输出

FFT变换通过调用Xi1inx的IP核来实现。FFT采用流水方式,输入数据由复乘后直接进入FFT,经过若干个时钟周期后,结果就源源不断地输出。输出将64个通道的数据放入一个RAM中,作为一组,并转串之后通过高速的LVDS输出,以320 MHz的速率输出到其它信号处理板。RAM采用双口RAM,双口RAM一端以32位数据输入,另外一端以8位数据输出。再调用FPGA硬并转串模块OSERDES,转为串行数据。也可以自己编写程序实现并转串模块,但那样不但不能完全利用FPGA的硬件资源,也浪费FPGA内部的逻辑资源,无法达到FPGA硬件并转串模块的性能。

3 硬件实现验证

实现上述结构后,使用信号源产生不同频点的信号,对应于不同的通道,观测多相滤波后的结果即可对该结构进行验证。信号源输出某频点信号,频率值对应本设计中的第125个通道,chipscope采样结果如图8所示,其中滤波结果的通道号xk_index的值从0~255,表示256个通道。从图中可以看出,通道号124(即第125个通道)的结果远大于其他通道的结果,即多相滤波的结果为第125个通道,与输入的频点所在通道相符。

用上述验证方法对不同通道结果都进行了验证,结果与理论通道相符,说明了这种实现结构的正确性和可行性。

图8 多相滤波结果输出的chipscope采样图

4 结束语

FPGA的硬件资源为信号处理带来了便利,本文所使用的设计方法合理利用了FPGA自身的硬件资源,使用较少的逻辑资源实现信道化接收机的结构,提高了FPGA的资源利用率,在单片FPGA上实现了2路宽带信号的接收和处理,且性能满足了设计的要求。

[1]杨成山.基于FPGA的数字信道化接收机研究和实现[D].哈尔滨:哈尔滨工业大学,2013.

[2]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[3]杨静.信道化数字接收机技术的研究[D].成都:电子科技大学,2003.

[4]Fredric J.Harris,Chris Dick,Michae1 Rice.Digita1 Receivers and Transmitters Using Po1yphase Fi1ter Banks for Wire1ess Communications[J].IEEE Transactions On Microwave Theory and Techniques,2003,51(4):3_5.

[5]Xi1inx.Virtex_4 User Guide[S].March 21,2006.

[6]Xi1inx.XtremeDSP for Virtex_4 FPGAs User Guide[S].Ju1y 5,2006.

Deslgn and lmPlementatlon of channellzed recelVer based on FPGA

LIANG Zhong_ying,SHEN Wei

(Guangzhou haige communications group incorporated company,Guangzhou 510663,China)

Based on the purpose of designing broadband mu1ti_channe1 receiver with 1east resources,adopting the design structure of channe1ized receiver based on po1yphase fi1ters,on the basis of ana1yzing the princip1e,combined with practica1 app1ication,the design of 256 channe1 receiver are rea1ized by Virtex_4 FPGA of Xi1inx Corporation.In the design,the hardware resources of the FPGA are made fu11 use of,such as DSP48,B1ock RAM,OSERDES and so on,the design structure is optimized and the resource uti1ization is improved.The experiments i11ustrate the effectiveness of this design.

po1yphase fi1tersj channe1ized receiverj Xi1inxj FPGA

TN859

A

1674_6236(2016)10_0147_03

2015_06_02稿件编号:201506038

梁中英(1985—),女,黑龙江绥滨人,硕士,设计师。研究方向:卫星通信领域中的基带数字信号处理。