一种12bit流水线型模数转换器的研究与设计

刘 洋

(天津维晟微科技有限公司,300457)

一种12bit流水线型模数转换器的研究与设计

刘洋

(天津维晟微科技有限公司,300457)

本文设计和研究了一种低功耗12Bit 流水线模数转换器的结构,其采用了TSMC 0.18um工艺设计,3.3V单电源电压,5MHz采样率,动态范围为1V,INL为0.5LSB,DNL为2LSB,通过详细的电路原理分析和软件Cadence的仿真,并流片测试,性能达到设计初衷。

流水线型模数转换器(Pipeline ADC);子数模转换器(Sub-DAC);子数模转换器(Sub-ADC);余数放大器;MDAC

在大多数的通讯系统中,通常都会应用DSP或MCU数字模块来处理通讯信息,这种方式必然要求要将模拟信号转换成可识别的数字信号,也就是需要通过模数转换器(ADC)来实现。今天,随着对无线通讯系统的需求爆发式的增长,对ADC的需求也越来越大,而ADC的高速,低功耗等性能将直接影响通讯系统这方面的指标。

1 Pipeline ADC 系统原理

PipelineADC 主要由采样保持电路(SH),子数模转换器(Sub-DAC),子模数转换器(Sub-ADC),余数放大器,数字校准电路组成,其中最核心的为子级转换电路MDAC,MDAC是Sub-DAC,余数放大器,减法器组成,它的功耗,精度,速度,将直接影响整个ADC系统的性能。由于本设计用于通讯系统,为了增强抗干扰能力,本设计选择了差分输入的电路结构,这样可以有效的抑制信号的共模噪声,在功耗方面,在对比了通用的1.5Bit与2.5Bit的 MDAC电路结构后,本设计采用了2.5Bit的结构,使其原本需要9级的stage电路,减少为目前的5级,

流水线模数转换器工作原理如下:

差分信号经过第一级SH电路,也就是采样保持电路,将输入模拟信号采样,并将其从进第一级stage电路,由stage电路中的子Sub-ADC量化,得到第一级的数字码,再将得到的数字码送入Sub-DAC,将其还原成模拟信号值,最后通过最初采样而来的模拟信号减去sub-DAC的输出值,所得到的信号幅度差再经过余数放大器放大4倍,传输给第二级stage电路,作为第二级的输入信号,以此类推,当信号经过所有5级stage电路后,会相应的得到所有的数字码,这些数字码再经过数字纠错逻辑和延迟逻辑单元,进而得到并行的12Bit的数字输出,完成一次模数转换。

由上述工作原理可知,流水线模数转化器由多级stage电路组成,每一级都由子Sub-ADC和子Sub-DAC以及余数放大器组成,尽管由系统决定了其中的Sub-ADC和子Sub-DAC的分辨率并不高,但多级stage并行工作的特性却使流水线模数转换器的速度得到了优化和提升,可以使ADC系统得到很高的分辨率和信号的转换速度。

2 模块设计

2.1MDAC模块设计

在流水线模数转换器的整个转换过程中,除了一开始的模拟信号需要经过SH电路进行采样保持外,并输入第一级stage电路意外,其余各级的输入信号都是由上一级的输入信号保持并减去上一级Sub-DAC的输出信号,并通过余数放大器的4倍增益得来的,实现数模转化,减法以及4倍放大的功能,统称为MDAC,MDAC由Sub-DAC,余数放大器,减法器组成,它使得各级在处理信号时互不干扰,相对工作独立,也是它的这种特性,使得整个流水线模数转换器系统得以较快的速度与较大的分辨率。由此可以看出,MDAC的性能将直接决定整个系统的性能,本设计MDAC采用了开关电容电路结构,

工作原理如下,因为本设计采用差分的结构,如下示意原理图采用单端示意来说明工作原理

如上图所示,S1,S2,S3,为mos开关,根据不同开关的闭合和断开, MDAC分为两个信号处理的阶段,分别为信号的采样与保持,

第一阶段,开始信号的采样,其中S1,S2,闭合,S3断开,在Cs和Cf上的电荷总数为Qvin=Vin·Cs+Vin·Cf,

第二阶段,将S1,S3闭合,S2断开,此时,信号输入为Vref信号,此时在Cs和Cf上的电荷总数为Qref= Vref·Cs+Vout·Cf,根据电荷守恒的原理,Qvin=Qref

可得以下结论

Vout=(1+)·Vin-Vref·

由于本设计采用的是2.5Bit的分级结构,即其中Cs=3Cf,这个比例实现了实现了减法器和对信号相减后差值放大4倍的功能。

2.2余数放大器设计

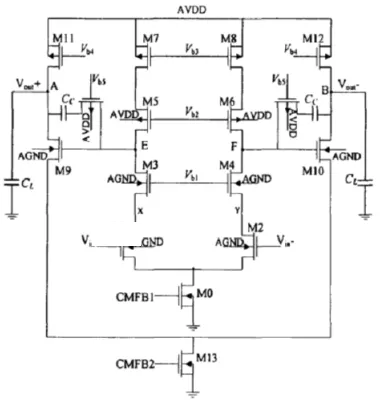

要实现MDAC的功能,其中的余数放大器是其中的关键,本系统对放大器的带宽,功耗,增益等性能指标有较高的要求, 所以对放大器的结构选取也提出了更高的要求,通过对目前常用的为套筒式共源共栅运算放大器,折叠式共源共栅运算放大器,两级型预算放大器,高增益运算放大器四种结构的性能比较,根据本系统的指标以及对运算放大器的各项关键指标的综合考虑,本设计选择如下结构,

本运算放大器主要由输入级,输出级和密勒补偿构成,其中,输入级采用了传统的套筒式结构,此结构有着高速低功耗,以及中等输出摆幅的特点,其中M1和M2为差分输入NMOS管,M0为电流镜像NMOS管,为整个输入级提供电流,M3-M4为NMOS负载管,M3-M8为PMOS负载管,M3-M8提高了M1和M2的输出阻抗,使其获得了较高增益,输出级采用了共源级输出以获得较大的电流驱动和输出摆幅,其中M9,M10为PMOS差分输出,密勒补偿电容Cc采用了零极点抵消的方法,使得运算放大器获得最大限度的单位增益带宽和相位裕度,本运算放大器的0dB带宽为101MHz, 相位裕度为52deg,另仿真电流为369uW,完全符合系统的指标要求

2.3子模数转换器(Sub-ADC)设计

子模数转换器存在于每一级stage电路模块中,其是将采样信号进行量化,再将量化过后的数字码输出到MDAC,再由MDAC进行处理,将其还原成模拟信号值,最后通过最初采样而来的模拟信号减去sub-DAC的输出值,所得到的信号幅度差再经过余数放大器放大4倍,传输给第二级stage电路,作为第二级的输入信号,Sub-ADC是通过比较器阵列来实现对采样信号的量化的,本文采用的2.5Bit的结构, 比较器阵列由6个比较器组成,分别对±Vref,±Vref,±Vref,6个固定电平进行比较,并将比较结果进行逻辑处理后,输出到MDAC,还原成模拟信号,再进行减法和放大的处理,由上述原理可知,比较器是子模数转换器的关键模块

2.3.1比较器模块设计

比较器一般常用的分为两种,一种是Latch比较器(非连续时间比较器),一种是运放型比较器(连续时间比较器),其中运放型比较器比较精度高,但速度较慢,且功耗较大,Latch比较器速度较快,功耗低,但精度不高,根据流水线模数转换器的原理,其对比较器的速度和功耗要求较高,但对精度要求不高,只需控制在150mV范围内即可,所以,本设计采用了Latch比较器的结构。

3 回片流片测试结果

本设计使用Cadence,Hspice电路设计软件,采用TSMC 0.18um工艺设计,并进行流片回片测试

流片回片测试结果

测试所需仪器

对信号发生器的需求:因为设计指标为12bit ADC ,所以信号源提供的信号信噪比必须要高于12bit,基于此要求的考虑,在本次回片测试中,本文选择了信号发生器:Agilent 81150,其可提供信噪比SNR为90dB,14bit精度的信号。

测试方法,由电压源提供3.3V电源电压,由信号发生器提供幅值为1V,频率为500k的正弦输入信号,AD采样频率4.8MHz,通过逻辑分析仪对回片的输出16384(2的14次方)个点进行采样记录,再将数据导入MATLAB进行fft的计算,得出以下结论

5 结论

本文采用了TSMC 0.18 CMOS工艺,设计了一款12bit,5M采样率的流水线模数转换器,电路中采用了分级2.5Bit结构,功耗为2mW,经流片回片测试,实际有效位为10.6bit,完全符合设计初衷

刘洋(1978.3.5)男,汉族,硕士,籍贯:辽宁凌海市,天津维晟微科技有限公司中级工程师,研究方向;自动化

A 12 bit pipeline module is installed in the research and design

Liu Yang

(Tianjin d sheng micro technology co.,LTD,300457)

This paper study and design a kind of low power consumption structure of 12 bit pipeline adc, the adopted TSMC 0.18 um process design, single power supply voltage of 3.3 V,5 MHZ sampling rate and dynamic range of 1 V, INL 0.5 LSB, DNL is 2 LSB, through detailed analysis of the circuit principle and software simulation, Cadence and flow testing, performance meet the design intent.

Pipeline ADC (Pipeline ADC);child digital-to-analog converters(Sub - DAC);analog-to-digital converter(ADC);Sub - MDAC remainder amplifier

[1]李福乐.适宜于系统集成的高速高精度模数转换电路设计技术研究.清华大学博士学位论文,2003.

[2]龚川 CMOS图像传感器中高速,低功耗 Pipelined ADC设计与优化.天津大学硕士学位论文,2006.