基于FPGA的高速USB协议分析仪的设计

张静 叶小芹

(河海大学文天学院 安徽马鞍山 243031)

基于FPGA的高速USB协议分析仪的设计

张静叶小芹

(河海大学文天学院安徽马鞍山243031)

USB协议分析仪是一种用于分析和监控USB总线协议的仪器,它包括采集主机及分析软件两个部分。可用于USB驱动开发、协议栈调试、协议符合性测试及总线性能分析等多个方面。针对现有的分析仪价格昂贵、采样丢包和无法进行长时间采集数据等问题,设计了一种基于FPGA的高速USB协议分析仪,实现了对高速、全速和低速差分信号的实时采样和分析,利用硬件的并发处理特性克服了采样丢包的问题,而且内嵌大容量SDRAM,使得长时间采集数据成为可能,并且设计成本低。

USB协议分析仪;FPGA;通用串行总线;USB控制器

USB总线由于其通用性、高速性和即插即用等特性,成为计算机不可或缺的接口[1]。USB总线采用串行的一对差分线进行信号传输,并采用NRZI进行编码,加上USB协议本身的复杂性。使得开发USB主机控制器和USB设备的难度较大,周期较长。而且USB设备种类繁多,其测试和后期的维修问题也日益突出[2]。而且现有的USB高速协议分析仪存在价格昂贵和采样丢包的问题,很难满足开发的需求。

本文设计了一种高速USB协议分析仪,在不影响主机和被测设备通信的前提下,捕获USB总线的信号,重新打包并保存在SDRAM存储器中。由MCU控制USB控制器,通过DMA方式,将SDRAM中保存的数据上传至计算机,利用软件将上传的数据进行解析并显示出来。当监控主机的上传速率低于被监测的外设时,数据可以暂存SDRAM中,等监控主机空闲时上传数据,这样可以防止丢包。文献[3]中采用高速差分放大器AD8352对差分信号进行处理后由USB物理层接口芯片进行采样,主要为了引入大阻抗,以免干扰要采集的总线信号。本文直接采用USB3500芯片,并将之设置为无负载模式,便可实现上述文中要达到的目的,且硬件电路更简单,更稳定。而且文献[3]选用8K*4字节的FIFO作为数据缓冲,缓冲能力十分有限,很容易丢失数据。而广州致远电子有限公司独立设计的USB分析仪最大只能存储512M字节的数据,本文由于采用了动态存储的设计[4],适合长时间数据采集,存储数据的大小并不受限制,具有明显的优势。

一、系统结构设计

系统框图如图1所示,通过USB3500芯片采集数据,将采集到的经过NRZI编码的串行数据去位填充,转换成并行数据输入到FPGA中。在FPGA中将数据重新打包,并进行CRC检验,将数据的CRC等信息加入到新的包中,然后保存在外部的SDRAM中,FPGA控制USB控制器通过DMA的方式[5-7],将SDRAM中的数据读到USB控制器的内部FIFO中。ISP1582内部具有8KB的缓冲空间,并支持DMA模式。

图1 系统结构框图

二、关键技术

(一)数据采集。数据采集端采用USB物理层芯片USB3500进行采集,USB3500可配置成高速、全速和低速模式。所以该分析仪可以检测这三种类型的外设,并将外设类型上传给监控主机。FPGA中的逻辑可以自动判断被监测的设备的类型。数据采集的关键点是将USB3500的DP和DM上的所有负载全部去除,以免干扰被监测设备与主机之间通信。具体方式是将OPMODE引脚的状态设置为01,表示移除所有终端负载。USB3500的接口符合UTMI协议,无论USB3500设置成高速、全速或低速模式,USB3500的输出时钟CLKOUT一直是60MHz,FPGA利用该时钟采样输入的数据,只有RXVALID引脚有效时,采集到的数据才有效。时序图如图2所示。USB3500的LINESTATE引脚输出总线上的状态,根据该引脚获取复位、挂起和唤醒等信息。

图2 USB3500输出信号时序图

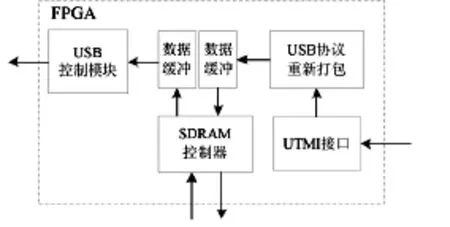

(二)FPGA控制逻辑设计。FPGA的控制逻辑主要划分为四个模块,分别为UTMI接口模块、数据打包模块、SDRAM控制器模块和USB控制器控制模块,结构框图如图3所示。

图3 FPGA内部逻辑框图

UTMI接口模块的功能是采集USB3500输出的数据,包括总线状态和数据,同时通过采集总线的状态来判断外设类型,高速外设接入的时候和主机有一个握手过程,如果能检测到握手信号,则表明是高速外设。全速外设和低速的空闲时的线上状态不一样来区分。当获取到外设类型后,将USB3500的引脚(XCVRSEL、TERMSEL)配置为相应的状态。

数据打包模块的功能是计算数据的CRC状态,包的大小以及包与包之间的时间间隔信息。并将这些信息和数据重新打包上传给监控主机,便于分析。

SDRAM控制器模块的功能是将数据打包模块的数据写入到外部的SDRAM存储器中,同时将该数据读出发送给外部的USB控制器,并完成SDRAM的刷新。由于SDRAM在刷新的时候,禁止任何写入和读出,所以前后加缓存,以便于在SDRAM刷新的时候暂存数据[8-10]。

USB控制模块主要完成USB分析仪接入的时候的枚举工作,同时当监控主机请求数据的时候,利用SDRAM控制器模块从SDRAM中读取数据,通过DMA接口写入到ISP1582内置的缓存空间,由USB控制器上传至监控主机。

三、系统实现及仿真

系统采用ALTERA公司CYCLONE系列FPGA芯片EP1C12,内置约24KB的SRAM和12000左右的逻辑单元,符合用于设计该分析仪的要求,而且成本较低。USB控制器采用恩智浦的ISP1582芯片,利用FPGA对其进行配置即可,缩短了开发周期,保证系统的稳定性。采用海力士的SDRAM芯片,容量为256Mbit。整个系统结构简单,易于实现。

采用QuartusII结合modelsim仿真软件进行仿真。图4的仿真波形是数据采集端的仿真,采集到的USB3500输出的数据,然后加上包与包之间的间隔时间,以及整个包的长度大小,然后写入到SRAM中,这样就完成了协议的打包。图5给出的波形是将SRAM中的数据写入SDRAM中,图中可以看出SDRAM的刷新时序以及读写时序,采用的是页突发模式进行的读写操作。

本文采用两种方式对系统进行了测试。方式一采用两台windows计算机,均配有高速USB主机,分别作为监控主机和测试主机,采用高速U盘作为被测设备。当高速U盘复制文件的速度为21MBps时,监控主机的速度为24MBps,分析可知监控主机的数据不仅包含被测设备的数据流,还存在该HUB下其他设备的部分数据,且上传至监控主机的数据是经过重新打包,因此数据量比较大。这种情况下,SDRAM的利用率比较低,因为采集到的数据都及时上传至监控主机。方式二采用一台装有windows系统并含有高速USB主机的计算机,同时作为监控主机和测试主机,被测设备同样为高速U盘。这种情况下,偶尔会出现监控主机的速率低于被测设备,主要因为此时监控所得到的总线资源较少,数据会在SDRAM中堆积,此时该方案的优势就比较明显,数据不会丢失。由此可见,本文设计的高速USB分析仪有效地解决了采样丢包的情况。

图4 数据打包时序图

图5 SDRAM控制时序图

四、结语

本文设计的高速USB协议分析仪,利用USB物理层芯片USB3500进行数据采集,硬件电路简单。为了防止监控主机的上传速率低于被监测的外设,采用一个大容量的SDRAM作为缓存,有效得防止了丢包的情况,同时利用FPGA的并行处理特性,保证了采集数据的准确性。本系统具有硬件电路简单,成本较低的特点,为USB相关设备的开发、调试和测试提供了便利的途径。

[1]刘爱东,张永强,杨健,等.USB设备互连通信协议设计[J].电光与控制,2011,18(1):69-72.

[2]高强,冉全,罗媛媛,等.USB总线协议层的研究[J].软件导刊,2010,9(10):28-30.

[3]胡伟,张新家,李美峰,等.基于FPGA的USB2.0协议分析仪设计[J].计算机测量与控制,2008,16(9):1353-1355.

[4]吕晖,谢向辉.同时基于预知信息和预测机制的SDRAM动态页策略[J].计算机工程与科学,2015,37(12):2208-2215.

[5]李宝将,张小军,田应洪,等.USB接口的FPGA实现[J].微电子学,2010,40(5):689-692.

[6]冉全,钱环环.基于FPGA的USB控制器IP核设计[J].兵工自动化,2008,27(4):88-89.

[7]Tang D.USB controller with intelligent transmission mode switching function and the operating method thereof:U.S.Patent 7,185,132[P].2007-02-27.

[8]张富贵,陈宇熠,吴雪梅,等.SDRAM控制器的FPGA设计及验证[J].中国农机化学报,2013,34(5):238-242.

[9]任兴晖,陈永超,石浩,等.基于FPGA的SDRAM控制器的设计[J].电子质量,2014(1):11-15.

[10]于明,高剑.SDRAM控制器的设计与实现[J].电子测试,2014(1):63-67.

[责任编辑郑丽娟]

Design of High Speed USB Protocol Analyzer Based on FPGA

Zhang Jing Ye Xiaoqin

(Hohai University,Ma'anshan,Anhui 243031)

A USB protocol analyzer is an instrument for analysis and monitoring of the USB bus protocol. It includes collection host and analysis software.It can be used for the USB driver development and debug the protocol stacks,test the protocol conformance and bus performance analysis of several aspects.For existing analyzer is expensive and sampling problem such as packet loss,we designed a high-speed USB protocol analyzer based on FPGA,which realized with high speed,full speed and low speed difference signal real-time sampling and analysis,using the concurrent processing of hardware features overcome the problem of the sample packet loss,and embedded large-capacity SDRAM,making it possible to collect data for a long time,and lower design costs.

USB protocol analyzer;FPGA;universal serial bus;USB controller

TP393

A

2095-0438(2016)09-0152-03

2016-05-10

张静(1984-),女,江苏徐州人,河海大学文天学院助教,硕士,研究方向:数字信号处理。