简单任意波形发生器设计

王丽君,李 萌

(1.南华大学电气工程学院,湖南 衡阳 421001;2.南华大学计算机科学与技术学院,湖南 衡阳 421001)

简单任意波形发生器设计

王丽君1,李萌2

(1.南华大学电气工程学院,湖南 衡阳 421001;2.南华大学计算机科学与技术学院,湖南 衡阳 421001)

介绍了一种基于FPGA(在系统可编程门阵列)的简单任意波形发生器设计方法,可实现对上位机仿真软件生成的任意波形数据的完整输出。输出波形的频率、相位和幅度均可任意调节。该设计操作简易,调节方便,输出波形较为理想,是一种易于实现、实用性强、成本低廉的信号生成方法。

FPGA;任意波形;频率;相位

信号发生器是一种能提供各种频率、波形和输出电平电信号的设备。一般可分为函数信号发生器和任意波形发生器,在生产实践、电路实验、设备检测中起着不可或缺的作用。传统的信号发生器一般体积较大,价格昂贵,生产过程复杂,最重要的是不具备用户自定义和编程功能。本设计方案中,只要借助现场可编程门阵列(Field-Programmable Gate Array,FPGA),利用合适的软件平台,就可以随心所欲地根据自己的需要,设计出用户自定义的信号发生器。输出波形可任意更改,重复开发,具有一定的经济价值。

1 系统整体设计

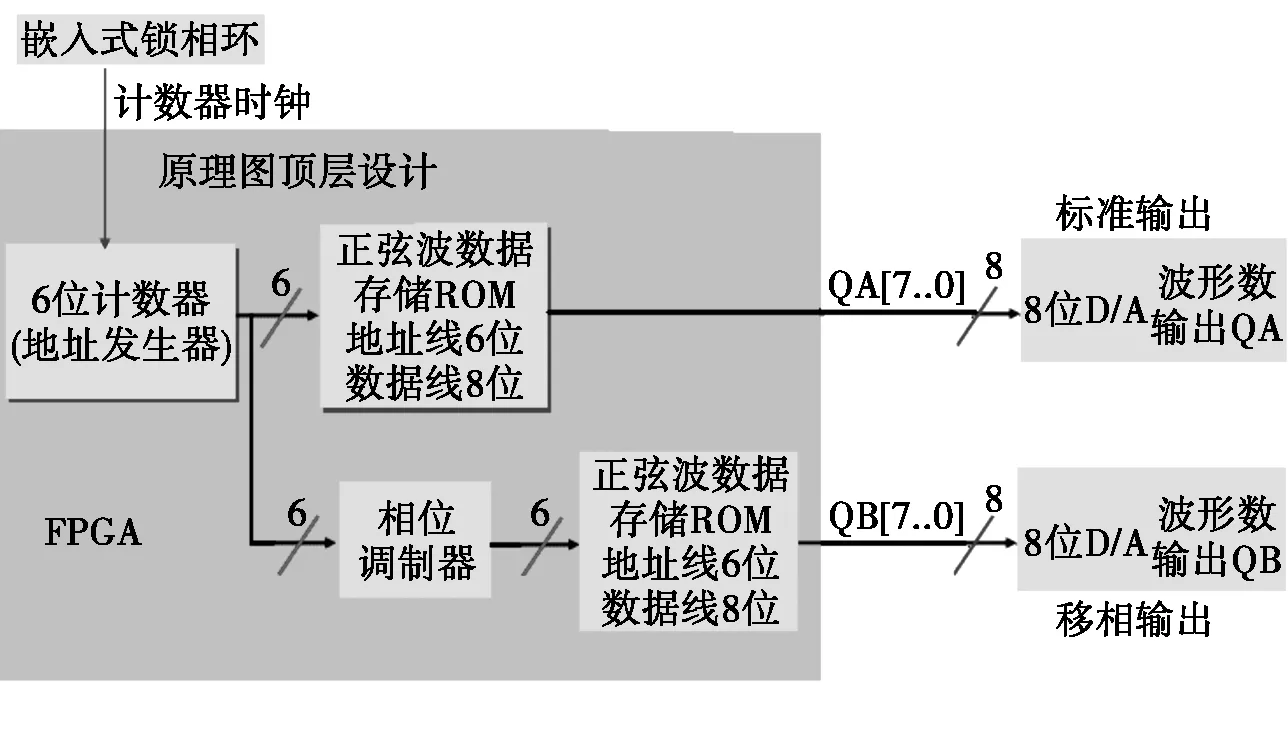

本文以简易正弦信号发生器为例,介绍任意波形发生器的实现方式。简易正弦信号发生器主要由三部分构成:数据计数器或地址发生器、数据ROM和D/A[1]。图1是此信号发生器结构图。原理图顶层设计包含前两部分,在FPGA中实现,软件平台采用Quartus II 9.0。波形输出部分由外部的

D/A转换模块和放大模块构成。

图1 简易正弦信号发生器结构图

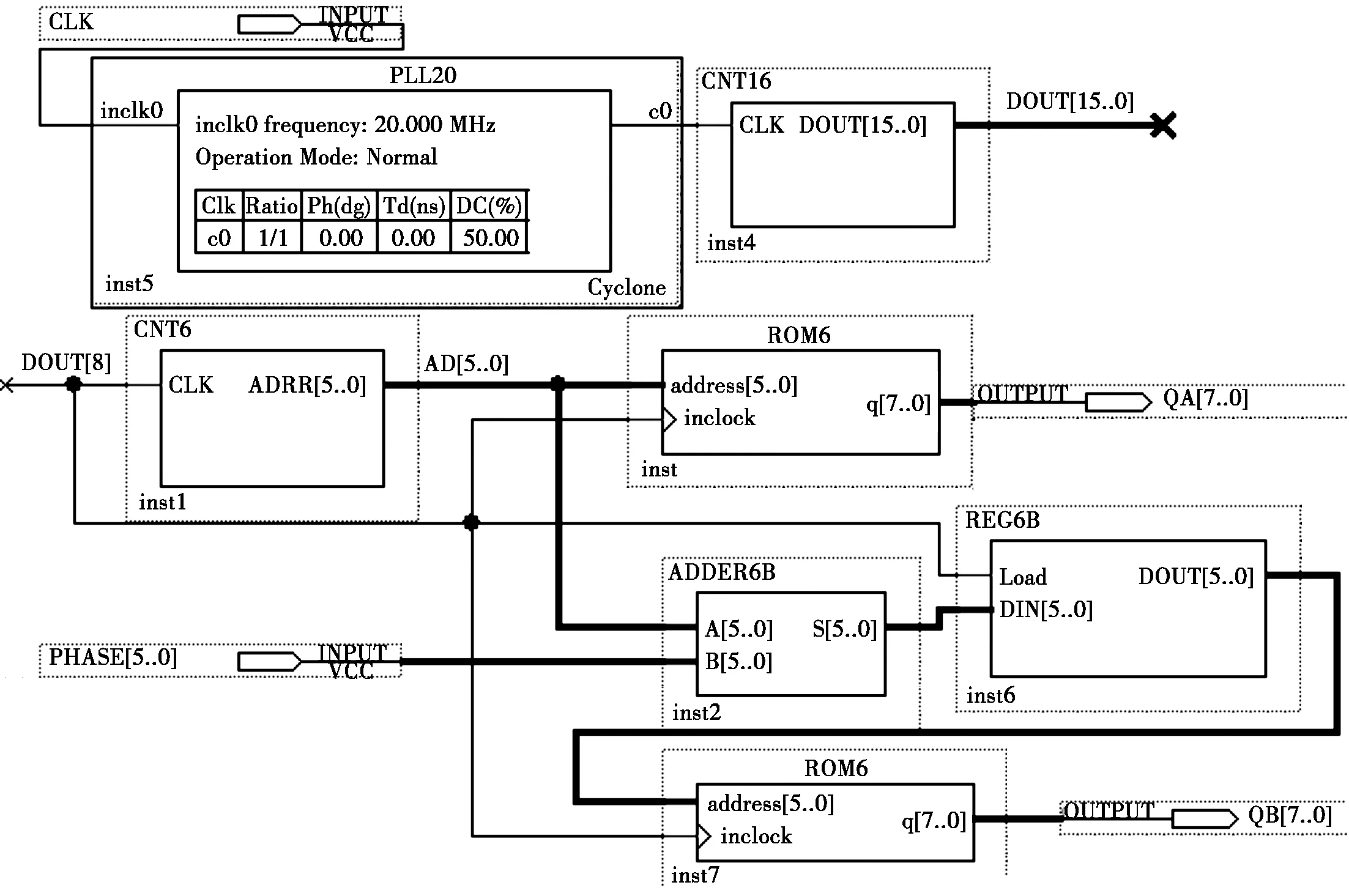

FPGA内部的原理图顶层设计如图2所示。QA[7..0]和QB[7..0]分别为标准正弦波和移相正弦波的波形数据输出。

图2 系统设计原理图

1.1频率可调地址发生器

首先生成六位二进制计数器的VHDL程序。

程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT6 IS

PORT (CLK,RST,EN: IN STD_LOGIC;

ADRR : OUT STD_LOGIC_VECTOR(5 DOWNTO 0) );

END CNT6;

ARCHITECTURE behav OF CNT6 IS

BEGIN

PROCESS(CLK, RST, EN)

VARIABLE CQI:

STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

IF RST = ′1′ THEN

CQI := (OTHERS =>′0′) ;

—计数器异步复位

ELSIF CLK′EVENT AND CLK=′1′ THEN

—检测时钟上升沿

IF EN = ′1′ THEN

—检测是否允许计数(同步使能)

CQI := CQI + 1;

—允许计数

END IF;

END IF;

ADRR<=CQI;

END PROCESS;

END behav;

将上面的程序转换成原理图,就是图2中的CNT6计数器模块,其输出DARR[5..0]作为存放正弦波数据的ROM的地址[2]。锁相环PLL20可以使输出的时钟保持稳定,输入时钟CLK通过锁相环PLL20后,作为16位计数器CNT16的计数时钟,取出CNT16输出的其中一位作为地址发生器CNT6的计数输入时钟f0(图2中选取了DOUT[8]),这样选取的位数不一样,地址发生器的计数时钟频率就不一样。

假设地址发生器的地址线为6位,则ROM中可存储64个正弦波数据。正弦波数据可由上位机波形发生器产生。地址发生器每计64个数,可以输出一个完整的正弦波。这样,D/A波形输出的频率f与地址发生器的计数时钟频率f0之间的关系为:f=f0/64。由此可知,通过取用CNT16不同的位输出作为地址发生器的计数时钟,可以实现D/A输出波形的频率调节。

1.2实现移相

ROM6模块中存放着正弦波的数据点(以64个为例),在64个计数时钟周期后,输出可构成一个完整的正弦波数据点,标准正弦数据点输出以QA[7..0]表示。加法器模块ADDER6B和寄存器模块REG6B共同构成相位调制器[3],PHASE[5..0]为相位控制字,控制相移的大小,由外部输入。QB[7..0]为移相正弦波数据点输出[4]。

1.3配置编程

将顶层原理图部分生成配置文件配置到配置芯片中,每次上电时,配置文件会自动载入到FPGA中,脱离上位机独立运行[5],这样利用一片FPGA芯片和一片配置芯片,就可完成两路正弦波数据点输出部分的设计,使得波形发生器的体积大为减小。

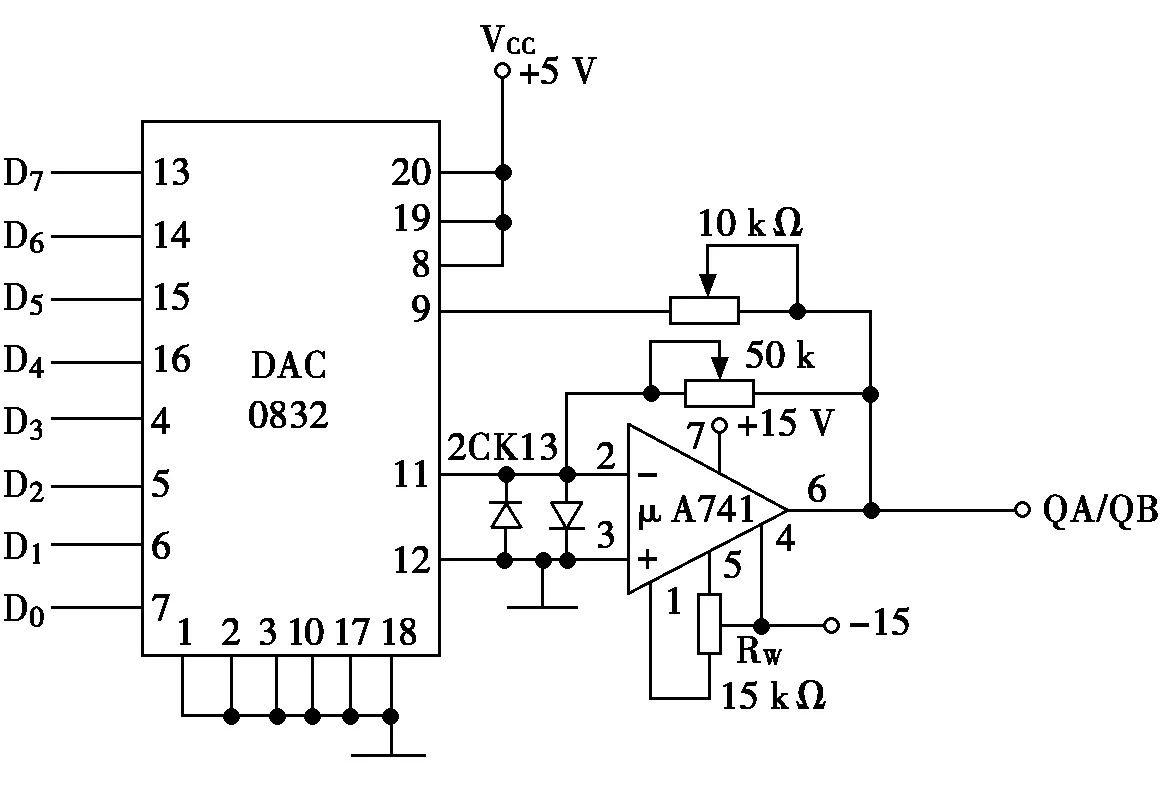

1.4幅度可调数模转换D/A

数模转换在FPGA的外部实现。主要由DAC0832和运放μA741构成[6],如图3所示。若要实现移相,需要两路相同的D/A模块。DAC0832的8位数字输入跟ROM6的输出QA[7..0]和QB[7..0]相连,QA为标准正弦波形模拟输出,QB为移相正弦波形模拟输出。通过调节电位器的大小,可以改变输出正弦波的幅度。

图3 数模转换D/A模块

移相正弦信号发生器两路模拟信号输出如图4所示。

图4 移相正弦信号发生器两路输出波形

2 任意波形发生器

以上介绍的是正弦波发生器,其数据ROM中存放的是正弦波的数据点。利用波形生成软件,可以生成方波、三角波的数据点,也可自定义生成任意波形的数据点,存入到数据存储ROM中,即可成为任意波形发生器,方便快捷,无需改变硬件结构。

3 结论

本方案利用FPGA芯片,借助EDA软件平台完成任意波形发生器的大部分设计,通过软件编程,对芯片的硬件结构进行重构,即利用软件来实现硬件功能,从而使得硬件的设计可以如同软件设计那样方便快捷。

[1]户永清.基于DDS的简易正弦信号发生器设计[J].四川文理学院学报(自然科学),2009,19(5):37-39.

[2]曹郑蛟.基于FPGA的DDS信号发生器设计[J].计算机测量与控制,2011,19(12):3175-3177.

[3]余勇,郑小林.基于FPGA的DDS正弦信号发生器的设计与实现[J].电子器件,2005,28(3):596-599.

[4]肖炎根.基于DDS的数字移相正弦信号发生器的设计[J].设计参考,2009,11(12):53-55.

[5]杨金孝.基于串口通信的FPGA配置控制方法及实现[J].计算机测量与控制,2011,19(4):848-850.

[6]鲁杰爽.采用DAC0832的数模转换设计与调试[J].PLC·变频器·计算机,2012(1):41-43.

Simple Design of Arbitrary Waveform Generator

Wang Lijun1, Li Meng2

(1.SchoolofElectricEngineering,UniversityofSouthChina,Hengyang,Hunan421001,China;2.SchoolofComputerScienceandTechnology,UniversityofSouthChina,Hengyang,Hunan421001,China)

The article introduces a simple design of arbitrary waveform generator based on Field-Programmable Gate Array. It can outputs arbitrary waveform data generated by upper computer. The frequency, phase position and amplitude of output waveform can be adjusted arbitrarily. The design is easy to be used and adjusted, and its output waveform is comparatively ideal. It’s a simple, practical and low-cost method to produce signal.

FPGA; arbitrary waveform; frequency; phase position

2016-05-11

王丽君(1979- ),女,讲师,硕士,主要研究方向:电子信息。

1674- 4578(2016)04- 0042- 03

TP 2;TM935.2

A