大容量弹载数据记录器的设计与实现

温建飞,岳凤英,李永红(.中北大学计算机与控制学院,太原03005;.中北大学仪器与电子学院,太原03005)

大容量弹载数据记录器的设计与实现

温建飞1,岳凤英2*,李永红2

(1.中北大学计算机与控制学院,太原030051;2.中北大学仪器与电子学院,太原030051)

提出了一种大容量弹载数据记录器的设计方案,该方案主要完成3路高速图像数据的接收,每个通道的数据带宽为每秒150Mbyte/s,存储容量为128 Gbyte。设计选用Xilinx公司的FPGA作为主控制器,完成对高速数据的接收,缓存和存储。接收单元采用FPGA内部集成的高速串行收发器RocketIOGTP,单个链路的数据接收速率为3.125Gbyte/s;缓存单元采用两片DDR2 SDRAM芯片对接收到的高速数据进行乒乓缓存;存储单元采用32片NAND FLASH构成存储阵列,对缓存后的数据进行存储。同时,该记录器能够对存储的数据进行事后读取并进行分析。

大容量;高速;RocketIOGTP;DDR2 SDRAM;乒乓缓存

数字化信息时代对高速信息的要求越来越高,尤其是在军事航天领域。在航天领域为了了解飞行器舱内的情况,飞行器在飞行过程中需要对舱内环境进行检测并记录,事后通过分析记录器中的数据,其结果可以为下次飞行做好准备工作。高速数据记录器具有较好的发展前景,除了能够满足星载、弹载等军事领域的数据记录要求外,还可以扩展到其他工业和商业领域。然而,随着需要记录的数据信息量和数据带宽不断增大,需要设计一种具有接收带宽高、容量大、体积小、实时缓存存储的数据记录器装置。

近年来,随着对低功耗、高密度和高可靠性的固态存储器的需求,采用NAND FLASH存储器的数据记录器广泛地应用于各个领域。NAND FLASH存储器主要有以下特点:

(1)功耗低、成本低、存储密度高。

(2)读写速度高、使用寿命长、数据存储时间长。

(3)工作环境温度范围较大。

1 系统整体组成部分

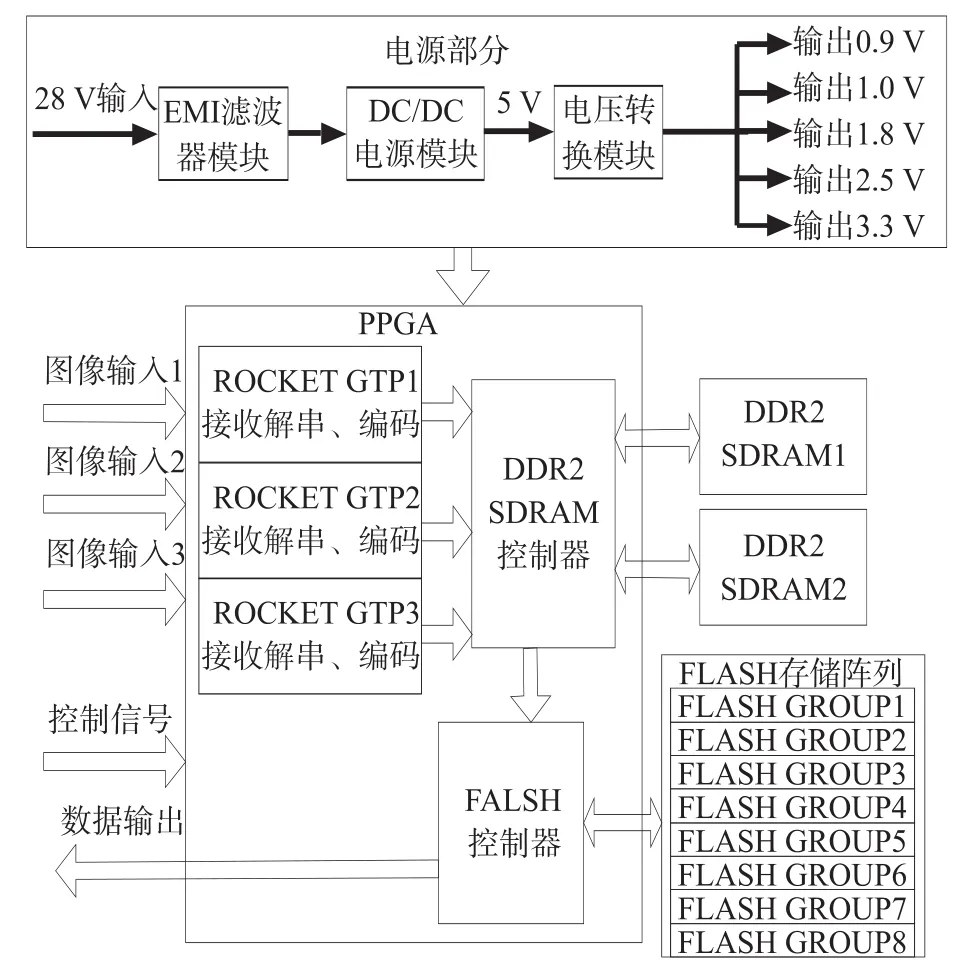

大容量弹载数据记录器主要完成飞行器在飞行过程中对3路高速图像数据信息进行实时接收、编码和记录的任务,飞行任务完成之后,用配套测试台读取记录器中的数据,最后由上位机软件对数据进行分析和处理。测试台和计算机之间通过USB3.0接口进行通讯,上位机软件完成下发指令、确认数据、读取数据和分析数据的任务。记录器与测试台的系统整体组成框图如图1所示。

图1 记录器与测试台系统整体组成框图

该记录器装置主要记录高速图像数据,根据任务的要求实现记录器的整体功能,记录器的主要技术指标如下所示:

(1)飞行器系统为记录器装置提供+28 V的工作电压,记录器的功耗不超过28W。

(2)采集存储三路高速图像数据,LVDS接口,码率为393.216Mbit/s,3路图像的像素点均为640× 480,每行的像素点为640个,每列的像素点为480个,图像速率每秒80副。

(3)记录器容量要求不小于100Gbyte,支持连续存储和超阈值存储两种模式。

2 总体方案设计

从整体功能上可以把大容量高速数据记录器分为4个部分:系统电源单元、高速数据接收单元、数据缓存单元和数据存储单元,总体功能组成原理框图如图2所示。

图2 功能原理框图

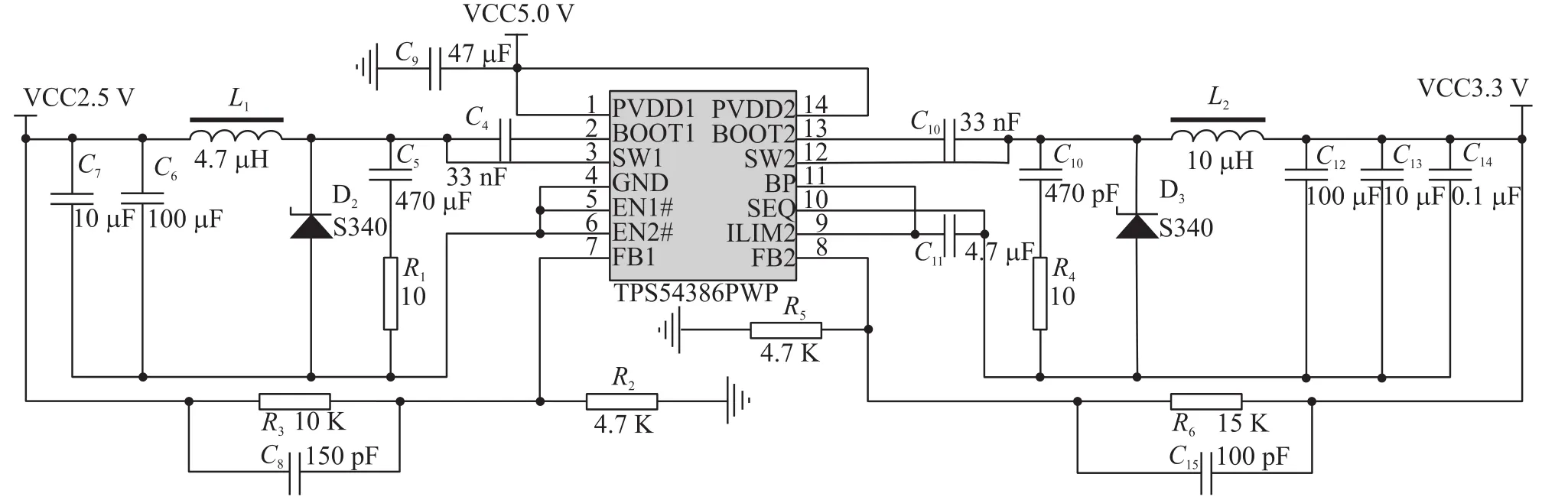

2.1系统电源的设计

由于飞行器系统供电为28 V,而记录器所需要的电源种类较多。主要有:DDR2SDRAM需要0.9V 和1.8V直流稳压电源;FLASH需要3.3 V直流稳压电源;主控芯片Virtex-5系列FPGA可兼容多种I/O电压,内核和I/O单独供电,内核供电电压为1.0 V,RocketIOGTP高速串行收发器供电电压2.5 V。因此需要电源单元对输入电源进行专门的转换和处理才能使用。通过测试,系统功耗为21W,满足系统需求。电源电路设计原理图如图3所示。

图3 电源转换模块原理图

电源单元主要由EMI(Electromagnetic Interference)滤波模块、DC-DC(电源转换)模块以及电压转换模块构成。EMI滤波模块主要完成对电压进行低通滤波,DC-DC模块主要实现对输入电压进行隔离,可以避免外系统对电源的干扰,电压转换模块主要实现各个系统单元的供电需求(这里选用的是TI公司的TPS54386 PWP芯片,最大可以提供6A的电流,满足系统工作需求)。

2.2高速数据接收单元

高速数据接收单元由FPGA内部集成的高速串行收发器RocketIO GTP接收数据,由于RocketIO GTP对参考时钟以及供电要求较为苛刻,因此设计中分别使用ADI公司的AD9520专用时钟芯片提供时钟和TI公司的TPS54810单独提供电源。

2.3数据缓存单元

数据缓存单元使用的是流水线设计,这样可以充分利用电路之间的等待时间,使电路运行的更快更稳定。

2.4数据存储单元

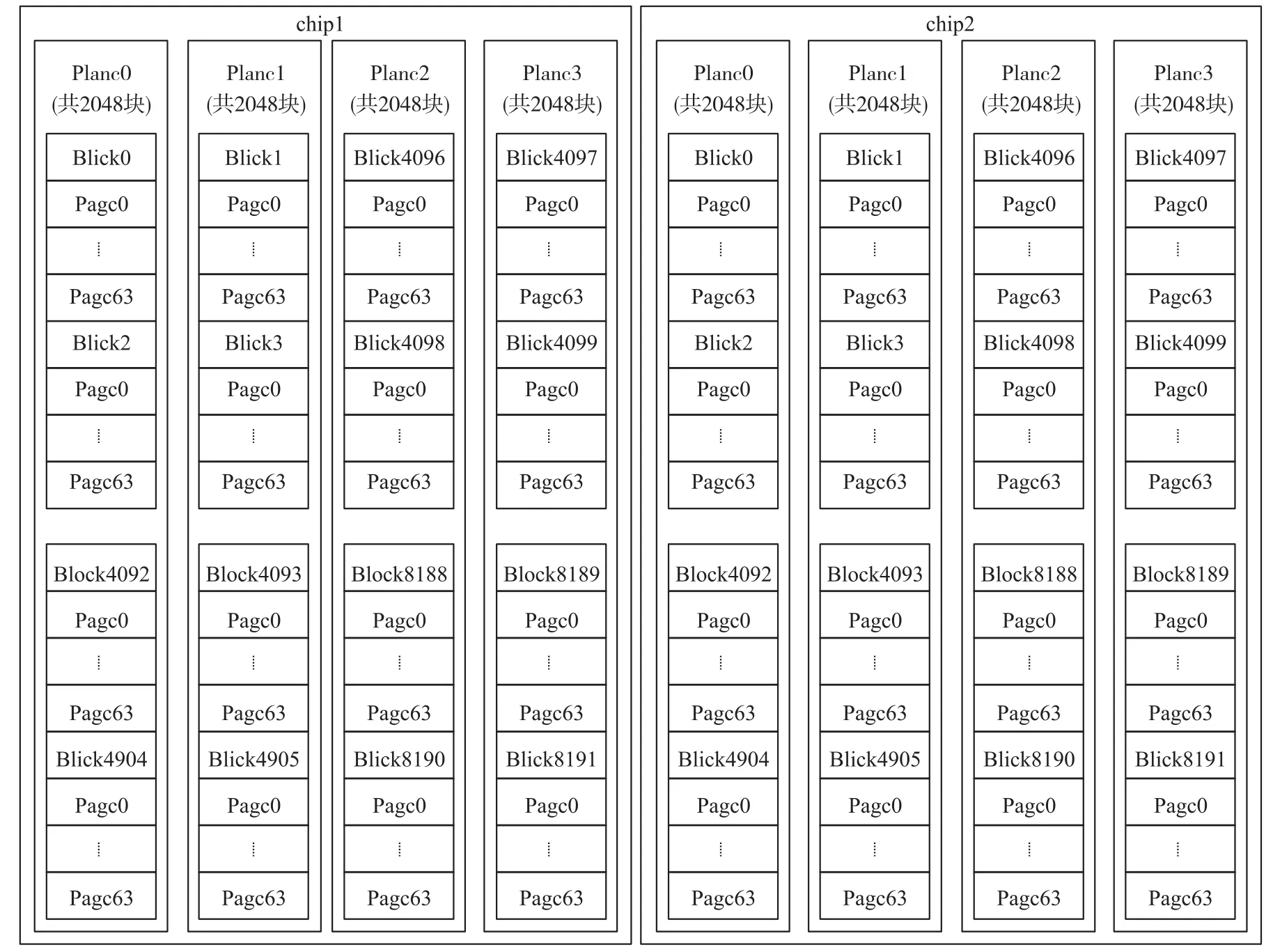

存储单元由32片K9WBG08U1M组成存储阵列,分为4组,每组由8片组成。实现对数据的大容量存储。

3 关键问题的解决

3.1高速收发器的设计

Xilinx公司针对高速数据传输的需求,提出了以RocketIO GTP(高速数据收发模块)为核心的解决方案,在其旗下的部分Virtex-5系列及更高级版本的FPGA内部集成了高速数据收发模块,RocketIO GTP采用了CML、CDR、8B/10 B线路编码和预加重等技术,最大限度的减小信号的衰减、时钟扭曲,进一步提高了数据传输速率,最高可达3.125 Gbit/s。由于 LVDS图像数据的速率为 393.216 Mbit/s,实际速率于此基本吻合(实测速率为389 Mbit/s~395Mbit/s)。因此,接收器完全能够满足此图像数据的接收,基于以上优点,本设计数据接收单元采用RocketIOGTP收发器。

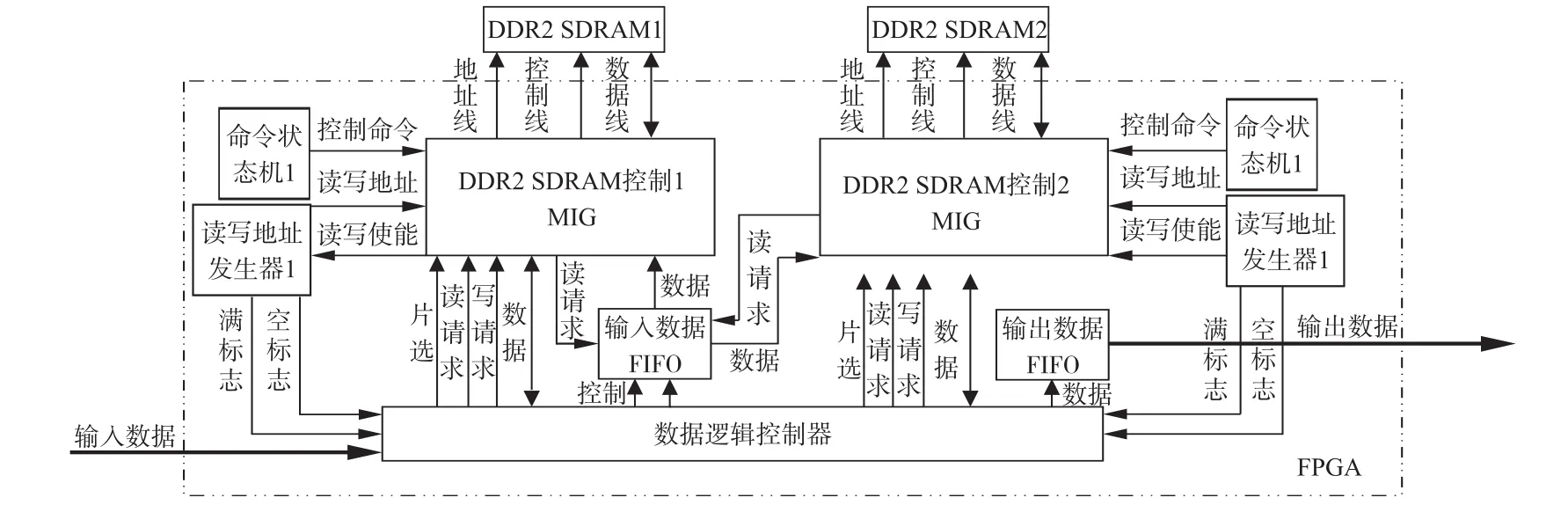

3.2DDR2 SDRAM乒乓缓存单元设计与仿真

图4为乒乓缓存的结构图,其具体工作流程如下:数据逻辑控制器完成对整个缓存数据的接收和合理化分配,系统上电后,DDR2 SDRAM控制器对DDR2 SDRAM进行初始化,初始化完成后DDR2SDRAM处于空闲状态,当数据逻辑控制器接收到数据时,片选DDR2SDRAM1的同时发送写请求,并将数据写入输入数据FIFO中,等待DDR2 SDRAM1写应答,DDR2 SDRAM1控制器收到写应答后使能读写地址发生器1,发送DDR2SDRAM1的写地址命令,同时开始计数,控制1读取输入FIFO中的数据,将输入数据写入到DDR2 SDRAM1中,当达到设定的存储容量时给出DDR2SDRAM1满信号。数据逻辑控制器判断DDR2 SDRAM1满标志有效时使能DDR2SDRAM1读请求,同时使能DDR2SDRAM2写请求,DDR2SDRAM1控制器写地址计数器1清零,等待DDR2SDRAM1读应答,收到应答后使能读写地址发生器1,读取DDR2 SDRAM1中的数据送入到存储单元进行存储。当DDR2 SDRAM1读取完成后等待DDR2 SDRAM2写满,当DDR2SDRAM2写满后将接收到的数据写入到DDR2SDRAM1中,同时读出DDR2SDRAM2中的数据送入到存储单元中进行存储。从外部看输入输出的数据是连续的,能够避免数据丢失,实现数据的无缝缓冲。

图5为乒乓缓存模块在modelsim中的仿真结果。

图4 DDR2 SDRAM乒乓缓存结构图

图5 DDR2_M odule读写时序仿真图

3.3存储单元模块的设计

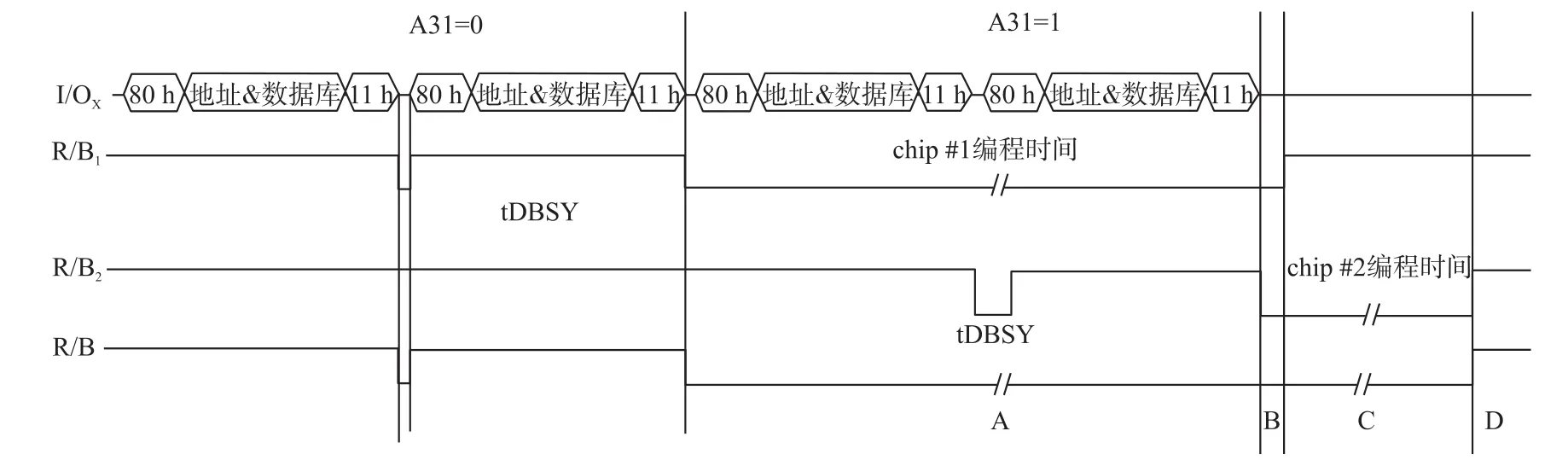

由于K9WBG08U1M的最小读写时钟周期是25 ns,单片的数据端口位宽为8 bit,所以极限读写速度为40Mbyte/s,加上写入命令和地址也需要时间,实际的读写速度在30Mbyte/s。由于接收端接收到的数据平均速度为 150 Mbyte/s,所以单片K9WBG08U1M不能实现对数据的实时存储,需要对8片K9WBG08U1M进行并行操作才能满足要求,存储单元的平均读写速度大约是240Mbyte/s,完全满足存储要求。接收到的数据要经过缓存单元进行缓存,存储单元需要从缓存单元中读出数据进行存储。缓存单元和存储单元的工作时钟是相互独立的,这就需要进行跨时域处理,利用FPGA内部的FIFO是一种常用的处理跨时域方法。文中的跨时域处理就采用此方法。图6和图7分别是K9WBG08U1M芯片的内部结构图以及交叉双平面编程的读写时序图。

图6 K 9WBG08U1M内部结构图

图7 交叉双平面编程时序图

当 plane0写入数据后进入编程时,此时不用等待 plane0编程结束,就可以对 plane1、plane2和plane3进行编程操作。由于使用交叉双平面编程方法省去了大量的页编程等待时间,从而提高了写入速度。经实际反复测试单片 K9WBG08U1M的最高写入速度为30 Mbyte/ s。存储单元存储数据时是对8片K9WBG08U1M进行同样的写操作,整体写入速度约为240 Mbyte/s。交叉双平面编程方式能够满足设计的要求。

4 系统功能测试

测试台USB3.0接口芯片选用的是赛普拉斯半导体公司的型号为CYUSB3014-BZX的芯片。CYUSB3014-BZX集成了USB3.0物理层和32 bit ARM926EJ-S微处理器,采用一种巧妙的架构,使CYUSB3014-BZX芯片和计算机的平均数据传输速度最高可达320Mbyte/s。选用CYUSB3014-BZX作为USB3.0接口芯片完全能够胜任测试工作。

下发数据的速度约为180Mbyte/s,满足测试要求,上位机软件下发数据和上传数据的界面如图8所示。

上位机软件下送数据的帧格式为:前2个字节为帧头“14 6F”,中间为数据体,从“01~FF”共255个字节,在数据体后有4个字节的帧计数,最后是2个字节的帧尾“EB 90”。每帧数据共263个字节,部分数据以及分析结果如图9所示。

图8 上位机下发和上传数据界面

图9 下发数据帧格式以及数据分析结果

发送结束之后点击上位机软件上的“读取数据”按钮,设备接收到读取命令之后开始读出NAND FLASH存储阵列中的数据并发送给CYUSB3014-BZX并进行上传,同时将数据保存至计算机的硬盘里。

数据读取结束之后点击上位机软件上的“数据分析”按钮即可对数据进行检测和分析。

共读取了2 048Mbyte数据,总帧数为十六进制的7C97D9。经检测没有出误码和数据丢失情况,数据完全正确。

5 总结

本设计创新点在于,针对高速数据接收要求,使用Virtex-5系列FPGA内部集成的高速串行收发器RocketIOGTP作为高速数据接收单元,内部MIG控制器操作2片DDR2 SDRAM构成的乒乓缓存为缓存单元,32片NAND FLASH构成的存储阵列为存储单元来接收存储高速数据的总体方案设计。文中对大容量高速数据记录器的3个主要单元的工作原理做了详细的介绍,对接口复杂的RocketIOGTP收发器和MIG控制器进行封装,简化了操作的复杂性,对封装的模块进行仿真,验证其正确性。高速数据的存储因受到NAND FLASH工作频率的限制,因此本设计对存储阵列的操作采用并行处理的方法,通过增加数据总线位宽的方法来提高存储速度。

[1] 刘波.基于闭环自检和双备份的数据存储器设计与实现[D].太原:中北大学,2011.

[2] 储成群.基于LVDS接口的高速数据记录器的设计[D].太原:中北大学,2011

[3] 姚宗.某型固态数据记录器的研制[D].太原:中北大学,2010.

[4] 胡惠.多通道超高速数据采集与记录系统的设计与实现[D].南京:南京理工大学.2010.

[5] 孙航,胡灵博,,等.Xilinx可编程逻辑器件应用与系统设计[M].北京:电子工业出版社,2008.

[6] 田耘,徐文波.Xilinx FPGA开发使用教程[M].北京:清华大学出版社,2008.

[7] 须文波,胡丹.DDR2 SDRAM控制器的FPGA实现[J].江南大学学报(自然科学版),2006.

[8] 胡振良.某导弹遥测数据记录器系统的设计与实现[D].太原:中北大学,2008.

[9] 李圣昆.高速数据采集记录装置的研究[D].太原:中北大学,2006.

[10]The DatasheetofMT47H256M8[R].

[11]李永丽.多通道数据采集及大容量存储系统设计[D].西安:西安电子科技大学,2009.

温建飞(1991-),男,硕士研究生,主要研究方向为动态测试与智能仪器,734285851@qq.com;

岳凤英(1977-),男,硕士生导师,副教授,主要研究方向为导航与制导,303979057@qq.com。

Design and Implementation of Large Capacity Missile Borne Data Recorder

WEN Jianfei1,YUE Fengying2*,LI Yonghong2

(1.School of Computer Scienceand Control Engineering,North Uniυersity of China,Taiyuan 030051,China;2.Schoolof Instrumentand Electronics,North Uniυersity ofChina,Taiyuan 030051,China)

A high capacity of the onboard data logger design has been presented,The scheme ismainly completed 3 high-speed image data receiving,each channel's data bandwidth is 150Mbyte/s,the storage capacity is 128 Gbyte. Xilinx's FPGA design selected as themain controller,the completion of high-speed data reception,caching and storage.The receiving unitadopts GTPRocketIO,which is integrated with FPGA,the data receiving rate ofa single link is 3.125 Gbyte/s;High-speed data buffer unit two DDR2 SDRAM chips

ping-pong cache;Thememory cell is composed of 32 pieces of FLASH NAND,which is stored in thememory array.Meanwhile,the recording device is capable of reading the stored data and analyzed afterwards.

large-capacity;high-speed;rocketio gtp;ddr2 sdram;ping-pong

TP431.2

A

1005-9490(2016)04-0951-06

2015-08-02修改日期:2015-12-03

EEACC:791010.3969/j.issn.1005-9490.2016.04.038