一种高速数据存储系统的优化设计

尉易庆,吴利兵,任勇峰,2*,贾兴中,刘兴俊(.中北大学电子测试技术国家重点实验室,太原0005;2.中北大学仪器科学与动态测试教育部重点实验室,太原0005;.晋中职业技术学院,山西晋中00600)

一种高速数据存储系统的优化设计

尉易庆1,吴利兵3,任勇峰1,2*,贾兴中1,刘兴俊1

(1.中北大学电子测试技术国家重点实验室,太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原030051;3.晋中职业技术学院,山西晋中030600)

针对记录器高速存储的需要,对基于FPGA和NANDFLASH的高速数据存储系统进行了优化设计。该设计通过采用交替双平面的编程方式,对存储器的存储速率进行了优化,使存储速率达到单片Flash最高存储速率的两倍,即60Mbit/s;采用双绞线和电缆延展芯片组,对传输质量进行优化;采用边擦除边写入的方式对存储逻辑进行了优化。在器件选择方面,采用LVDS构成接口电路,FPGA控制逻辑电路。该优化设计的可行性和可靠性已通过工程实践验证。

FPGA;高速存储;LVDS;逻辑设计;

高速数据采集系统目前在航天工程中已得到广泛应用,尤其在卫星工程中的应用更为广泛[1]。怎样实现数据实时、高速可靠的传输到存储设备中,成为一个关键性问题。

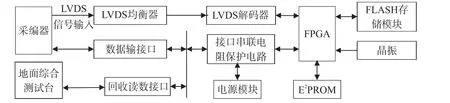

1 总体方案设计

本系统包括电源模块、主控模块和存储模块。存储模块设计作为存储器的核心组成部分,由中心逻辑控制芯片FPGA,接口电路,配置芯片E2PROM,LVDS均衡器、LVDS解码器、存储芯片Flash以及 60 MHz晶振等构成。FPGA通过对LVDS高速接口以及数据的发送和接收来实现逻辑控制[2]。LVDS数据经均衡器、解码器转换后传送给FPGA,FPGA对其缓存处理后,写入Flash芯片;通过接口串联电阻保护电路对存储器数据进行回收;电源模块为整个电路提供电源,工作时钟由60MHz晶振提供。

原理框图如图1所示。

图1 高速存储系统组成原理框图

2 高速数据存储系统的优化设计

2.1存储速率的优化

NANDFLASH以其非易失性、低功耗和单片容量大等优点被广泛应用于固态存储器[3]。但由于其基于页编程、块擦出进行操作的特点,使其在运行期间其他的相关操作得不到响应,从而大大降低数据存储速度。

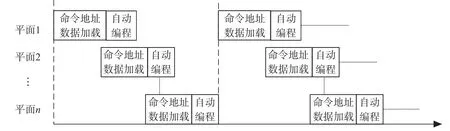

图2是分时加载方式示意图。在完成平面1的数据加载之后,平面2的数据加载即开始进行,而此时平面1进入自动编程时间,与平面2操作互不干扰。平面1、平面2、…平面n依次往下进行。在平面1自动编程完成后,再次对平面1进行数据加载,如此循环,使得数据源源不断地输入到芯片之中,极大地提高了数据的写入速度。

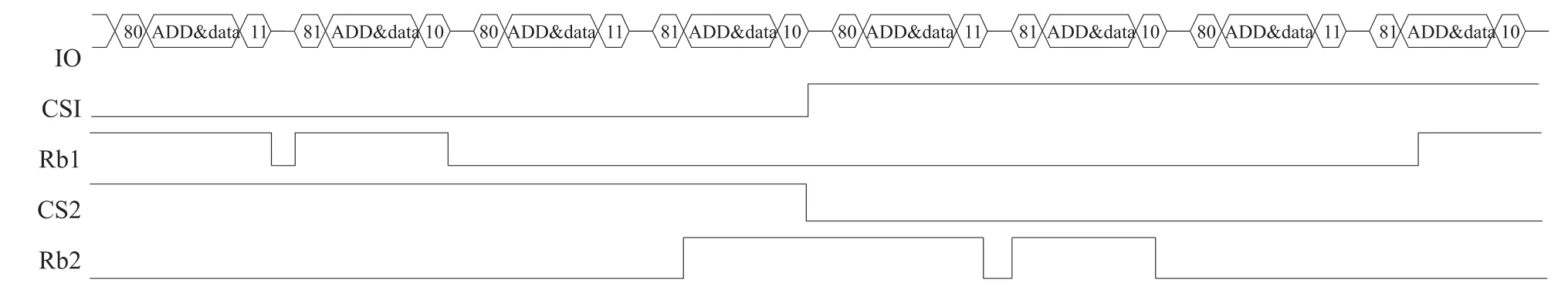

图3为双平面交替存储法[4,5]。这种方法是利用流水线操作思想,分步逐个阵列地完成整个存储,先完成第1组页寄存器存储,等待它进人页编程时间之后再进行2组、3组、4组的页寄存器存储,这样1组、2组、3组、4组来回交替,就可以高速地完成整个存储任务。对图3各个时间进行计算,分析:

第1组加载完成所需页编程时间约为200μs,此时对 2组~4组加载,加载时间为 Tjiazai=[2(4 kbyte×t+7t)+tDBSY]×3=823.2μs;其中,t=1/30Mbyte/s,tDBSY为1μs等待时间。由此看出,当2组~4组完成加载时,第1组已经完成编程,可以继续加载。1组~4组的加载时间 T=[2(4 kbyte×t+7 t)+tDBSY]×4= 1 097.6μs,单片 NANDFLASH最大存储速率为4 096×8 byte/1 097.6μs=29.85 Mbyte/s。采用两片NANDFLASH并行存储,存储速度可达59Mbyte/s。由此可满足高速数据存储系统设计要求。时序如图4所示。

图2 分时加载方式示意图

图3 交替双平面编程方式示意图

图4 交替双平面编程时序示意图

2.2存储逻辑的优化

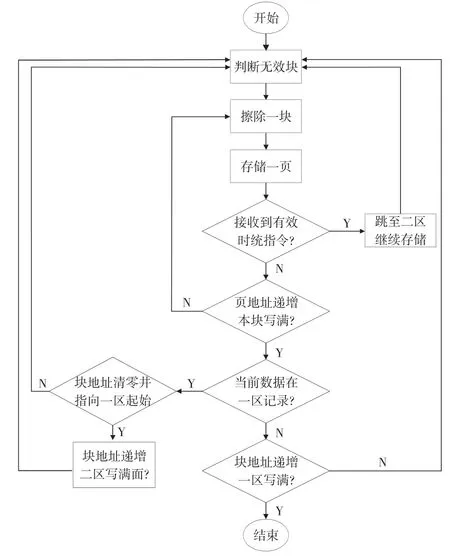

FLASH的数据存储可以是先全部擦除,再进行数据写入。如果FLASH的擦除由手工完成,则记录数据量需小于FLASH容量;如果自动擦除,全部擦除耗费时间过长,可能会导致连续的待存储数据丢失[6]。设计边擦除边写入的方式可以有效的解决以上问题,擦除一块,存储一块,以此往复,不仅满足了数据的自动循环擦写,也保障了记录数据的完整性。图5为存储逻辑流程图。

图5 存储逻辑流程图

2.3传输质量的优化

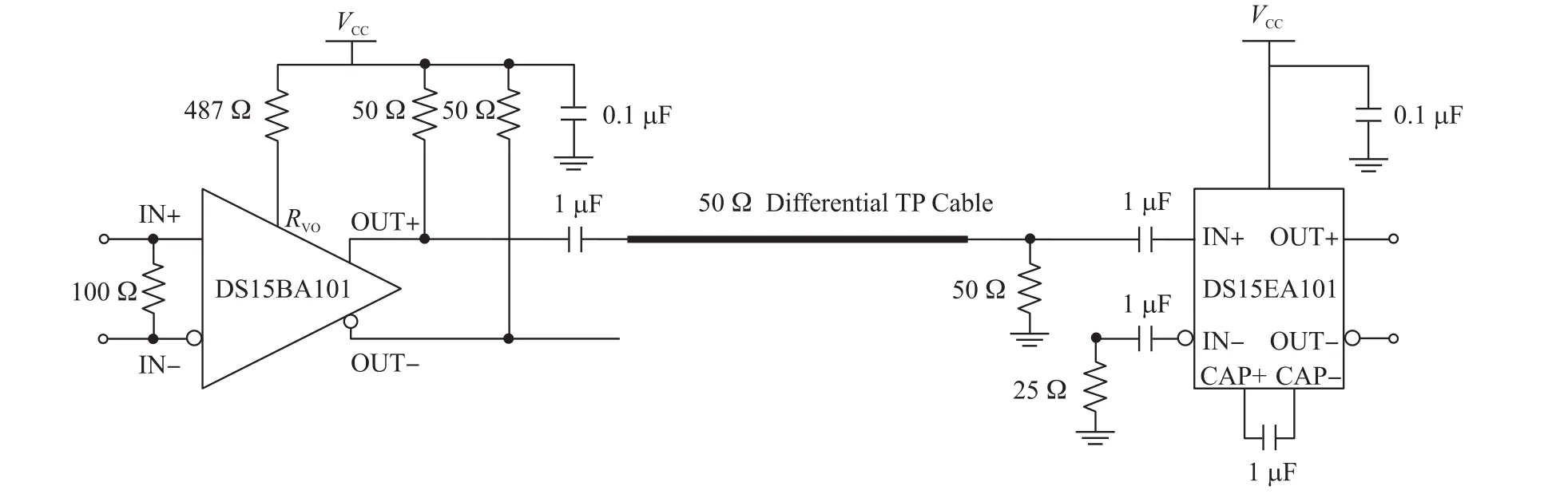

在远距离传输高速数据时,高速信号在传输介质中的衰减是存储数据产生误码的原因之一[7,8]。因此在高速数据进行较远距离传输时,为保证其传输质量,通常采用信号调理技术来针对特定数据速率和传输介质,LVDS传输时通常采用均衡加重技术。对此,可以在信号发送端采用信号驱动器,接收端采用信号均衡器,以实现信号的长距离稳定传输。

DS15BA101和DS15EA101电缆延展器芯片组可以通过双绞线及同轴电缆驱动来自FPGA芯片的串行数据流。DS15BA101是一种高速差分缓冲器,可以用于电缆驱动,信号缓冲和转发等功能;DS15EA101是一种自适应均衡器,可以优化在同轴、双绞线电缆中传输的均衡数据,速度可达150 Mbit/s至1.5Gbit/s。发送器或电缆终端驱动器的信号幅值(发射幅值)决定了自动均衡电路DS15EA101的性能,100Ω差分电缆(双绞线电缆)的最佳发射幅值是±400mV(800 Vp-p),50Ω的同轴电缆的最佳发射幅值也是800mV[9]。DS15EA101的能量检测电路能够对输入的信号能量进行量化,并将其反馈给自动均衡控制电路。自动均衡控制电路对原始信号和反馈信号进行比较,并根据比较结果来控制均衡滤波器,使信号的高频分量获得增益。

图6是利用双绞线和电缆延展芯片组进行高速数据传输原理图。图7为同轴电缆传输原理图。

图6 双绞线延长传输原理图

图7 同轴电缆传输原理图

3 试验结果

对高速数据存储系统设计进行改进后,将本系统连接到某高速图像采集系统后,进行数据的接收和存储。在数据回收后,由上位机软件进行分析处理,根据数据的完整程度来验证存储系统的功能和可靠性。经过几十次测试,测试数据量达300Gbyte,接收的数据均完整无误。存储单元回读数据符合设计,并且数据在传输、存储过程中未出现误码等现象,并实现了60Mbyte/s的存储速度。证明设计方案能够实现采集数据的准确、完整存储及可靠回收。

4 总结

本次设计的存储系统采用交替双平面编程和分时加载的方式,极大地存储速率;利用均衡加重来提高信号的传输质量,保证了数据存储的准确性和完整性,在数据高速存储方面具有良好的应用前景。

[1] 车艳霞,任勇峰,刘东海.一种小体积高速数据记录器的设计与实现[J].自动化与仪表,2011,26(11):9-11.

[2] 盛大鹏.基于FLASH的高速大容量存储器的研究[D].中国科学院研究生院,2008.

[3] 刘瑞,黄鲁,陈楠.基于FLASH的高速大容量固态存储系统设计[J].测控技术,2009,28(4):1-3.

[4] 吴萌,刘波.高速、大容量视频数据存储、传输系统设计[J].电子器件,2009,32(3):638-642.

[5] 陈桂生,李志刚.嵌入式FLASH文件系统的设计与实现[J].计算机系统应用,2010,19(5):36-40.

[6] 李玉峰,韩晓红,刘洋,等.基于FPGA的高速数据采集系统的实现与性能分析[J].电子器件,2012,35(6):709-712.

[7] 陆浩,王振占.高速大容量固态存储器设计[J].计算机工程,2011,37(15):226-231.

[8] 马游春,张涛,李锦明.FPGA集成FIFO在高过载存储测试系统中的应用[J].仪器仪表学报,2006,27(6):2350-2351.

[9] 任勇峰,张凯华,程海亮.基于FPGA的高速数据采集存储系统设计[J].电子器件,2015,38(1):135-139.

尉易庆(1989-),男,汉族,山西运城人,中北大学,硕士研究生,研究方向为电路与系统,weiyiqing@yeah.net;

吴利兵(1969-),男,汉族,山西太古人,晋中职业技术学院,高级工程师,现从事工业机器人、PLC控制系统等领域的研究;

任勇峰(1968-),男,汉族,山西中阳人,博士,教授,现从事动态测试、高速数据采集等领域的研究;

贾兴中(1984-),男,汉族,山西太原人,硕士,工程师,研究方向为微电路系统、电路系统检测与诊断技术;

刘兴俊(1989-),男,汉族,山西太原人,中北大学,硕士研究生,研究方向为电路与系统。

Optim ized Design of a High-Speed Storage System

WEI Yiqing1,WU Libing3,REN Yongfeng1,2*,JIAXingzhong1,LIU Xingjun1

(1.National Key Laboratory for Electronic Measurement Technology,North Uniυersity ofChina,Taiyuan 030051,China;2.Dynamic Testing Laboratory Instrument Scienceand the Ministry of Education,North Uniυersity of China,Taiyuan 030051,China;3.Jin Zhong Vocational&Technical College,Jinzhong Shanxi 030600,China)

For the requirement of data recorder with high-speed storing,it provides an optimizational design to the high-speed system based on FPGA and NANDFLASH.By using the interleaving two-plane program mode to improve its storage speed,the storage rate of the recording device reaches the highestspeed of single Flash,namely 60Mbit/s.By using twisted-pair cables and chipsetwith extended cables,the transmission quality of the system is improved.And that the logical system for storing is optimized is obtained by using erasing and writing pattern at the same time.The logical circuit is controlled by FPGA using LVDS to build interface circuit in choosing devices.And the practicability and reliability of the projecthasbeen tested and confirmed by the engineering practices.

FPGA;high-speed storage;LVDS;logic design

TP301.6

A

1005-9490(2016)04-0816-04

2015-08-11修改日期:2015-10-06

EEACC:7210G10.3969/j.issn.1005-9490.2016.04.013