一种低功耗高线性度VCO的设计与实现

殷万君,武建寿,熊建云,郑 君

(1.四川信息职业技术学院 四川 广元 628017;2.张掖市华光太阳能有限公司 甘肃 张掖 734000)

一种低功耗高线性度VCO的设计与实现

殷万君1,武建寿2,熊建云1,郑 君2

(1.四川信息职业技术学院 四川 广元 628017;2.张掖市华光太阳能有限公司 甘肃 张掖 734000)

随着物联网技术的不断发展,无线通信成为了物联网技术发展的关键技术。射频接收机是无线通信系统的重要功能模块,而压控振荡器(voltage-controlled oscillator,VCO)又是射频接收机的关键组成部分。为了充分考虑面积、功耗、工艺等性能之间的各种约束,设计采用了电流饥饿CMOS反相器单元延时电路,实现了线性度好、频率调节范围广、功耗低、稳定性高的要求。

VCO;电流饥饿;CMOS反相器;线性度

全集成环形压控振荡器(VCOs:Voltage-Controlled Oscillators)由于具有集成度高、调谐范围宽、高线性度及面积小等的众多特征,已经成为众多数字芯片和通信系统的关键模块。环形振荡器是基于反相器的延时原理工作的。只要将任何大于1的奇数个反相器单元首尾相连就可以形成一个基本的环形振荡器,由反相器单元组成的环形振荡电路具有集成度高、结构简单、功耗低的优点[1]。

1 环形振荡器

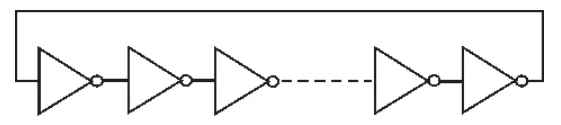

振荡器的振荡频率是由构成该电路的每级反相器的延迟时间的大小和环路中反相器的级数来决定[2]。如图1所示。

图1 反相器链组成的环形振荡器Fig.1 A ring oscillator composed of inverter chain map

采用单端反相器结构的环形振荡器反相器就是其中的延迟单元,如图2所示。延迟单元的数目至少为 3以上的奇数个反相器构成,任何大于或者等于 3的奇数个反相器首尾相连,就能产生自激振荡,周期为T=2NTpd,其中N为串联反相器个数,Tpd为单个反相器延迟时间[3-4]。

图2 反相器延时单元Fig.2 Inverter delay unit

2 电流饥饿型延时单元

由于CMOS反相器的传输延时较短,所以要得到较低的振荡频率是非常困难的[5-6],在电路结构上虽然可通过增加环路级数来降低输出频率,但简单的电路结构改进已不能满足实际的需要。在反相器环路数量不增加的情况下,要想最直接的实现频率的调整,其方法就是改变延迟单元的延迟时间[7-8],而要改变延迟时间在电路的实现途径上是通过改变延迟单元的时间常数和改变延迟单元充放电电流来实现,在实际的电路设计中往往采用多种技术来改变延时单元的延迟时间[9]。

电流饥饿反相器延时单元具有较宽的频带调节特性,通过调整反相器延时单元的电流可以使得振荡器在非常宽的频率范围内进行调节,除了能较为便捷的调节振荡器的频率特性外,电流饥饿型振荡器还具有电路结构简单,功耗较低等众多特点[10]。

由电流饥饿反相器单元组成的环型振荡器的工作过程如下:首先通过输入控制电压或电流模块电路,将控制电压或控制电流转换为电流饥饿反相器单元的偏置电流,最终通过对偏置电流的变化来控制环形振荡器的振荡频率。对电压/电流转换模块电路的要求就是要产生大小合适的偏置电流。

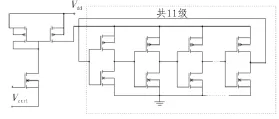

为了使得振荡频率较低,调节范围更宽,可以在电流饥饿型环形振荡器的基础上做进一步的改进,如图3所示。

图3 电流饥饿型环形振荡器电路结构Fig.3 Current starvation-type ring oscillator circuit structure

由M2管和M3管、M5管和M6管组成的反相器为延时单元,NMOS-M1管控制延时单元的放电电流Id1,PMOS-M4管控制延时单元的充电电流Id4,与M2、M3和M5、M6相同的若干单元共同构成了环形振荡器的每一级。M1管和M4管控制着流过M2、M6管的放电电流和M3、M5管的充电电流,也就是说,反相器M2管和M3管;M5管和M6构成的延时单元处于电流的饥饿状态。

若采用N(奇数)级反向器结构,则充电电流i是N级反向器的总的电流,由于每级反相器参数相同,所以每级电流也相等,大小为i/N,当M4管栅极电压较小时,充电电流也较小,处在电流饥饿状态的单级延时单元振荡电路的充放电电流很小,振荡频率也较低;随着控制电压的上升,充电电流逐渐增大,处在电流饥饿状态的延时单元振荡电路的充放电电流也随之变化,振荡频率也随着充放电电流的增加而增加。

表1 仿真参数Tab.1 Simulation parameters

3 基于电流饥饿型反相器延时单元VCO电路的设计与仿真

采用电流镜形式的偏置的结构,电流镜和压控管构成了延时单元的供电电路。电流镜PMOS管取L=1um,W=5um,压控NMOS管L=1um,W=3.3um,取延时链的级数为11级,反相器延时单元N管,P管

图4 仿真原理图Fig.4 Simulation schematic

在MI 0.35um工艺环境下,电源电压为1.8 V。控制电压在0.85~1.15变化时仿真结果如表1所示。

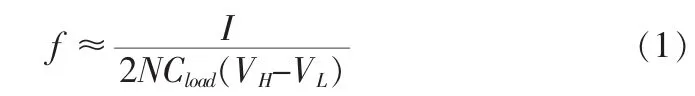

工作在饱和状态的压控MOS管输出电流是与控制电压(VGS-VTH)呈平方关系的,由于控制电压是在 0.8~1.36 V变化,减去阈值电压VTH可使得输出电流进一步细化,1 V范围内电压的平方也近似线性关系,电流与输出频率的关系为式1。

故输出频率与输入电压呈线性关系。若改变延时单元的级数,振荡器的频率将进一步提高。

4 结 论

本文利用电流饥饿反相器延时单元设计了一种线性度好、功耗低、频率可调的全MOS型VCO电路,仿真结果表明,本文设计的VCO可通过调整MOS管参数,使得振荡频率调整范围更宽,电路结构简单,易于设计。

[1]殷万君.基于温度的DRAM刷新时钟产生电路设计[D].成都:西南交通大学,2014.

[2]张爱琴,段吉海,秦志杰.两种高频 CMOS压控振荡器的研究与设计[J].电子科技,2009,22(11):26-29.

[3]陈永洁,刘忠,危长明,等.低相位噪声CMOS环形振荡器的研究与设计[J].微电子学,2008(6):76-80.

[4]M.Straayer,J.Cabanillas,and G M.Rebeiz.A low-noise transformer—based 1.7 GHz CMOS VCO[J].IEEE International Solid—State Circuits Conference,2002(1):286-287.

[5]L.H.Lue,H.Hsieh-Hung,and L.Yu-Te.A wide tuning-range CMOS VCO with adifferential tunable active inductor[J].IEEE Trans.Microw.Theory Tech,2006,54(9):3462-3468.

[6]Chang—Hsi Wu and Guan—Xiu Jian.A CMOS LC VCO with Novel Negative Impedance Design for Wide·Band Operation[J].IEEE Radio Frequency Integrated Circuits Symposium,2010:537-540.

[7]Hsieh-Hung Hsieh,Liang-Hung Lu.A Low—Phase—Noise K.Band CMOS VCO[J].IEEE Microwave And Wireless Components Letters,2006,16(10):552-554.

[8]李天望,曾晓军,洪志良.1V 2.5 GHz压控振荡器设计[J].半导体学报,2009,24(1):80-83.

[9]施琦锋,薛晓博,何乐年.新型数模转换器时域误差校正方法[J].浙江大学学报(工学版),2013(11):2025-2030.

[10]徐伟杰,梁炜,凤超.WIA-PA网络关键技术的设计与实现[J].计算机应用研究,2011(6):2265-2270.

Design and realization of low power and high linearity based on VCO

YIN Wan-jun1,WU Jian-shou2,XIONG Jian-yun1,ZHENG Jun2

(1.Sichuan Information Technology College,Guangyuan 628017,China;2.Zhangye City Huaguang Solar Energy Co.Ltd,Zhangye 734000,China)

with the continuous development of Internet of things technology,wireless communication has become the key technology in the development of iot.The RF receiver is an important function module of wireless communication system,and the voltagecontrolledoscillator(voltage-controlledoscillator,VCO)isthekeypartofRFreceiver.Inordertofullyconsiderthevarious constraints between the area,power consumption,process performance,the design uses the current hunger CMOS inverter unit delaycircuit,achievedgoodlinearity,frequencyregulationrange,lowpowerconsumption,highstabilityrequirements.

VCO;current hunger;CMOS inverter;linearity

TN752

A

1674-6236(2016)02-0110-02

2014-10-15稿件编号:201410106

四川省教育厅自然科学重点项目(15ZA0380);四川省教育厅自然科学一般项目(15ZB0467);甘肃省科技厅科技支撑计划(1204GKCG059)

殷万君(1980—),男,甘肃张掖人,硕士,讲师。研究方向:大规模集成电路设计与仿真。