基于FPGA的视频叠加系统在电视导引头中的应用

曲锋,隋龙,赵建,孙强

(中国科学院 长春光学精密机械与物理研究所,吉林 长春 130033)

基于FPGA的视频叠加系统在电视导引头中的应用

曲锋,隋龙,赵建,孙强

(中国科学院 长春光学精密机械与物理研究所,吉林 长春130033)

在电视导引头应用中,视频叠加显示信息可以为后期诊断调试提供有效的信息,为了能够解决视频叠加信息显示问题,提出了一种基于FPGA的视频叠加系统,该系统采用FPGA对视频的行场频及像素时钟信号进行计数扫描法,利用模拟视频开关将相应的白电平直接叠加到视频输出模拟信号上。该方法具有成本低、可靠性高和易于开发的优点。在最终的实验结果证明,该系统能够达到预期效果,对电视导引头的显示波门信息等应用画面效果良好,能够满足工程应用的需要。

视频叠加;FPGA;电视导引头;图形图像叠加系统

近年来,随着国内外图像处理技术在实时性及处理速度上的高速发展,电视导引头在导弹等武器系统中的应用越来越受到重视[1]。所谓电视制导技术就是指采用电视摄像机对目标进行捕获、识别、定位、跟踪直至击中目标的技术[2]。因为电视的分辨率比较高,在跟踪目标时能够提供比较清晰的目标图像信息,有利于鉴别目标的真伪,所以该技术在精确制导中占据着重要的位置。

本文针对电视导引技术中的图像显示系统进行了研究,提出了一种基于FPGA的图形图像与字符的视频叠加方法,该方法具有成本低、实现简单及系统可靠等优点,同时该方法还可广泛应用于如监控安防等民用领域。

1 视频叠加方法及原理

视频叠加原理主要是基于电视扫描原理,即每一帧图像有625行,采用隔行扫描,分为两场,奇数场和偶数场,每场均有312.5行数据,而每行则有765个像素值,因此对于每一场图像都是一个312×765大小的二维矩阵数据,同时不考虑彩色信息,而只讨论黑白视频信号,则视频叠加原理就是将每场图像看成是312×765的灰度图像,对应每一点的灰度值为0则显示黑色,灰度值为255则显示白色,而要显示的信息则直接以描点的方式在相应位置将其灰度值修改为0或255即可。

目前所流行的视频叠加方法主要可以概括为两大类,一类是数字叠加法[3-4],另一类是模拟信号叠加法[5-6]。

其中数字叠加法主要是指将模拟视频进行解码后,转换成数字信号,然后将需要叠加的图形和字符叠加到数字信号中,再通过编码芯片将数字信号转换成模拟信号输出。这种方法直接对数字信号操作,具有非常好的灵活性,然而由于增加了一片编码芯片,不仅提高的系统的成本,而且降低了系统的可靠性,同时由于处理系统需要进行编码的控制,增加了软件的工作量和视频信号的延时。

而模拟信号叠加法主要有两种,一种是采用专用的字符叠加芯片,如MK36000、MB90092等,这种芯片具有简便灵活特点,只需要将要显示的字符和其显示的位置输入至字符叠加芯片,则可以直接在视频图像上自动进行叠加,字符叠加芯片对于字符的叠加以及固定图形的叠加具有非常好的使用效果,然而对于跟踪波门一类的动态图像却显得无能为力。另一种方法即是本文所讨论的模拟视频开关法,采用FPGA对行场频及像素时钟进行计数法,进行视频图像的叠加显示。

2 系统结构设计

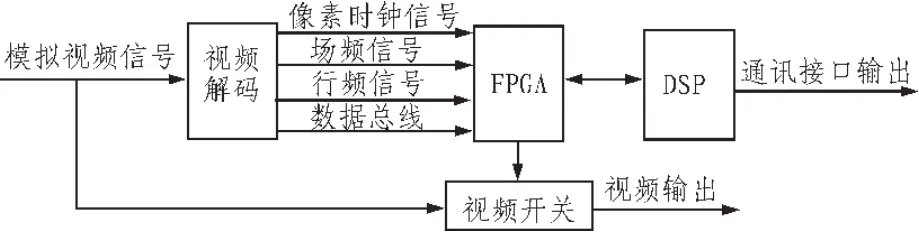

标准电视制式信号的导引头系统其主要功能是对视频信号中的目标进行捕获和跟踪,其工作流程主要包括对电视信号的解码将模拟信号转换成数字信号,由FPGA将数字信号传输至数字信号处理器(DSP)进行目标的捕获和跟踪算法处理,由DSP将处理后的目标坐标位置及目标大小等信息通过通讯接口发送至弹载计算机,同时由FPGA将相关信息进行视频叠加显示输出即完成了一个完整的目标捕获跟踪过程。系统结构如图1所示。

图1 系统总体结构图Fig.1 Structure diagram of system

3 系统硬件设计

在本系统中,由于DSP主要偏重于跟踪算法功能,不是本文讨论的重点,因此不做阐述。对于视频解码芯片我们采用了ADV7180,同时将像素时钟信号、场频信号、行频信号与数据总线都接在FPGA的管脚上。

FPGA我们则采用Altera公司生产的Cyclone II系列的EP2C8Q208I8芯片,该芯片具有成本低、功耗小、性能优等特点,而对于模拟视频开关则采用了TI公司生产的TS5A2053芯片,该芯片具有以下特点:

1)单电源宽电压供电(1.65 V~5.5 V);

2)带宽330 MHz,远远超过模拟视频的6 MHz带宽;

3)低导通电阻,即为7.5 Ω;

4)极低的打开/关断时间,分别为6.8 ns和4.1 ns。

在EN信号为低电平使能条件下,当IN信号为低电平时,NC与COM导通,当IN信号为高电平时,NO与COM导通。

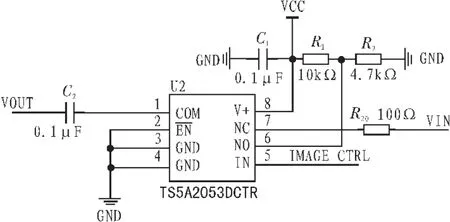

图2 模拟视频开关电路原理图Fig.2 The circuit schematics of analog video switch

由TS5A2053特点可以设计如图2所示的视频叠加电路,在NO端我们直接输入一个固定电平,该电平由电阻R1 和R2分压方式得出,因此当VCC为5 V时,该管脚的电压为1.053 V,因此可以认为是白电平信号,而NC端则直接输入待处理的模拟视频信号,根据前面所述的视频叠加原理,可以直接用FPGA控制TS5A2053芯片的IN管脚,选择是显示正常的模拟视频信号还是白电平信号方式进行信息的叠加。因此当VCC为5 V时,该管脚的电压为1.053 V,因此可以认为是白电平信号,而NC端则直接输入待处理的模拟视频信号,根据前面所述的视频叠加原理,可以直接用FPGA控制TS5A2053芯片的IN管脚,选择是显示正常的模拟视频信号还是白电平信号方式进行信息的叠加。

4 系统软件设计

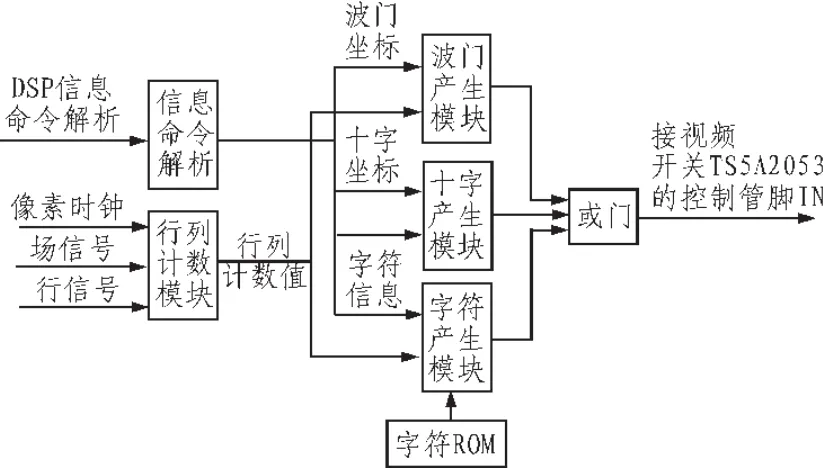

在FPGA的软件设计中,我们采用了Verilog HDL做为开发语言,并采用了模块化的方式进行了软件设计,其软件结构框图如图3所示。

图3 系统软件设计结构图Fig.3 Schematic diagram of the software system

从结构框图可以看出,软件系统共分为5个模块:

1)信息命令解析模块:信息命令解析模块在本系统中的主要作用是对DSP发送来的指令进行解析,将其转换成如波门信息所需要的左上角和右下角的顶点坐标,十字坐标的中心坐标及长度,要显示的字符及其相应位置坐标,同时将这些坐标转换成符合行列扫描计数的值传输至对应功能模块进行处理。

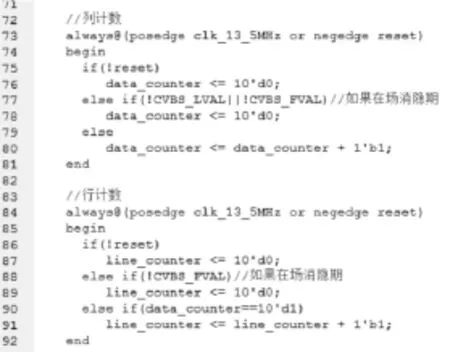

2)行列计数模块:本模块主要是对每一场中的行和每一行进行计数,这样可以表示出当前时刻下的行数和列数,其程序如图4所示:

图4 行列计数程序Fig.4 Program of line-counter

3)波门产生模块:对于波门图像只需要左上角和右下角的坐标即可确定大小,其实任何图形都是线段和点的集合,因此我们可以将叠加的信息看做是画线段的过程,因此对波门就是横线与竖线的组合。根据硬件的设计可知,如果对TS5A2053芯片的IN管脚置高电平,则叠加白色信息,因此以波门左上角与右下角坐标为判断条件,当行列计数模块中的data_counter与line_counter的值符合判断条件时,即置高IN管脚即可实现。以画横线程序为例如图5所示:

由程序可以知道,当horizontal_line_enable为1时,则对TS5A2053芯片的IN管脚置高电平以显示白线。

4)十字产生模块:对于十字图形,其实与波门的叠加方式原理相同,此处不再做讨论。

图5 波门画横线程序Fig.5 Program of drawing a gate horizontal line

5)字符产生模块:由于字符图形与波门和十字图形相比较较为复杂,因此可以用目前大多数字模提取工具生成相应字符的坐标数据,从而制作一个适合本系统的字库并存储到FPGA内嵌的ROM中,这样在显示字符时,只需从ROM将相应字符的数据读出做为判断条件即可,其方式与波门和十字图形的产生原理一样。

最后再将三个图形产生模块的控制信号线用或门进行判断,输出至TS5A2053芯片的IN管脚。最终的测试结果如图6所示。

5 结 论

图6 视频叠加显示效果Fig.6 The effect shows of video overlap

本文所述的视频叠加系统解决了在电视导引头中视频信息叠加显示的问题,同时在基于FPGA系统设计中,只需一个模拟视频开关即可完成视频叠加的功能,具有成本低、可靠性高、开发简单等优点。实际应用也证明该系统工作稳定,效果良好。

[1]张自发,孙建楠,孙勇,等.电视制导技术应用研究[J].红外与激光工程,2010(39):526-528.

[2]夏思宇.精确制导技术及其现状与发展 [J].航空科学技术,2003(1):41-43.

[3]刘洋.电视导引头目标跟踪显示技术研究[D].南京:南京理工大学,2012.

[4]万鹏,杨大伟.基于FPGA的视频叠加融合系统设计与实现[J].电子技术与应用,2013,39(9):46-44.

[5]薛陈,熊文卓,龙科慧,等.基于CPLD的带刻度十字丝的产生电路[J].电子器件,2007,30(6):2050-2052.

[6]罗凌.一种视频、图形、汉字叠加系统在雷达光电跟踪中的应用[D].成都:电子科技大学,2007.

Design of portable power control unit test system based on FPGA in the TV seeker

QU Feng,SUI Long,ZHAO Jian,SUN Qiang

(Changchun Institute of Optics,Fine Mechanics and Physics,Chinese Academy of Sciences,Changchun 130033,China)

In order to satisfy the requirement of the Power Control Unit,the design of the Power Control Unit test system based on LabWindows/CVI is designed in this paper.The hardware system is used to produce the input signals of PCU.The software system adopts the LabWindows/CVI software as development environment.The Power Control Unit test system can accomplish the output signals test of the Power Control Unit.The experiment and application show that this test system has good performance,and achieve the design requirement.

video overlap;FPGA;TV seeker;OSD

TN919.81

A

1674-6236(2016)03-0181-03

2015-05-06稿件编号:201505051

吉林省重点科技攻关项目(20140204030GX)

曲 锋(1984—),男,山东泰安人,博士,副研究员。研究方向:红外图像处理,硬件设计。