基于FPGA的Flexray IP核通信的研究与实现

雷志军,李文新,雷志广,贾露娟

(兰州空间技术物理研究所 甘肃 兰州 730000)

基于FPGA的Flexray IP核通信的研究与实现

雷志军,李文新,雷志广,贾露娟

(兰州空间技术物理研究所 甘肃 兰州730000)

目前从航天工程角度来看,CAN和1553B的速率、可靠性和成本指标在航天系统中应用最为适宜。但是对于安全等级要求更高的系统则需一个新的标准。尤其是对故障容错与时间确定性需求不断增加的系统。FlexRay通过在确定的时隙中传递信息,以及在两个通道上的故障容错和冗余信息的传送,满足了这些新增加的要求。然而,集成着FlexRay IP的芯片目前主要满足的是汽车安全等级而不能满足宇航级。通过对集成着FlexRay IP核的CPU进行筛选和加固会导致芯片费用昂贵。基于以上问题,本文选用满足宇航级的FPGA来实现FlexRay通信控制器,这种方法既可以简化FlexRay节点的硬件复杂度和成本,也为FlexRay的实现新添了一种方法。并且为其在航天领域的应用做出相应的研究。经测试可知两个节点可以正常稳定通信。

FlexRay IP;通信控制器;FlexRay;FPGA;筛选

目前,星载设备上通用的总线协议为CAN和1553B。CAN总线[1]是一种成熟的串行通信总线,它是由德国的BOSCH公司从20世纪80年代初为解决汽车中众多的控制与测试仪器之间的数据交换而开发的一种串行数据通讯协议。它具有可靠性高[2]、稳定性好、抗干扰能力强、通信速率高、维护成本低、实时性强、很好的开放性及数据兼容性等优点。其最大数据吞吐率为1 Mbps。由于CAN总线是基于事件触发的,虽然保证了通讯的实时性,但当多个事件同时触发时则不能保证信息到达的时间的确定性。

MIL-STD-1553B总线是20世纪70年代由美国空军提出的一种串行通信总线。其具有双向输出特性,实时性和可靠性高[3]。广泛应用在当代的运输机和相当数量的民航客机以及军用飞机上。航天系统也广泛的应用这一总线。1553B总线是一种集中控制、响应式多路数据传输总线。总线组成包括:一个总线监视器(BC)负责总线调度管理,若干个(0-31)远程终端(RT)构成。其总线传输速率为 1 Mbps。虽然1553B有以上优点,但是RT与RT之间通信方式复杂,必须通过BC才能进行通信。

FlexRay总线是在2000年由国际几大汽车巨头组织建立了FlexRay联盟[4],其目的就是设计一个新的时间触发通讯协议用于汽车工业上,并且在速度和稳定性上都超过CAN 和TTP[5]。在2009年FlexRay联盟解体,并将最后一个版本的通讯协议称作——FlexRay;目前FlexRay协议已经成为ISO标准的一员。FlexRay总线支持消息冗余和非冗余2种传输[6],在考虑冗余的情况下该总线理论上的最高通信速率达到10 Mbps,是CAN和1553B总线通信速率的10倍。如果不考虑冗余则其传输速率可以达到20 Mbps。并且在一个FlexRay通信周期内。同时综合了时分多址和柔性时分多址的总线技术。例如在一个通信中期中包括有静态段、动态段、符号窗和网络空闲时间。静态段采用时间触发方式来保证信号传输的高度确定性,补充了CAN总线在多事件同时触发时信息到达的不确定性。动态段则采用事件触发方式来增强通信的灵活性。

基于以上原因,本文选择FlexRay作为研究对象。

1 FlexRay节点的硬件平台搭建

单个FlexRay节点由以下8部分组成:USB BLASTER、RS232、POWER、SDRAM、SRAM、EXTCLK、FPGA和TJA1080。其中USB BLASTER用于下载和调试程序。PC机通过RS232与FPGA进行信息交互,从而通过PC机输入命令来控制程序的运行。POWER是整个系统的供电模块,电源的完整性将影响整个硬件是否能正确运行的关键。SDRAM、SRAM用于存储应用程序、EXT CLK用于同步外部的节点。FlexRay总线驱动器TJA1080是FlexRay节点的最重要的一个部分,FPGA通过它与外部的FlexRay总线进行通信。整体框架如图1所示。

图1 系统框架Fig.1 System framework

2 FlexRay节点的软件实现

FlexRay IP核是个复杂的软核。FlexRay IP核实现主要由以下6个部分组成:64 bit的时间戳、事件日志、触发器、Injector、FlexRay控制器、UART。

图2 FlexRay IP核的整体框架Fig.2 The overall framework of the IP kernel FlexRay

其中 64 bit的时间戳为各个部分提供了时钟计数。Event Logger用来记录一些通信过程中的信息。Trigger作为FlexRay IP核的重要组成部分,它的作用是检测一些信号模式的到来。如果一些信号(如上升沿或下降沿等)发生将触发相应的信号被发送。Injector是FlexRay IP核的一个重要组成部分,它可以产生任意的波形并发送到FlexRay总线上作为无效的信息。FlexRay通信控制器用它产生的波形作为冲突波形来测试节点的接收是否正常。FlexRay控制器是FlexRay IP核的核心构成元素,它对FlexRay协议V2.1的大部分功能予以实现。UART控制模块主要用于PC机与FlexRay IP之间的信息交互。FlexRay IP核的整体框架图2所示。

从图2可以看出FlexRay IP核主要可以分为两大部分:VHDL描述的硬件和程序运行控制的C语言。其中用VHDL描述的硬件是FlexRay IP实现通信的最重要也是最核心的一部分,它描述了FlexRay IP的硬件构成及各功能模块的实现,其中FlexRay控制器是FlexRay IP构成的主要元素,接下来我们将详细介绍一下FlexRay控制器各个组件的VHDL构成的功能。

2.1FlexRay控制器的VHDL实现

FlexRay控制器主要包括控制器主机接口、协议操作控制器(POC)、Macrotick生成模块、时钟同步处理模块、时钟同步启动模块、(MAC)媒体访问控制模块、帧和符号处理模块、编码解码处理模块。

其中主控制器接口对每个节点主控制器 (NIOS II软核)与FlexRay协议引擎间的数据和控制流进行管理。主控制器接口包含两个主要的接口模块-协议数据接口protocol data interface和信息数据接口message data interface。协议数据接口管理着所有与协议运行相关的数据交互,而信息数据接口管理着所有与信息交互相关的数据交互。

协议操作控制:每个核心处理器允许对其基本运行状态进行变更,以满足节点更高模式的改变。如果核心处理器在完全协调和同步的情形下发生变更,正确的协议状态才能出现。POC的目的是响应主机指令以及在同步方式中核心处理器变更时做出协议调节,并且根据变更情况向主机提供适当的状态反馈。在唤醒、启动和重组规程中核心处理器的同步是必需的。

Macrotick生成模块:它是由Microtick时钟作为原时钟,并结合时钟同步处理模块产生的误差来更新Macrotick时钟的生成。

时钟同步处理模块:在一个分布式通信系统中,各个节点拥有各自的时钟。即使在最初所有的内部时钟基准是同步的,但由于温度高低,电压起伏,及时钟源(如晶振)公差等原因,各个节点间的内部时钟基准同样存在一个短时间的偏差。一个时间触发系统的基础是在集群的每个节点都拥有近似相同的时间窗口并且该。全局的时间窗口用作各个节点通信计时的基准。因为FlexRay协议采用的是一个分布式的时钟同步机制。集群中各个节点根据其他节点发出的同步帧信息各自完成与集群的同步。所以此模块是用来计算一写频率和相位偏差的模块,并将计算的结果送给Macrotick生成模块用来调整Macrotick的大小从而来保证全局的时间窗口“近似相同”。而“近似相同”的意思是不同的两个节点间,其全局时间窗口的偏差在规定的容差范围内。而此偏差的最大值则是平常所称的精度。

时钟同步启动模块:对于一个时分多址通信方案而言,要求参与该集群通信的所有节点具有同步和时间对准的能力。一个容错的分布式启动策略将用于对所有节点进行同步,这是正常通信的前提保证。

媒体访问控制模块:在FlexRay协议中,媒介存取控制是基于一个循环的通信周期的。在一个通信周期中,FlexRay提供了两个媒介存取方案供选择。他们是静态时分多址存取方式(TDMA)和基于最小时隙的动态存取方式。

帧和符号处理模块:帧信息和符号处理(FSP)是帧信息和符号解码间的主要处理层,帧信息和符号处理通过时分多址存取模式对帧信息和符号的准确时间进行校对,并进一步按照语法检验对接收的帧信息进行校验,以确定其语义正确性。

编码解码处理模块:它有两种功能,一种是将要发送的帧转化成NRZ信号并发送到FlexRay总线上,另一种功能是从FlexRay总线上接收帧信息,并将满足NRZ信号的逻辑零和一转化成满足FlexRay的帧格式。

2.2C语言控制实现

C语言的控制也是非常重要的一部分,通过它的编写可以控制FlexRay IP核正常初始化、控制和通信。下面就对C语言控制进行介绍:

协议操作控制(POC)是FlexRay IP核最核心的一个部分,FlexRay的各个状态之间的转变就是靠POC控制的。当开发板上电后,协议会进行default config状态,在这个状态里FlexRay IP会进行一些默认的配置。然后转换到config状态,这时是用户进行参数的配置(如通道的选择、时钟同步配置的参数等)、buffer和 FIFO的初始化等处理。然后是ready状态,在这个状态下如果节点是冷启动节点则有责任去唤醒其它睡眠模式下的节点(这个过程是 wakeup状态)。如果这个节点不是冷启动节点,则其将没有发送wakeup信号的能力,只要被唤醒的能力。当全部节点都被唤醒后状态会跳转到startup状态。在这个状态下冷启动节点会启动通信,跟随冷启动节点会首先集成到通信簇里,最后是非冷启动节点集成到通信簇里。到目前为止FlexRay便可以正常通信。

实际上,C语言的控制流程也是按照协议操作控制(POC)的状态转变过程进行配置的。图3是更详细的C语言实现的控制流程图。

图3 C语言实现的控制流程图Fig.3 C control flow chart language

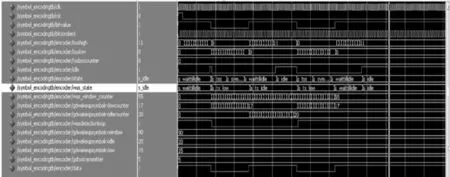

3 MODELSIM仿真

FlexRay总线开始通信的前提是节点是否被正确的唤醒和启动,在FlexRay协议v2.1中,它是由两个WUS组成的一个WUP,其中底电平gdWakeupSymbolTxLow的有效取值可在15~60 gdBit,而高电平的取值范围在45~180 gdBit这个范围内。簇中节点被唤醒的前提是所有总线驱动器都已经上电。冷启动节点有发送WUS符的责任,当其它节点的总线驱动器接收到这个WUS后就会唤醒本节点。唤醒的仿真波形如下图所示,它也是由两个WUS构成一个WUP的仿真波形。从图中可以看出WUP发送的全过程,及其波形的正确性。

图4 ModelSim仿真WUP波形Fig.4 ModelSim WUP waveform simulation

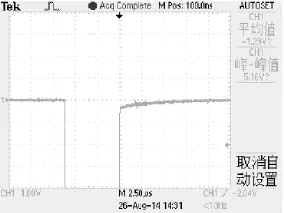

4 硬件测试

经过ModelSim仿真后,我们将开始进行硬件的调试,首先将VHDL实现的FlexRay IP下载到FPGA中,然后调用NIOS软件将C语言实现的控制程序下载到FPGA中并全速运行。通过示波器我们可以发现首先获取的信号是由冷启动节点A发送的15个WUS构成的WUP信号,具体的测试波形如图5所示。

图5 示波器测得WUP波形Fig.5 The measured waveform oscilloscope WUP

当节点B接收到来自冷启动节点A的唤醒信号后,跟随冷启动节点B也发出同样的唤醒信号到FlexRay总线。这时两个节点都已经被唤醒并进入启动阶段。在传输启始帧之前冷启动节点将先发送一个CAS(冲突避免标示符)到FlexRay总线。CAS标示符的测试波形如图6所示。

FlexRay网络的起始阶段由冷启动节点进行初始化,冷启动节点有启动通讯的能力。非冷启动节点必须等待其启始后才能集成到簇中。冷启动节点在时间表中指定的位置发送启始帧。在网络起始阶段这些启始帧是惟一被发送的帧。并且它们每个周期都被发送。具体测试到的启始帧波形如图7所示。

图6 示波器下冲突避免标示符(CAS)Fig.6 Oscilloscope conflict avoiding identifier(CAS)

图7 示波器测得的启始帧波形Fig.7 Oscilloscope measured starting frame waveforms

5 结束语

经过理论的学习与研究,本文实现了能够在两块FPGA之间进行正常通信的FlexRay节点。下一步计划是实现由多个FPGA实现的FlexRay节点间的通信。并对总线利用率进行理论学习与验证。为FlexRay总线在航天中应用做前期研究。

[1]刘欣,杨志佳.FlexRay通信控制器收发功能的研究和实现[J].汽车电子,2007,3(6):266-268.

[2]何仁,李强.汽车线控转向技术的现状与发展趋势[J].交通运输工程学报,2005,5(2):68-72.

[3]袁春柱,刘思远,杨芳.星载FlexRay总线应用层传输方法研究[J].航天器工程,2013,22(3):68-70.

[4]陈涛,秦贵和.FlexRay时钟同步分析[J].计算机工程,2010,14(36):235-237.

[5]程驰,帅志斌,李建秋,等.车载网络通讯协议FlexRay网络的分析及搭建[J].汽车安全与节能学报,2013,4(1):76-79.

[6]刘思远,杨芳,汪小洁,等.时间触发型FlexRay总线星载应用研究[J].航天器工程,2012:6-12.

Research and implement of point to point communicate based on FPGA’s FlexRay IP

LEI Zhi-jun,LI Wen-xin,LEI Zhi-guang,JIA Lu-juan

(Lanzhou Institute of Physics,CAST Lanzhou 730000,China)

At present from the perspective of Aerospace Engineering,CAN and 1553B's rate,reliability and cost index in the application of space system are the most appropriate.But for the system security level required higher needs a new standard. Especially for the fault tolerance and time deterministic demand are increasing system.FlexRay through the transmission of information in determining the time slot,And the transmission of fault tolerance and redundancy information in two on the channel,To meet these new increased demand.However,integrated with FlexRay IP chip at present mainly is to meet the automotive safety level and can not meet the space level.Through screening and reinforcement will lead to expensive of the integrated FlexRay chip IP core CPU.Based on the above problems,this paper used the FPGA to meet aerospace grade to realize FlexRay communication controller,This method can not only simplify the FlexRay node hardware complexity and cost,Also provides for a method of the implementation of FlexRay.And make the appropriate research for its application in the field of space.The test indicated that the two nodes can be normal and stable communication.

flexray IP;communication controller;flexray;FPGA;screening

TN91

A

1674-6236(2016)03-0148-04

2015-03-12稿件编号:201503164

雷志军(1987—),男,甘肃兰州人,硕士。研究方向:电子技术在空间中的应用。