基于AD9762和EP2C70的低功耗轻型化调制器设计与实现

纪春国,卢丹

(航天科技集团公司五院513所 山东 烟台 264003)

基于AD9762和EP2C70的低功耗轻型化调制器设计与实现

纪春国,卢丹

(航天科技集团公司五院513所 山东 烟台 264003)

本文基于低功耗、轻型化调制器的目的,采用了低功耗、小封装的FPGA和DA芯片,即AD9762和EP2C70联合的设计思想,给出了QPSK调制器的原理和工程实现方法;运用FPGA软件编程的方法实现了数字化的QPSK调制器,并通过AD9762实现数字到模拟信号的转换,取得了调制器低功耗、小型化,达到了设计目的,满足应用需求。

调制;低功耗;DDS;轻型化;FPGA

随着低功耗、小型化需求的与日俱增,各大系统对设备的功耗、体积、重量等开始有着苛刻的要求,特别是在弹载、星载、船载等能源有限的情况下,低功耗、小型化显得尤为重要。目前大部分调制器都体积大、功耗大,在某些场合无法应用。本文提出了一种基于Altera公司EP2C70和DA9762进行低功耗、轻型化的调制器设计。

1 芯片简介

1.1EP2C70简介

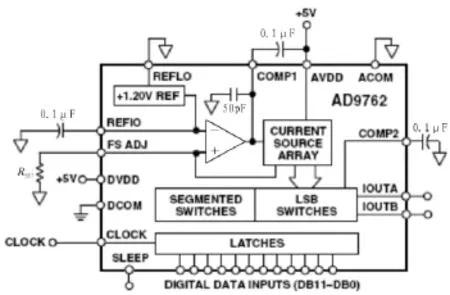

Altera公司 Cyclone系列 FPGA——EP2C70采用基于90nm工艺技术,采用低电介常数的电介质和全铜质金属层,因此具有潜在速度方面的极大优势,和高级面积特性提供的动态功耗优势,通过提高布线密度获得极高的面积效率。包含超纵向排列逻辑单元(LE)、嵌入式存储器块、嵌入式乘法器和锁相环(PLL),它们被I/O单元(IOE)包围在中间。高效互连、低歪斜的时钟网络在每个结构之间提供时钟和数据信号连接。面积高效的IOE被分组成围绕在器件周围的I/O区,在消耗最小裸片面积的同时提供可观的I/O能力。支持大范围的单端和差分I/O标准。每个IOE包含可编程驱动强度、总线保持和可编程回转速率等相关电路。多个I/O区组装在一起提供专用外部存储器接口电路。

支持多种单端和差分I/O标准。例如LVTTL、LVCMOS、SSTL-2、SSTL-18、HSTL-18、HSTL-15、PCI和PCIX,以连接至板上其他器件。当FPGA与其他高级存储器件如双倍数据速率 (DDR和DDR2)SDRAM和QDRIISRAM器件一起工作时,单端I/O标准是关键因素。与单端I/O标准相比,差分信号提供更好的噪音容限,产生更低的电磁干扰(EMI),并降低了功耗。支持的差分标准有 LVDS、miniLVDS、RSDS、LVPECL、DHSTL、DSSTL等。

单FPGA的AS配置方式电路如图1所示。

JTAG配置方式符合IEEE1149.1标准,将每块FPGA看作是JTAG链上的一个器件,直接将配置文件下载到FPGA中。下载完毕以后FPGA释放CONF_DONE信号,Quartus通过JTAG接口检测CONF_DONE信号,可以显示配置成功与否。接下来进入和AS一样的初始化阶段。

单FPGA的JTAG配置方式电路如图2所示。

EP2C70芯片的下载方式由MSEL0和MSEL1组合进行配置。其中使用JTAG方式要求MSEL0和MSEL1不悬空,单用JTAG方式则全部接地。这里使用AS+JTAG的方式,所以MSEL[1..0]设置为10。

表1 FPGA电源种类Tab.1 FPGA power category

图1 FPGA的AS配置方式电路Fig.1 The FPGA AS installs way electric circuit

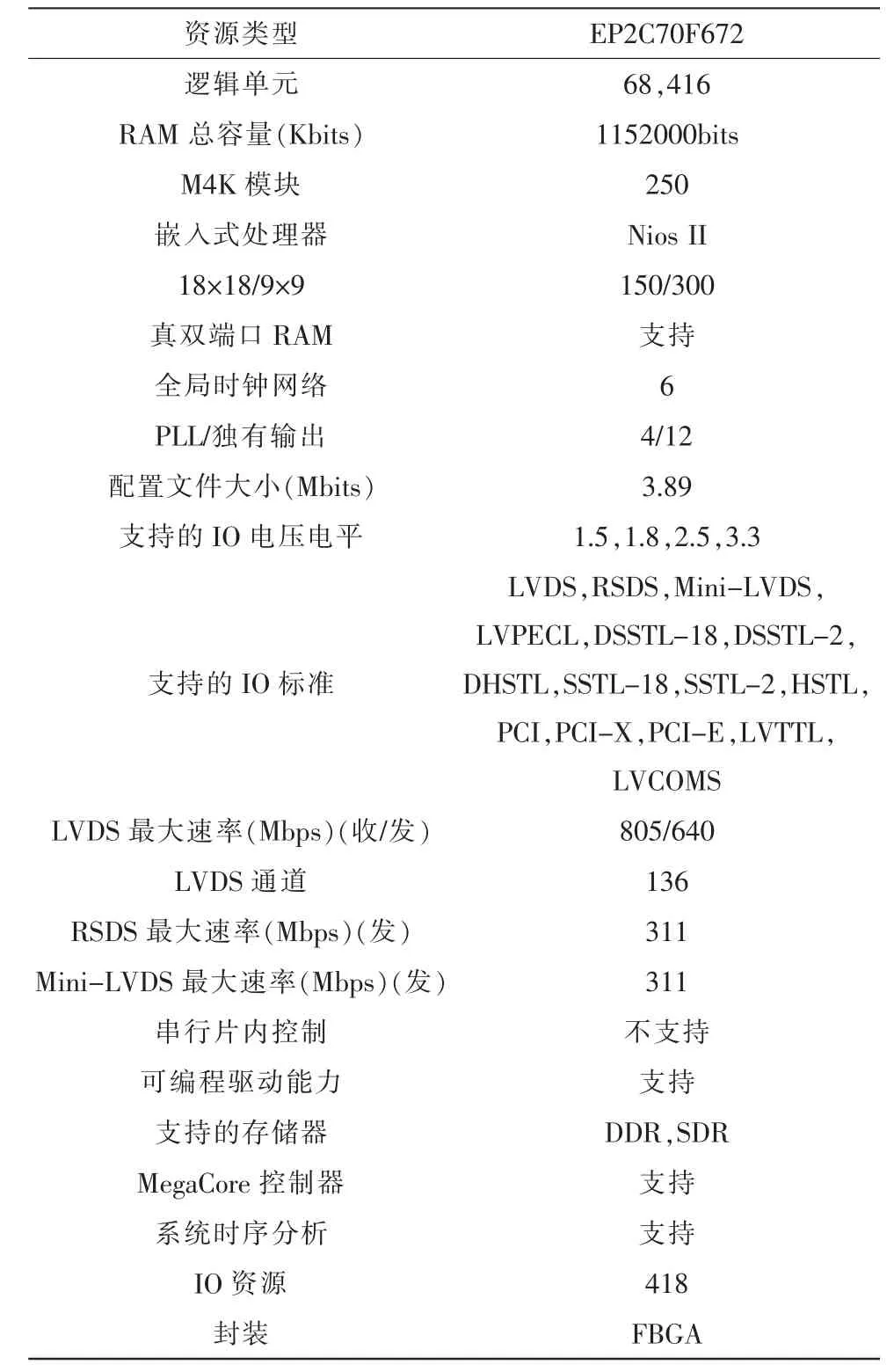

1.2AD9762简介

AD9762是AD公司的一款低功耗数模转换芯片,最高采样率可达125M,12bit输入。供电电压在2.7 V到5.5 V之间,AD9762的内部结构框图如下所示:

图2 FPGA的JTAG配置方式电路Fig.2 FPGA JTAG installs way electric circuit

图3 AD9762内部结构框图Fig.3 AD9762 internal structure frame diagram

2 调制器原理及其实现

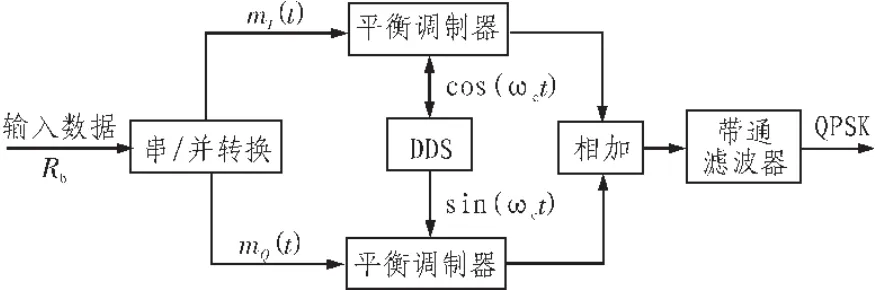

QPSK信号是多进制数字频率调制的一种,它基本上是二进制数字频率键控方式的直接推广。QPSK信号的产生方法,可以分为调相法和相位选择法。

1)调相法

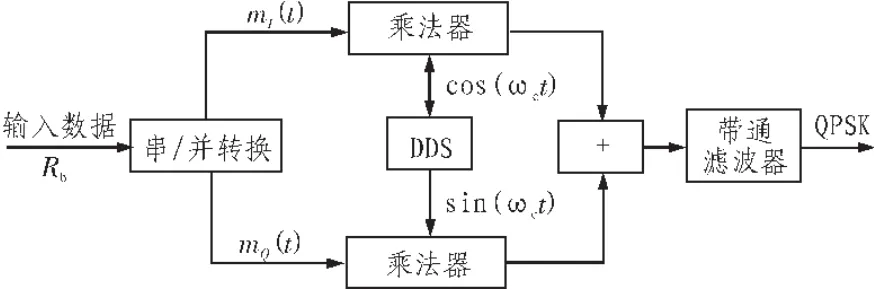

用调相法产生QPSK信号的组成方框图如图4所示。单极性二进制消息流比特率为Rb,首先用一个单极性-双极性转换器将它转换为双极性归零(NRZ)序列。然后比特流m(t)分为两个比特流mI(t)和mQ(t)(同相和正交流),每个的比特率为Rs=Rb/2。比特流mI(t)叫做“偶”流,mQ(t)叫做“奇流”。两个二进制序列分别用两个正交的载波cos(ωct)和sin(ωct)调制。两个已调信号每一个都可看作是一个BPSK信号,对它们求和产生一个QPSK信号。

调制器输出端的滤波器将QPSK信号的功率谱限制在分配的带宽内。这样可以防止信号能量泄漏到相邻的信道,还能除去在调制过程中产生的带外杂散信号。

2)相位选择法

图4 调相法组成框图Fig.4 Adjust mutually a method to constitute frame diagram

用相位选择法产生QPSK信号的组成方框图如图5所示。图5中,四相载波发生器分别送出调相所需的4种不同相位的载波。按照串/并变换器输出的双比特码元的不同,逻辑选相电路输出相应相位的载波。

图5 相位选择法的组成框图Fig.5 Mutually chooses a method of constitute frame diagram

本文调制器采用调相法实现,是通过 EP2C70进行VHDL编程,并使用内部的dds核产生 cos信号,并送给DA9762进行数模转换完成调制的功能,其FPGA实现原理框图如下所示。

3结论

图6 QPSK实现原理框图Fig.6 QPSK carries out principle frame diagram

器的可行性,通过对设计结果分析达到了低功耗、小型化调制器的设计目的,减小了设备体积、降低了设备功耗,节约了

能源,解决了目前大体积、大功耗调制器的瓶颈。

[1]王兴亮.数字通信原理与技术[M].2000,索书号:TN914.3/4. [2]樊昌信,张甫翊,徐炳祥,等.通信原理[M].北京:国防工业出版社,2001.

[3]胡广书.数字信号处理理论、算法与实现[M].北京:清华大学出版社,2006.

[4]苏涛,何学辉,吕林夏.实时信号处理系统设计[M].西安:西安电子科技大学出版社,2006.

[5]王建平,张宝剑,王军涛.通信原理[M].北京:人民邮电出版社,2007.

[6]张欣.扩频通信数字基带信号处理算法及其VLSI实现[M].北京:科学出版社,2004.

本文说明了利用低功耗、小封装的芯片实现低功耗调制

Consume according to the low achievement of the AD9762 and the EP2C70 light turn to make a machine of design and realization

JI Chun-guo,LU Dan

(Five Hospitals of Aerospace Science and Technology Group Company are 513,Yantai 264003,China)

This text consumes according to the low achievement,light turn the purpose of making the machine,adopted a low achievement to consume,small the FPGA and DA chip for packing,namely the design thought of AD9762 and EP2C70 consociation,give QPSK make principle and engineering of machine to carry out a method;Made use of the method of FPGA software plait distance to carry out QPSK that the number turns to make a machine,and carry out number to arrive the conversion that imitates signal through an AD9762,obtained to make a machine low achievement consume,small scaled turn, come to a to design a purpose,satisfy an applied need.

make a low;achievement to consume;DDS;light turn;FPGA

TN91

A

1674-6236(2016)03-0109-03

2015-03-01稿件编号:201503006

纪春国(1981—),男,山东烟台人,硕士,高级工程师。研究方向:信息与通信工程。