基于PXI的时序信号监测设备设计

卢逸斌,吴睫,王楠,唐亮

(1.上海宇航系统工程研究所 上海 201109;2.上海航天电子技术研究所 上海 201109)

基于PXI的时序信号监测设备设计

卢逸斌1,吴睫2,王楠1,唐亮1

(1.上海宇航系统工程研究所 上海 201109;2.上海航天电子技术研究所 上海 201109)

为满足飞行器时序信号监测的需求,采用了基于PXI总线的时序信号监测设备的设计方案,阐述了设备构成、PCI接口、信号隔离、PCI总线通信等方面的原理,利用LabVIEW开发平台完成了各种界面显示、数据处理、数据传输等功能。结果表明,该设备具有高便携性、高可靠性、高可维修性、数据分析能力强大等特点,满足各项飞行器测试的需求。

PXI;PCI;时序信号;监测设备

时序信号监测设备主要用于飞行器火工品信号、时序指令等信号的监测,是飞行器地面测试的重要组成部分。针对该设备对便携性、可靠性要求较高的特点,采用基于PXI总线的测试技术的一体式设计,充分考虑各种故障模式下的备份应急措施,保证设备的稳定工作。

PXI(PCI Extensions for Instrumentation)是面向仪器的PCI扩展总线,由美国NI公司推出。它使用了PCI总线的电气特性,并结合了CPCI的坚固性、模块化、机械封装等特性。同时,增加了专用的同步总线,是目前测试领域应用最广泛的总线之一。

1 系统设计

时序信号监测设备采用一体式的PXI机箱,包含显示器、鼠标、键盘等,可以完成数据处理、保存、监测、打印等功能。设备配置采集板卡和数据处理板卡,可以满足时序最大通道数测试的需求。

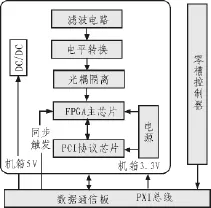

每块数据采集功能板可以同时完成16路时序信号的输入和处理,并进行模拟滤波,滤除60 μs脉宽以下的干扰信号。6块采集功能板共完成96路信号的采集,并分别与数据处理功能板相连,通过板上的FPGA进行采集和处理,再通过PXI总线把采集到的数据传输给PXI零槽控制器[1-2],具体如图1所示。

图1 时序信号监测设备组成图Fig.1 Diagram of signal monitoring equipment

2 硬件设计

2.1CPCI接口设计

PCI总线协议采用通用的PCI9054接口芯片,芯片内部集成了满足PCI时序的逻辑电路,可以完成PCI主控模块和目标模块的各项功能,将繁复的 PCI总线接口转换为相对简单的客户接口[3]。

2.2信号输入隔离板卡设计

16路信号输入隔离板卡电路如下图所示。信号输入隔离卡由子母板组成,子板负责信号的处理,脉宽Vin输入电压为0~32 V,经信号调理、光耦隔离以及电平转换后,送入板间接口。

母板为FPGA与PCI9054组成的总线协议板,从通用板间接口处接收子板输入的信号,判读脉冲信号,脉宽宽度小于60 μs,由FPGA自动滤除。

PCI9054负责与零槽的数据交换,当收到数据采集指令后,板卡开始采集信号,将脉冲信号到达的时间,脉冲宽度,保存至板卡的FPGA内存中,再通过零槽实时读取,具体如图2所示。

图2 信号输入隔离板卡原理框图Fig.2 Principle diagram of the signal input isolation board

输入隔离板卡采用硬件滤波和软件滤波相结合的去干扰措施。在硬件设计中,各个功能板脉冲采集接口处设置100 μs的滤波[4]。在软件处理中添加延时,在FPGA的逻辑代码中,设置脉冲采样时钟,进行数字滤波。

2.3FPGA读写PCI总线

FPGA作为开发板的控制模块,主要实现PCI局部总线的时序以及对SRAM的控制。FPGA实现PCI局部总线时序是通过一个状态机来完成的,如图3所示。

图3 PCI局部总线的状态机示意图Fig.3 Diagram of the PCI local bus state machine

当LLAD#=0时,说明PCI主设备发起一次访问,FPGA根据 LLW/R#来判断是读操作或是写操作,然后根据其值配置RAM控制信号,即RCE、ROE、RWE 3个信号,并将LLA [14:0]的值写入RAM的地址线,这时读/写操作的配置阶段完成,状态机从状态 0跳转到状态 1[5]。状态 1进行读写操作并根据LLBLAST#的值来确定是否是最后一个读/写周期,若不是则设置LLREADY#信号为 1,继续读/写操作,并返回状态1,若 LLBLAST#=0则表示最后一个操作周期,设置LLREADY#信号为0,读/写操作结束后转入状态 0,并不断检验LLAD#的值,等待新的读/写周期。由于PCI总线功能开发板是单一的从设备,不存在设备忙状态,因此对申请本地总线信号总是立即应答,即在编写 FPGA的逻辑时总是将LLHOLD的值带入LLHOLDA[6]。

3 软件设计

计算机显示模块采用NI公司的LabVIEW 2013平台进行开发。可切换查看不同前端嵌入式设备的显示信息,并且保存显示的测试数据,用于事后分析。

软件分为2个模块,一个用于显示数据备份板卡的RS-485发送数据;另一个用于前端显示,加载在时序测试设备机箱上,并可通过以太网与外部设备通信。

测试人员可以通过主界面了解测试详情,通过修改配置文件,调整嵌入式测试设备的显示界面,并可以根据脉冲到来次数更换显示灯的颜色等功能。软件预读取相应状态的配置文件,可以根据理论数据进行自动判读。同时,通过界面切换可以进行数据的曲线形式显示和回放。

时序测试设备通过以太网口与后端进行通讯,当程序开始执行后,相应后端发出的运行信号,软件和FPGA电路进行相应的执行,等待各通道的信号,没有信号到来则保持原样,软件采用循采的模式执行,发现信号变化则立即显示,并把FPGA上的缓存数据进行读取。

4 结 论

时序信号监测设备以PXI总线技术为核心,结合了FPGA、LabVIEW等技术手段,实现对时序信号的高速可靠采集。同时采用了一体式的设计思路,增强了设备的整体性和便携性。目前已应用于多个飞行器型号的地面测试,大幅提高了测试的效率及有效性。

[1]黄现.基于PXI平台的FPGA高速自动化测试系统设计[J].复旦大学,2013(8):5-9.

[2]韩大伟.基于PXI总线的导弹自动测试系统设计[J].计算机测量与控制,2008(11):115-117.

[3]刘鑫.CompactPCI总线工控机技术的现状与应用[J].电子技术应用,2002(7):81-84.

[4]李睿鹏.基于PXI总线的半实物仿真系统的设计与实现[J].电子设计工程,2015(1):43-44.

[5]甄国涌.基于PXI接口多通道信源卡设计[J].计算机测量与控制,2014(10):23-26.

[6]张猛.基于LabVIEW的推进系统通用试验台设计[J].测控技术,2014(12):49-51.

Design of pulse signal monitor equipment based on PXI technology

LU Yi-bin1,WU Jie2,WANG Nan1,TANG Liang1

(1.Shanghai Aerospace System Engineering Institute,Shanghai 201109,China;2.Shanghai Aerospace Electronic Technology Institute,Shanghai 201109,China)

In order to meet the needs of aircraft pulse signal monitoring,This discourse use a design of pulse signal monitor equipment based on PXI technology,expounds the equipment constitution,PCI interface,signal isolation,PCI bus communication,using LabVIEW development platform,completed a variety of interface display,data processing,data transmission and other functions.The results shows that,this equipment has high portability,high reliability,strong maintainability data analysis ability etc,it can meet the aircraft testing needs.

PXI;PCI;pulse signal;monitoring equipment

TN98

A

1674-6236(2016)03-0076-02

2015-03-21稿件编号:201503291

卢逸斌(1982—),男,上海人,工程师。研究方向:飞行器综合测试系统设计。