基于Hi3531的视频存储与回放电路的设计

金永明(中国电子科技集团公司第五十五研究所,南京 210000)

基于Hi3531的视频存储与回放电路的设计

金永明

(中国电子科技集团公司第五十五研究所,南京 210000)

本文描述了基于Hi3531处理器为核心的视频存储与回放电路的设计,介绍了电路中重要功能模块设计,同时对与电路相关的驱动软件进行了规划。本电路实现方便,具有一定的使用价值。

Hi3531;视频;存储

0 引言

随着计算机应用领域地不断扩展,现在人类在工作、学习、生活过程中越来越依靠计算机应用提供的便利,提高工作效率、改善生活质量、激发学习乐趣。因此,对计算机上应用及操作的监控也是一个重要的研究方向,通过对计算机上应用及操作的实时监控,可以完成计算机应用及操作的事后评估、检索和取证,为检查计算机操作人员的工作准确性和合理性提供视频数据。

对计算机应用和操作进行视频扑获、存储和回放,需要对计算机应用和操作的视频监控。我们基于Hi3531芯片设计和实现了计算机视频存储和回放电路,可将计算机VGA视频信号扑获,存储在固态电子盘中,利用USB通讯口对存储视频进行回放,电路设计稳定高效,软件使用简易,在视频监控、视频分析、视频检索等应用中具有一定的使用价值。

1 电路原理设计

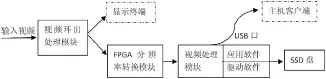

视频存储与回放电路中核心芯片为Hi3531,此芯片是华为公司针对多路高清 DVR、NVR产品应用开发的一款专业高端SOC 芯片。芯片中内置高性能双核A9处理器、可完成高达 5 路1080P 视频信号的实时多协议编译码以及专用TOE 网络加速,能应对越来越复杂的高清视频和高速网络应用。芯片内部集成了优异的视频引擎和编译码算法,结合芯片的多路高清显示输出能力,可以充分满足高质量图像体验。同时芯片有丰富的外围接口,满足不同项目设计接口的差异化,图1为视频存储与回放电路原理功能框图。

图1 视频存储与回放电路原理框图

图1中输入视频通过视频环出处理模块后,完成视频信号1:2复制、增强和A/D转换后,提供外部显示终端视频信号,同步提供后继FPGA分辨率转换模块和视频处理模块的视频源,在驱动软件和应用软件控制下,将数字视频信号存储在SSD盘中,供外部主机客户端检索、回放。

2 关键硬件电路设计

2.1VGA视频环出电路模块设计

目前计算机中使用最多的视频接口为VGA视频接口,其他DVI视频接口、PAL视频接口等可以通过商业化视频转换板变化成VGA视频接口,因此本文中视频存储和回放电路的设计以VGA视频接口为主。

在实际使用过程中,输入的VGA视频信号必须在显示图像的过程中,同步完成视频存储和回放处理。因此,VGA视频环出电路是输入VGA视频信号处理的重要电路。

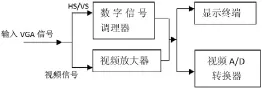

图2为VGA视频环出电路原理框图。外部输入的VGA视频信号中数字部分VS、HS信号通过数字信号调理器,完成数字信号整形、缓冲等处理后,增加了数字信号的输出功率和效率;VGA视频信号中模拟部分红绿蓝视频信号经过视频放大器后,完成了视频信号放大、复制、分配处理,同样也增加了模拟信号的输出功率和效率。输入的VGA视频信号完成上述视频放大和调理后,按照1:2分配给后续的显示终端和视频A/D转换器,可同步完成输入视频VGA信号实时显示和视频A/D转换。

图2 VGA视频环出电路原理框图

VGA视频信号中VS、VS信号是低于1MHz以下的信号,数字信号调理器采用74HC244等常用数字信号缓冲器,可以完成数字信号调理功能。

EL5364是600MHz高带宽电流回馈放大器,是视频信号处理应用中理想的放大器。同时,、电路芯片还可以完成VGA视频信号中模拟红绿蓝信号的1:2分配,设计中选用EL5364作为VGA视频信号放大器,完成VGA视频信号的放大和备份处理。

考虑到后续VGA视频信号存储和回放电路芯片只能处理数字信号,而且存储视频信号的物理空间为固态电子盘,也只能存储数字视频信号,因此必须对VGA视频信号A/D转换,变换成数字视频信号供后级电路处理。

ADV7842是一款高质量、单芯片、2:1多任务HDMI™接收器和图形数字化仪,并集成多格式视频译码器。该器件内置一个双路输入HDMI 1.4相容型接收器,支持最高达1080p 的所有高清电视格式,显示分辨率最高可达UXGA(1600×1200,60 Hz)。

ADV7842支持图形数字化,能够对VGA至UXGA 速率的RGB 图形信号进行数字化处理,将其转换为数字RGB 或YCbCr 像素输出流。

设计中通过ADV7842将VGA视频信号转换为BT.1120数字信号,传输给FPGA进行分辨率转换,转换后视频信号传输给主处理器进行编码压缩和存储。

ADV7842管脚中有INT中断输出,可以通过对芯片设置,使ADV7842特定的寄存器位变化及时反映到INT中断输出上,这样做可以实现外部输入信号分辨率变化时,FPGA和主处理器能够及时检测到,并采取相应处理。INT中断信号可设置为高电平或低电平有效。

设计中考虑到实际应用中,需要对多路VGA信号进行视频A/ D转换、存储和回放,需要多片ADV7842进行视频A/D转换。ADV7842的I2C地址固定无法设置,因此可通过I2C扩展芯片完成对多片相同地址ADV7842的配置工作,设计中采用主处理器I2C配置多片ADV7842,并行地对16路VGA视频信号进行了A/D装换,设计结果符合使用要求。

2.2FPGA分辨率转换电路模块设计

对计算机输入VGA视频信号进行存储和回顾,须兼顾对计算机启动全过程的录制。众所周知,以Windows操作系统为例,计算机在开机启动时VGA视频分辨率为640x480,操作系统启动完成后VGA视频分辨率变为操作系统默认分辨率,多数为高于640x480的视频分辨率。后继Hi3531芯片在视频输入接口的分辨率发生改变时,需要重新配置VI视频编码才可以完成不同分辨率视频信号的处理,但是相关程序模块运行所需时间较长。因此设计过程中,考虑利用FPGA将输入640x480分辨率的BT1120时序视频信号,通过硬件分辨率转换电路处理成操作系统默认分辨率的BT1120时序视频信号,再供给Hi3531进行编码存储,提高电路运行效率。

此外,FPGA进行分辨率转换后,当出现人员误操作、系统蓝屏等错误信息或者操作系统进入安全模式等引起分辨率变化时,FPGA分辨率转换电路可保证Hi3531视频输入接口的输入分辨率保持不变,FPGA分辨率转换电路实现方式:当输入视频分辨率低于默认分辨率时,通过加黑边的方式将其转换为默认分辨率。当输入分辨率高于默认分辨率时,FPGA转换电路利用GPIO脚实时通知Hi3531处理芯片,FPGA转换分辨率电路实时生成蓝屏提示视频代替异常分辨率视频信号,无缝连接地完成视频存储的连续性,同时还可从存储视频和GPIO两个方面对异常视频信号报警。

2.3视频处理电路模块设计

视频处理电路主要完成A/D转换后数字视频编码、存储工作,也是电路设计中核心部分,选择了Hi3531处理器进行视频处理。

Hi3531处理器是一个视频编码器,可支持H.264/ MPEG-4/JPEG的多协议编码器,处理器中包含VEDU等部分。VEDU(Video Encode Unit)是一个硬件实现的支持多种视频标准(包括H.264、MPEG-4等)的编码器。VEDU 具有CPU 占用率低、总线带宽占用小、低延时、低功耗等优点,最高可达16x960H/30fps+16x480x272/30fps 编码。支持图像分辨率可配置,最小图像分辨率160x64,最大图像分辨率7040x8176。

Hi3531处理器内置视频捕获单元VICAP(Video capture),视频扑获单元可通过多路BT.656(mux)/1120(mux)/601 接口或者DC(Digital Camera)接口扑获视频数据,存入指定的内存区域。在此过程中,VICAP可以对视频图像数据进行水平垂直缩小(根据通道情况能简单地采样或者是缩放)并输出多个不同的视频流。

VICAP 有以下特点:

输入最大分辨率为2560x1600

外部支持8 个BT656 接口,或 4 个BT1120界面

内部支持8 个端口和16 路通道视频处理,每个通道支持隔行和逐行输入模式;其中有8 路支持小码流输出

支持BT.656(mux),BT.1120(mux) ,BT601 ,DC等时序

支持SMPTE293M/ITU-R BT.1358时序(480P/576P)

支持BT.601 时序

支持SMPTE 274M/BT 1120 时序(1080i/1080P)

支持SMPTE 296M(720P)

支持最大16 倍的水平和垂直缩小

各信道支持3 级总线优先级可配

支持在一个指定窗口内获取数据

支持水平镜像和垂直镜像

输出格式支持存储模式:SPYCbCr 4:2:0 和SPYCbCr 4:2:2模式。

Hi351处理器的VDP(Video Display)模块主动从内存相应位置读取视频和图形数据,将视频层和图形层数据迭加后通过显示信道送出,支持后继视频信号数字化存储,为视频信号数字化存储提供了硬件基础。

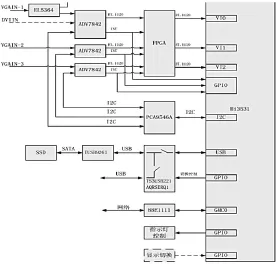

图3为基于Hi3531处理器的视频处理电路原理图。输入VGA视频信号通过视频环出、视频A/D变换、分辨率转换等处理后,数字视频信号进入Hi3531处理器相应部分,完成视频处理的硬件搭配,结合处理器内部程序可完成视频扑获、存储等功能。

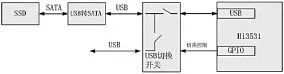

2.4SATA转USB电路模块设计

如图3所示,视频处理后的数字信号存储在SSD固态电子盘中,可以提高数据访问的便捷性和可靠性。考虑到USB通讯接口不仅使用方便,而且传输数率较高,因此设计中采用USB通讯口作为视频数据对外传输接口。Hi3531处理器没有USB从设备接口,为了满足主机客户端通过USB通讯口读取固态硬盘视频数据的需要,在固态电子盘SATA数据接口与主机USB通讯接口之间,设计了如图4所示的SATA转USB的接口电路,Hi3531处理器和主机都可通过USB接口访问固态电子盘,USB切换开关实现了两者对电子盘控制权的切换,USB转SATA可实现通过USB接口访问控制固态电子盘。

图3 基于Hi3531处理器的视频处理电路原理图

图4 SATA转USB接口电路

图4中SATA转USB接口电路工作模式如下:正常扑获、存储视频数据时,固态电子盘SATA接口通过USB转换电路后,接入Hi3531处理器的USB接口;当主机要通过客户端回放、导出固态电子盘中存储的视频数据时,客户端应用软件通过默认控制命令,Hi3531处理器解析命令,通过USB切换开关电路将固态电子盘控制端切换到主机端,关闭上述视频扑获、存储通道,此时主机端获得了对固态电子盘的访问权,从而提供了客户端软件对视频数据的回放、导出的硬件基础。

3 处理器驱动软件设计

在本电路设计中,不仅包括核心芯片Hi3531处理等硬件电路设计,还包括Hi3531处理器内部驱动程序开发,驱动程序能够控制、协调Hi3531处理器,按照设计要求对输入视频扑获、存储和回放。

Hi3531处理器作为ARM9体系的嵌入式高端芯片,驱动程序开发环境采用Cmake项目源码工程编译管理工具和TortoiseGit项目源码管理工具,程序编译在Linux操作系统上采用公共交叉编译。

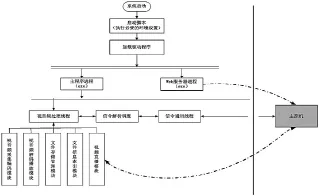

图5为根据视频存储和回放的设计要求,规划的Hi3531处理器驱动程序运行次序图。

图5 Hi3531处理器驱动程序运行次序图

根据图5的Hi3531处理器驱动程序运行次序图,Hi3531处理器软件运行顺序如图,分为以下6个步骤:

步骤1:启动,执行必要的启动脚本来初始化业务软件的运行环境,

步骤2:加载必要的设备驱动程序(RTC、音视频接口、USB、 SATA等)。

步骤3:启动主程序进程,Web服务器进程。主程序进程开启处理器视频编码模块,此工作模式为视频存储模式。

步骤4:“信令通讯线程”接收到信令后,解析信令,依次执行命令,如信令为开启反演状态,则进入步骤5.

步骤5:开启处理器视频解码进程,从SSD盘中获取反演文件,解码输出,工作模式为存储视频回放模式。

步骤6:循环执行步骤4。

按照软件设计和实现功能,处理器软件主要分为音视频采集编码模块、音视频解码播放模块、文件存储管理模块、文件信息索引模块和视频直播模块,每个软件模块的功能划分如下:

音视频采集编码模块主要负责音视频采集编码工作,其中分为芯片驱动层、输入管理层、编码层、输出管理层、附属信息层等几个部分。芯片驱动层负责驱动音视频采集芯片,使其能够适配音视频编码芯片的输入时序要求,音频为I2S总线、视频为BT.1120时序。输入管理层负责调整音视频编码芯片Hi3531的音视频输入管理通道,使其工作在预先配置的工作模式。输出管理层:负责音视频输出配置管理,及标识管理等。编码层主要是配置启动Hi3531 SDK中的视频编码模块,音频的编码层部分负责把接收到的PCM裸流,进行立体声融合、声道分离等数据预处理。音视频编码流,目前设计为直接通过数据流转模块,裸流存储,需要导出时,调用封装模块进行MP4等的封装导出。附属信息层包括采集时间戳管理、NTP时间戳管理。

视音频解码播放模块接收主机端传来的指令,解码播放相应通道、相应时间的视音频数据到视音频输出接口。此模块还响应主机端下发的录制任务、文件列表查询等功能。

文件存储管理模块的主要功能是管理存储介质内的文件存储、文件空间管理、文件导出管理、文件满报警、文件自动清理等功能。该模块能够为视音频采集编码模块提供分割、存储等功能;能够为视音频解码播放模块提供文件查询,文件读写,文件导出、文件缓存等功能。文件的存储文件类型为MKV。使用ffmpeg进行MKV封装。按照一定的编码帧数,定期更新mkv文件头的信息。可保存记录到断电时刻之前的视频。模块监控内置的SSD盘存储空间,在存储空间写满后,存储视频数据进行循环覆盖,记录最新的数据并删除最早的数据。

文件信息索引管理模块能够自动收集、扫描并管理文件存储管理模块的文件内容信息,并保持索引信息与存储文件的真实对应,同时该模块还具有统计录取文件及时长、已录取总时长等功能。

视频直播模块通过内嵌商业化成熟的音视频播放软件,如暴风影音等,在主机客户端对存储在SSD盘内的视频信号进行播放,对输入视频信号实时监控。

根据上述处理器驱动软件规划和设计,可以进行驱动软件详细设计,完成符合设计和使用要求的电路配套软件。

4 结论

基于Hi3531处理器的视频存储与回放电路设计和架构较简洁,电路实现重点在Hi3531处理器驱动软件部分。图6左半部分为本单位设计和实现的三路VGA输入的视频存储与回放电路板,图6右半部分为三路VGA输入的视频存储与回放电路测试效果图,从电路系统测试效果图看,本电路在视频监控、检索、回放等方面具有一定的使用价值。

图6 基于Hi3531处理的视频存储与回放电路板(左)和测试效果图(右)

[1]深圳海思半导体有限公司.Hi3511 H.264编解码处理器用户指南[Z].深圳:深圳海思半导体有限公司,2008.

10.16640/j.cnki.37-1222/t.2016.14.135

金永明(1972-),男,硕士,高级工程师,主要从事加固显示器相关视频电路和软件开发和设计工作。