DP与DVI接口在4K显示器上叠加显示的电路设计

金永明,蒋 韬(中国电子科技集团公司第五十五研究所,南京 210000)

DP与DVI接口在4K显示器上叠加显示的电路设计

金永明,蒋 韬

(中国电子科技集团公司第五十五研究所,南京 210000)

本文描述了DP和DVI接口在4K显示器上叠加显示的电路设计原理,提供了基于STDP9320电路芯片为核心的电路实现,同时对与电路相关的驱动软件进行了规划。本电路不但功能和性能稳定,同时电路设计和实现方便,具有一定的使用价值。

DP;DVI;叠加显示

0 引言

2014年以来,显示器领域发展的最大亮点:4k(分辨率3840*2160)显示器量产化和商业化。随着4K显示器的普及,显示器接口也同步发展中。DP(Display Port)视频接口升级到1.2版本后,从数据吞吐率等方面较好地适配了4K显示器显示器,成为4K显示器标配视频接口。

4K分辨率显示器的商业化应用,结合DP1.2视频接口标准确定,大大地推动了医疗高清显示、视频会议高清显示等高端应用。考虑到在上述显示领域DVI接口的大量使用,因此本文提出了DP与DVI视频接口在4K显示器上叠加显示的电路设计和实现,既可以充分利用已有的电子资源,同时可快速进行电子设备升级换代。

DP与DVI视频接口叠加电路主要以STDP9320视频处理芯片为主,通过两片STDP9320视频处理芯片级联,配合视频处理芯片内部控制程序驱动4K显示器视频显示,控制输入DVI视频信号的叠加显示,此叠加显示电路采用专用4k视频处理芯片完成视频叠加显示,电路功能和性能稳定可靠。在实际使用过程中,上述叠加电路用一定的实用价值和应用价值。

1 电路原理设计

本视频电路重点在4K显示器上完成视频叠加显示,因此电路核心为4K显示器视频显示。通过对商业化4K显示器驱动电路解剖和分析,确定目前市场上4K显示器视频驱动芯片主要采用:1,商业化专用视频处理芯片,如ST公司、MStar公司、Realtek公司等提供成熟技术的视频芯片;2非商业化视频处理公司采用FPGA以及专业视频内核,编程实现4K显示器视频显示。后期经过技术研讨和难度评判,结合上述两种技术路线的功能和性能对比,本视频电路采用ST公司新一代视频处理芯片STDP9320完成4K显示器视频显示。

STDP9320视频处理器是ST公司新的视频处理芯片,此芯片具有以下功能:

支持显示最大分辨率为2560x1600/60Hz

外部支持两路DP1.2(DisplayPort)视频输入

外部支持两路DVI视频输入,最大视频工作输率165MHz

外部支持24位TTL视频信号输入

输出视频信号最多4路LVDS

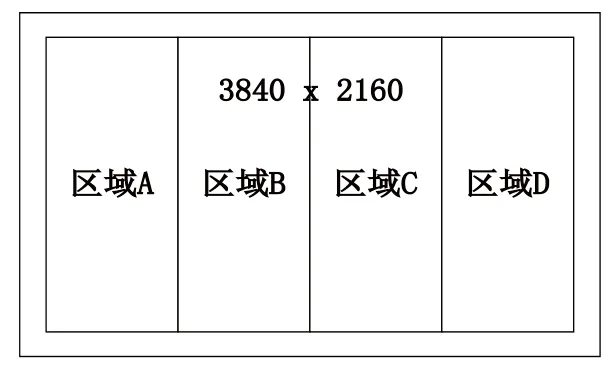

目前4K显示器分辩率一般为3840×2160,如图1所示本项目选用的4K显示器显示像素排列图。

图1 4K显示器显示像素配列图

4K显示器分辨率一般为3840×2160像素,显示器设计和生产厂家为了降低显示器工作视频时钟、功耗,以及显示器芯片设计难度,对4K显示器驱动采用如图1所示视频4路并行驱动方式,将显示器分为4个相同视频区间并行显示,每个显示区间为960×2160像素,通过上述并行视频处理方式,降低了4K显示器对视频驱动芯片的要求,符合目前视频芯片处理和发展水平。

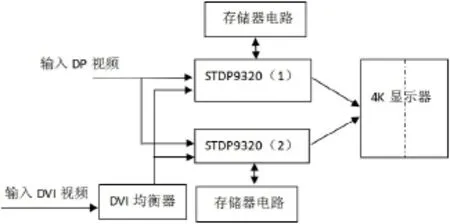

根据STDP视频芯片功能和4K显示器显示像素排列图,如图2所示为DP与DVI接口在4K显示器上叠加显示的电路功能图。

图2 DP与DVI接口在4K显示器上叠加显示的电路功能图

设计中考虑到,单片STDP9320最大驱动显示屏分辩率为2560×1600,显示屏的分辩率为3840×2160,因此需要两块视频处理芯片STDP9320才可驱动4K显示屏。项目设计要求输入DVI视频信号最小分辩率1024×768,DVI信号需在显示屏上、下、左、右四个角部叠加显示,结合4K显示屏4个分区像素划分,DVI信号单一叠加显示区间将会跨越显示屏的两个区域,设计中将4K显示器分成左右两个相同显示部分,每个显示部分为1920×2160像素,每个视频处理芯片驱动一个显示部分(分辩率1920×2160),如图2中所示的电路功能图所示,输入DVI视频信通过DVI均衡器电路后,分别进入两个视频处理芯片STDP9320后叠加显示,如此设计可支持最大1080P的DVI视频信号叠加显示。采用此视频分区驱动方法,可以简化软件设计,同时减少对视频芯片、高速电路设计的硬件要求。DVI均衡器电路能够支持DVI长线传输,存储器电路提供视频芯片数据暂存,完成视频信号处理。

2 关键硬件电路设计

2.1DVI均衡器电路设计

DVI视频信号输入到电路中叠加显示,如果视频电路对输入视频信号的适应性不好,显示器就会出现DVI视频画面不稳定、画面有杂点和水波纹等问题,严重的出现画面无显示,影响正常使用。因此视频电路对DVI视频信号的适应性设计尤为重要。

就数字信号DVI来说,DVI信号最初用来在短距离上传输视频和数据,其中电缆损耗的影响可以忽略。但是在工业级或特定领域应用时,很多应用要求采用更长的电缆,五米到十米甚至更长,由于显示分辨率、刷新速率和颜色深度的持续增加,所需的数据速率也随之增加。因此DVI长距离传输就会造成信号的劣化,出现衰减、抖动、偏移和串扰等信号问题,限制从源端到显示端之间的连接距离,出现屏幕闪光、噪声闪烁和音频失真。

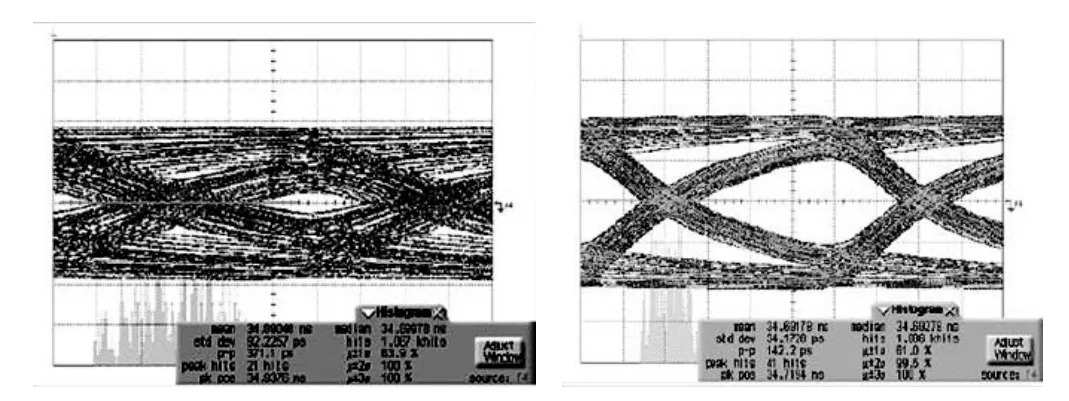

实际使用过程中,非常规DVI标准接口(如使用航插等)的长距离传输,会造成高分辨率(比如1600x1200)DVI信号的闪烁、噪点等故障,通过软、硬件均衡处理可支持高分辨率DVI信号长距离传输。硬件上采用DVI均衡芯片DS16EV5110对DVI信号做均衡处理,软件上配置TMDS均衡相关寄存器,编写硬件自动均衡代码,反复校验与修正,可使DVI信号在输入时能够保持稳定且不丢失数据。图3左图为加均衡器之前眼图很混乱,而图3右图为加均衡器之后眼图很清晰,DVI信号得到补偿和修正。

图3 加均衡器前后眼图的对比

DS16EV5110在设计中作为高通滤波器电缆均衡器,可有效地重新打开差分信号的眼图,DVI信号增益曲线与电缆的衰减曲线成反比,其它特性还包括使用SMBus接口(类似于I2C总线接口)或者3引脚外置接口(BST1/2/3)可编程八种级别的均衡增益。

信号的总体抖动(Tj)是由确定性抖动(Dj)和随即抖动(Rj)组成,使用DS16EV5110的增益曲线来匹配电缆在工作频率上地发送损耗地负效应,以此抵消确定性损耗(Dj),因为随机损耗(Rj)也非常重要,在设计DS16EV5110电路时必须使其具有合适的增益、带宽等综合性能,一般用3ps rms来提供优化整体性能。

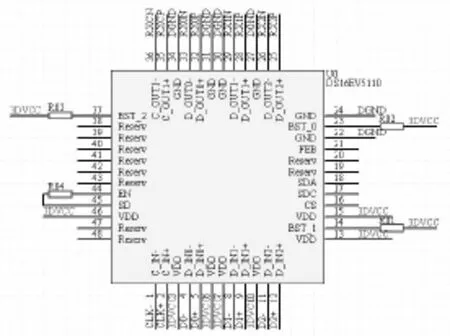

DS16EV5110硬件原理图如图4所示:

图4 DS16EV5110硬件原理图

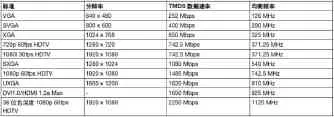

因为电缆衰减随频率增高而增加,应将均衡器的增益设定在可支持的最高分辨率上。表1列出了一些通用分辨率和与均衡增益相关的频率,该频率为数据速率的一半,由最差模式下1010数据模式产生。

表1 与TMDS数据速率和均衡频率相关的常用分辨率

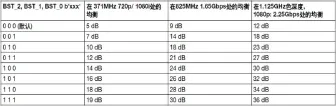

使用SMBus接口或使用提供的三种外置引脚来配置增益设定,EQ增益控制表如表2所示:表1为对应三种关键分辨率的均衡器增益,可以看出DS16EV5110的增益曲线斜率根据分辨率而变化,来自动提供较低的增益。在DVI视频通路上加上DS16EV5110可以均衡确定性抖动和衰减,并不会对来自噪声输入的扰动和随机尖峰作补偿。

表2 EQ增益控制表

2.2STDP9320视频处理器电路设计

如上文所述,驱动4K分辩率显示器需要两块STDP9320视频处理器并联配合,无论输入的DVI视频信号,还是DP视频信号经过前级处理后,分别接入到两块STDP9320视频处理器中,通过STDP9320视频处理内部驱动程序,完成DVI和DP视频信号叠加显示。

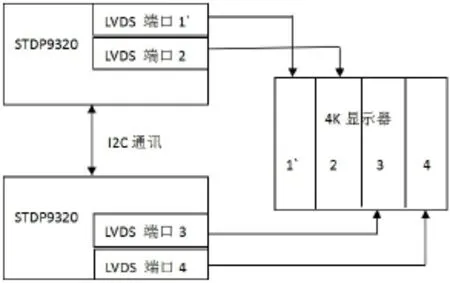

STDP9320视频处理器对外输出视频LVDS接口共有4路,为简化设计难度,减少后续视频处理器驱动软件编写难度,一块STDP9320视频处理器输出LVDS端1/2驱动4K显示屏左半部分,另一块STDP9320视频处理器输出LVDS端口3/4驱动4K显示屏右半部分,如图5所示视频处理器输出LVDS端口驱动4K显示屏示意图。

图5 视频处理器输出LVDS端口驱动4K显示屏示意图

通过图5所示,视频处理器输出LVDS端口驱动4K显示屏示意图,DVI在左半和右半部分显示分别由一块视频处理器STDP9320完成,DVI输入视频分辨率能够到达1080P,避免了DVI视频信号跨区间显示难度。

两块STDP9320视频处理器在电路中,分成主从配置结构,采用I2C总线交换数据完成主从设备通讯,协调DVI视频信号叠加显示位置、视频处理器输出LVDS端口开关设置等。

视频处理器具有较高频数字电路,因此设计中需要注意PCB板的高频设计,恰当的布局布线和安装来实现PCB的高频阻抗匹配设计。采用紧密交织的电源和地栅格;电源线紧靠地线,在垂直和水平线和填充区之间,尽可能多地连接;I/O电路尽可能靠近对应的连接器;对易受ESD影响的电路,放在靠近电路中心的区域,这样高频电路可以提供一定的高频阻抗匹配。PCB设计中需保证信号线尽可能短。信号线的长度过长(比如大于300mm)时,平行布一条地线;确保信号线和相应回路之间的环路面积尽可能小。对于长信号线每隔几厘米调换信号线和地线的位置来减小环路面积。确保电源和地之间的环路面积尽可能小,提高高频电路阻抗匹配。

3 处理器驱动软件设计

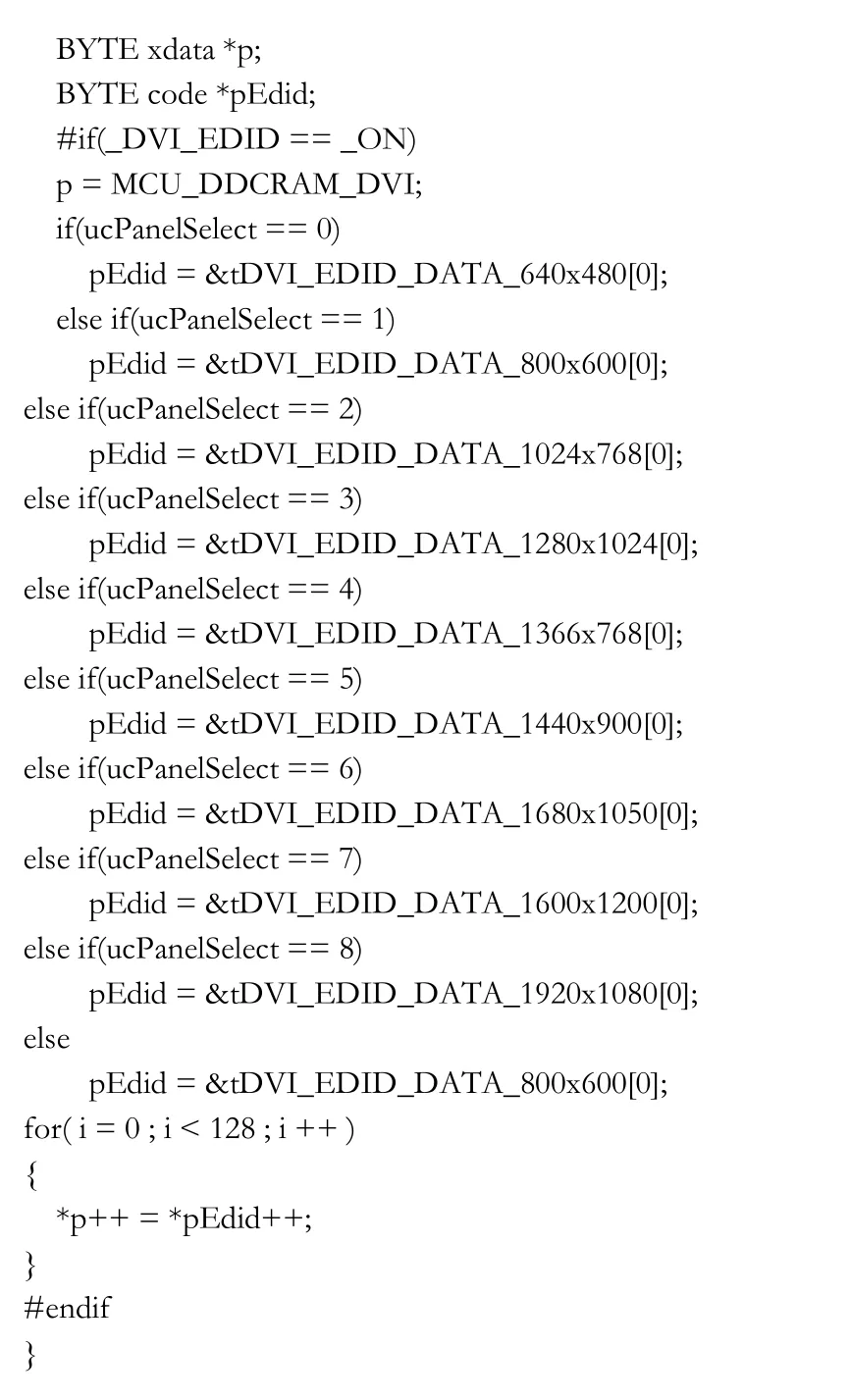

在视频处理器软件设计中,主要需要完成4K显示屏输出LVDS驱动、输入视频信号选择、多路视频信号叠加显示等功能,相应的软件需按照STDP9320内部寄存器设置流程和数据项进行编程驱动即可。主视频处理器STDP9320还根据使用环境配置DVI均衡器电路,配置核心代码和函数构架如下:

变 量ucPanelSelect读 取 分 辨 率, 然 后 加 载tDVI_EDID_ DATA_1280x1024[ ]数组里128个字节EDID数据,通过DDC通道将其传输到视频处理器芯片RAM里,完成外部输入DVI视频信号读取和DDC数据获取工作。

4 结论

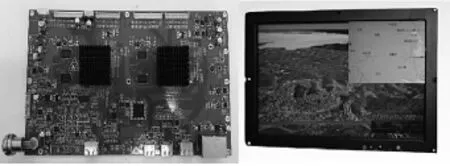

上述DP与DVI接口在4K显示器上叠加显示电路以STDP9320为主,通过两块STDP9320电路芯片主从配合和合理分配输出LVDS端口实现叠加显示,电路设计和架构较简洁。图6左半部分为本单位设计和实现的DP与DVI接口叠加显示电路板,图6右半部分为电路测试效果图,从电路系统测试效果图看,本电路在视频叠加显示、高清显示等方面具有一定的使用价值。

图6 视频叠加显示电路板(左)和测试效果图(右)

[1]ST半导体有限公司.STDP9320 3D功能高清多媒体监视器视频控制器数据手册[Z].ST半导体有限公司,2012.

[2]TI半导体有限公司.DS16EV5110 DVI均衡器数据手册[Z].TI半导体有限公司,2008.

10.16640/j.cnki.37-1222/t.2016.14.131

金永明(1972-),男,硕士,高级工程师,主要从事加固显示器相关设计工作。