多级流水线处理机的少课时实践内容设计

刘玉洁, 沈世全

(1. 中国民航大学 计算机科学与技术学院, 天津 300300;2. 厦门航空有限公司 杭州分公司, 浙江 杭州 310000)

多级流水线处理机的少课时实践内容设计

刘玉洁1, 沈世全2

(1. 中国民航大学 计算机科学与技术学院, 天津300300;2. 厦门航空有限公司 杭州分公司, 浙江 杭州310000)

以少课时教学为前提,基于FPGA技术设计了一个适用于本科生的多级流水线处理机的实践内容。通过精简处理机结构、缩减运算规模,设计了一个学生能够在有限课时内实现的多级流水乘法处理机,并提出了流水线瓶颈段问题的解决方案,收到了良好的教学效果。

多级流水线处理机; 实践内容设计;FPGA; 计算机体系结构

流水线技术是现代计算机系统设计中的关键技术,也是计算机体系结构课程中的重要内容。面对少课时的实践授课情况,设计出适合于本科学生计算机专业学生的流水线处理机的实践内容,有利于提高学生的系统设计能力,以及对CPU关键技术的掌握。

1 实验环境选择

对于流水线处理机的实践,一般可采用的方法有两种:一种是基于模拟器的设计方式;另一种是基于FPGA技术的设计方式。

基于模拟器下的设计方式,是在模拟器环境下,用程序来实现对流水线工作方式的模拟。常用的模拟器有WinDLX[1]、DLXView[2]、SimpleScalar[3]等。由于模拟器的特点,其设计出的多级流水线更接近于一段程序,而非CPU设计,难以让学生从本质上体会流水设计的意义。

基于FPGA技术的设计方式,要求学生利用可编程芯片,从指令系统开始,完成逻辑设计到物理实现的一台流水线处理机[4]。此方法学生的参与度高,设计过程能促使学生更加深入思考各部件间的联系与工作方式,但此方法对于本科学生而言工作量较大、设计难度较大[5]。

为了保证在少课时情况下的教学质量[6],本文在基于FPGA技术设计流水线的基础上,精简设计及运算规模,设计以突出流水线技术为主要目标的流水线处理机实践项目。

2 多级流水线处理机的实践内容设计

2.1精简的乘法流水处理机

运算规模越大、指令系统越复杂、控制复杂度越高,设计及实现需要的时间就越多,如浮点[7]、双精度、矩阵[8]等数据源的乘法运算。

故此在保证设计关键及难点不变的前提下,选用四位的数据流与地址流,以减小逻辑实现的规模,并摒弃复杂的控制[9],保留流水线必需的控制部分、时序部分、运算部分,输入/输出部分以及存储部分,形成一个精简的流水处理机。

2.2多级流水线的模块化设计

流水线设计的基本关键点是如何保证各部件在时间上的并行性。指令在流水过程中需被分解为若干子过程,这些子过程的功能由相应的部件完成。通过各部件时间均保持一致才能保证不同指令的子过程能够重叠成功。

流水线的基本结构包括三大部分:锁存器部分、时序部分、功能段部分[10]。功能段部分反映了流水线实现的功能,各功能段可以相互独立地对一些信息进行操作;在相邻的两个功能段之间用锁存器连接,用以保证各子过程的执行时间一致;传递的信息在各个功能段之间的传输由时序来控制。

在设计中,以子过程与基本结构的概念作为依据,进行模块化设计,各模块功能清晰、耗时相等,并可要求学生以顶层电路的方式体现出来。模块化可督促学生理清思路,并以小见大地理解多级流水线设计的一般规律。

2.3带有瓶颈段的三级流水线

根据流水线的模块化设计方法,以及二进制乘法的运算法则,设计流水线原理图见图1(a):流水线分为读RAM、逻辑与、逻辑加3个功能部件,中间以寄存器堆所构成的锁存器加以链接。时序部分则由时序发生器将系统时钟(clk)分频为t1~t4共4个节拍,为各部件提供内部时序脉冲。图中的BCD转码,是输出部分。为了便于观察,将8位二进制乘法结果,转码为BCD码,分3组显示[11]。

图1 乘法流水线设计

根据流水段原理图,在QUARTUSⅡ中实现乘法流水顶层电路图见图1(b)。在编码与调试成功之后,建立仿真文件[12]。设置仿真时钟clk周期为20ns,得到图2的仿真结果。从图2中可观察到每2拍(2个t4)读到一组A和B,1拍后推进到流水的下一级q0—q3。测试的乘法运算结果正确,且为每2拍输出一个结果。

图2 有瓶颈段乘法流水线的时序仿真

利用带有FPGA芯片插板的实验设备,将电路下载到CycloneⅢ系列芯片中,由该芯片实现乘法流水线处理机的功能,并将输出显示在实验设备的数码管上,见图3。图3中前3位显示的是3组BCD码的结果,第4个数码管显示的是时序,通过观察可判断时序与结果输出的关系为每2拍输出一个结果。学生亦可通过绑定不同输出端,观察流水线每一级的输出。

图3 数码管显示的运算结果

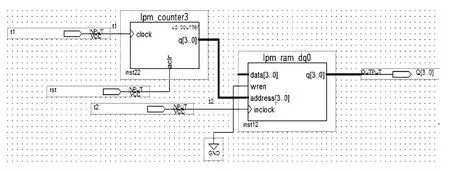

流水线每2拍输出一个运算结果的时序关系,说明流水线中有瓶颈段存在,且该瓶颈段的工作时长为2拍。在QUARTUSⅡ中分析乘法流水线电路图可知,“读RAM”段电路图(见图4),即地址1拍,读RAM1拍(此处为简化控制的目的,采取了由计数器产生地址的方式,非唯一方案)。故此共需2拍才能读出存储器中的内容,是整个流水线中的瓶颈段。

图4 “读RAM”段

3 流水线瓶颈段的解决方案

3.1流水线瓶颈段的消除

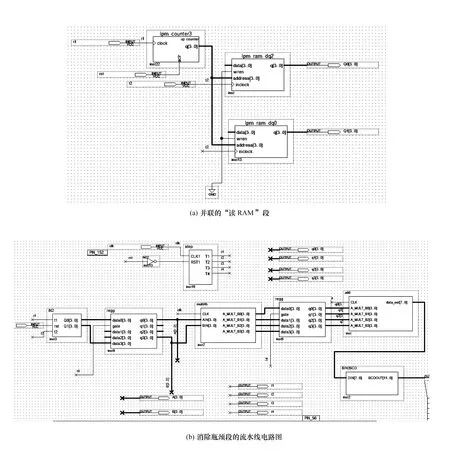

消除瓶颈段是流水线优化的一种常用技术[13]。消除瓶颈段有两种方法:瓶颈段再细分和重复设置多套瓶颈段。本文采用重复设置设备的方法来消除“读RAM”瓶颈段,需2套瓶颈段设备并联来实现瓶颈段的消除,则流水线原理图需修改为图5。

图5 消除瓶颈段的流水线原理图

并联的瓶颈段电路图见图6(a),设置2个“读RAM”,操作数A和B分别存在2个随机访问存储器RAM中。消除瓶颈段的流水段电路图见图6(b)。

图6 消除瓶颈段的乘法流水线

修改电路并编译成功后,以同一仿真文件、相同的设置对消除了瓶颈段的流水线进行仿真,得到仿真结果如图7所示。从图7中可观察到流水线每一拍输出一个结果,且测试的乘法运算结果正确。

图7 消除瓶颈段乘法流水线的时序仿真

下载至FPGA芯片后,在实验设备的数码管上,可直观地观察乘法流水线的运行结果。学生可观察各个乘法在流水线充满后,每一拍输出一个乘法结果。

3.2时空图及参数对比

配合理论课程内容,可要求学生画出消除瓶颈段前后的时空图,以计算2个流水线处理机的各项参数。带有瓶颈段的流水线的时空图[14]见图8(a),图8(b)则是消除瓶颈段后的流水线时空图。对比两图中可直

观看出同样进行4对乘法,消除瓶颈前需9拍,而消除后仅需6拍。图8(a)中可观察到流水线中除瓶颈段外,其他流水段并未充满,流水线利用率较低。图8(b)中各个流水段均充满。分别计算其各主要参数可得:带有瓶颈段的流水线吞吐率Tp≈0.44,加速比S≈1.78,效率E≈0.59;消除瓶颈段后吞吐率Tp≈0.89,加速比S≈2.67,效率E≈0.89。可以看到消除掉瓶颈段后,流水线的各项参数都有大幅度提高。

图8 乘法流水线时空图

4 实践的开放性和可扩展性

由于采取FPGA技术,此实践内容不仅具有适用于少课时教学的优点,而且也具备很好的设计开放性。乘法流水线处理机中,二进制乘法的逻辑实现方式多样,如阵列法、查表法、移位相加法、Booth法、判断压缩法等[15],在教学中可只给出实践目的和流水线设计的常用技术,不设置唯一的正确答案。学生可利用FPGA芯片设计灵活的特点,设计出不同的方案,有利于学生充分扩展思维。

另外,对于需求较高且有精力的学生,实践内容可以很方便地进一步扩展,如扩大运算规模为8位、16位,或增加指令控制功能,使精简的流水处理机变成一个能够执行简单程序的流水线处理机。

5 结语

基于FPGA芯片的乘法流水处理机,结构相对简单,运算规模小,流水线设计完整,在实际应用中收到了良好的教学效果。绝大部分学生可在2~3次实践课内依次完成带有瓶颈段的乘法流水处理机、消除瓶颈段的乘法流水处理机的全部设计与实现。确保了学生在少课时教学的情况下,切实地掌握流水线相关设计技术,保证了教学质量。

References)

[1]PattersonDA,HennessyJL.ComputerArchitecture-AQuantitativeApproach(SecondEdition)[M].MorganKaufmannPublishers,Inc,1996:112-250.

[2] 赵明波,陈平,林浩,等.DLX模拟器在计算机系统结构课教学实验中的应用研究[J]. 教育探索,2007(12):134-135.

[3]AustinT,LarsonE,DanE.SimpleScalar:AnInfrastructureforComputerSystemModeling[J].Computer,2002,35(2):59-67.

[4] 李志平,杨西珊,张俊方,等;基于FPGA的计算机系统实验教学平台的设计与实现[J].实验技术与管理,2009,26(9):77-80.

[5] 秘海晓.基于FPGA的32位五级流水线CPU的研究与设计[D].天津:河北工业大学,2012.

[6] 黎明,付扬. 少学时电工电子学课程教学改革探究[J].实验技术与管理,2010,27(11):292-294.

[7] 吕律,易清明,刘光昌. 基于FPGA单精度浮点乘法器的设计实现与测试[J]. 暨南大学学报:自然科学与医学版,2004,25(3):302-309.

[8]DouY,VassiliadisS,KuzmanovGK,etal. 64-bitfloating-pointFPGAmatrixmultiplication[C]//Proceedingsofthe2005ACM/SIGDA13thinternationalsymposiumonField-programmablegatearrays.ACM,2005:86-95.

[9] 张玲玲,李克俭,蔡启仲. 基于FPGA单指令浮点乘法自主控制器设计[J].计算机测量与控制,2014,22(10):3323-3326.

[10] 郑纬民,汤志忠.计算机系统结构[M].北京:清华大学出版社,1998:276-292.

[11] 邬杨波,胡建平,李宏. 一种BIN码与BCD码转换电路的设计与实现[J]. 信息技术,2005(8):33-35.

[12] 胡振华.VHDL与FPGA设计[M].北京:中国铁道出版社,2003.

[13] 杨海涛,孙燕. 消除瓶颈问题提高流水线效率方法的讨论[J]. 内蒙古民族大学学报:自然科学版,2004,19(6):621-622.

[14] 李学干.计算机系统结构[M].5版.西安:西安电子科技大学出版社,2011:178-196.

[15] 鞠芳,马昕,田岚.基于FPGA的数字乘法器性能比较[J].电子器件,2011,34(6):718-722.

Apracticaldesignformultistagepipelineprocessorinless-lessonsteaching

LiuYujie1,ShenShiquan2

(1.CollageofComputerScienceandTechnology,CivilAviationUniversityofChina,Tianjin300300,China;2.HangzhouBranch,XiamenAirlinesLtd.Co.,Hangzhou310000,China)

BasedonFPGAchipsandthetechnology,apracticaldesignisproposedfortheless-lessonsteachingofundergraduatestudents.Byreducingthearchitectureoftheprocessor,anddecreasingthescaleofcomputing,amultistagepipelinedmultiplicationprocessorisproduced.Andtheproblemofbottlenecksectioninpipelineissolved.

multistagepipelineprocessor;practicaldesign;FPGA;computerarchitecture

DOI:10.16791/j.cnki.sjg.2016.07.023

2015-11-24

中国民航大学教育教学改革研究项目“基于芯片设计的计算机体系结构的实践课程开发”(205002240220)

刘玉洁(1973—),女,天津,工学博士,高级实验师,研究方向为实践教学研究和计算机系统设计.

E-mail:yjliu@cauc.edu.cn

TP303;G642.0

A

1002-4956(2016)7-0096-04