新型高速大容量雷达数据记录器设计*

雷超群,苏淑靖*

(1.中北大学仪器科学与动态测试教育部重点实验室,太原030051;2.中北大学电子测试技术重点实验室,太原030051)

新型高速大容量雷达数据记录器设计*

雷超群1,2,苏淑靖1,2*

(1.中北大学仪器科学与动态测试教育部重点实验室,太原030051;2.中北大学电子测试技术重点实验室,太原030051)

设计了一种新型高速大容量雷达数据记录器的设计。为了将有效速度为59 Mbyte/s的雷达回波数据流及时、可靠的存储到记录器中,系统逻辑使用了乒乓缓存技术将其分解为两路速度为29.5 Mbyte/s的数据流并分别交叉写入两片FLASH,这样大大减轻了单片FLASH操作时序的压力。同时单片FLASH运用了交错式双平面编程和高效的无效块管理,极大的提高了芯片的写入速度。此数据记录器已经通过了振动、高低温、电磁兼容和冲击等实验,运行可靠稳定,同时已经交付部队使用。

高速存储;MT29F16G08AJADAWP;乒乓缓存;交错式双平面编程

在雷达回波信号的采集存储中,为了获取及时、可靠、高清的数据图像,雷达数据记录器必须在较短的时间内存储大量的数据[1-4],这就对记录器的存储带宽和存储容量提出了非常高的要求。本文借助某飞行器中雷达系统产生的高速视频、图像及遥测数据,同时为了解决传统的三星NAND FLASH早已停产和目前系统逻辑中所存在的问题[5],提出了一种基于镁光MT29F16G08AJADAWP型号的高速大容量数据记录器的设计。该记录器实现了实时记录雷达回波数据,同时可以通过地面测试台读取记录器中所存储的数据,以便进行后续的相关分析。

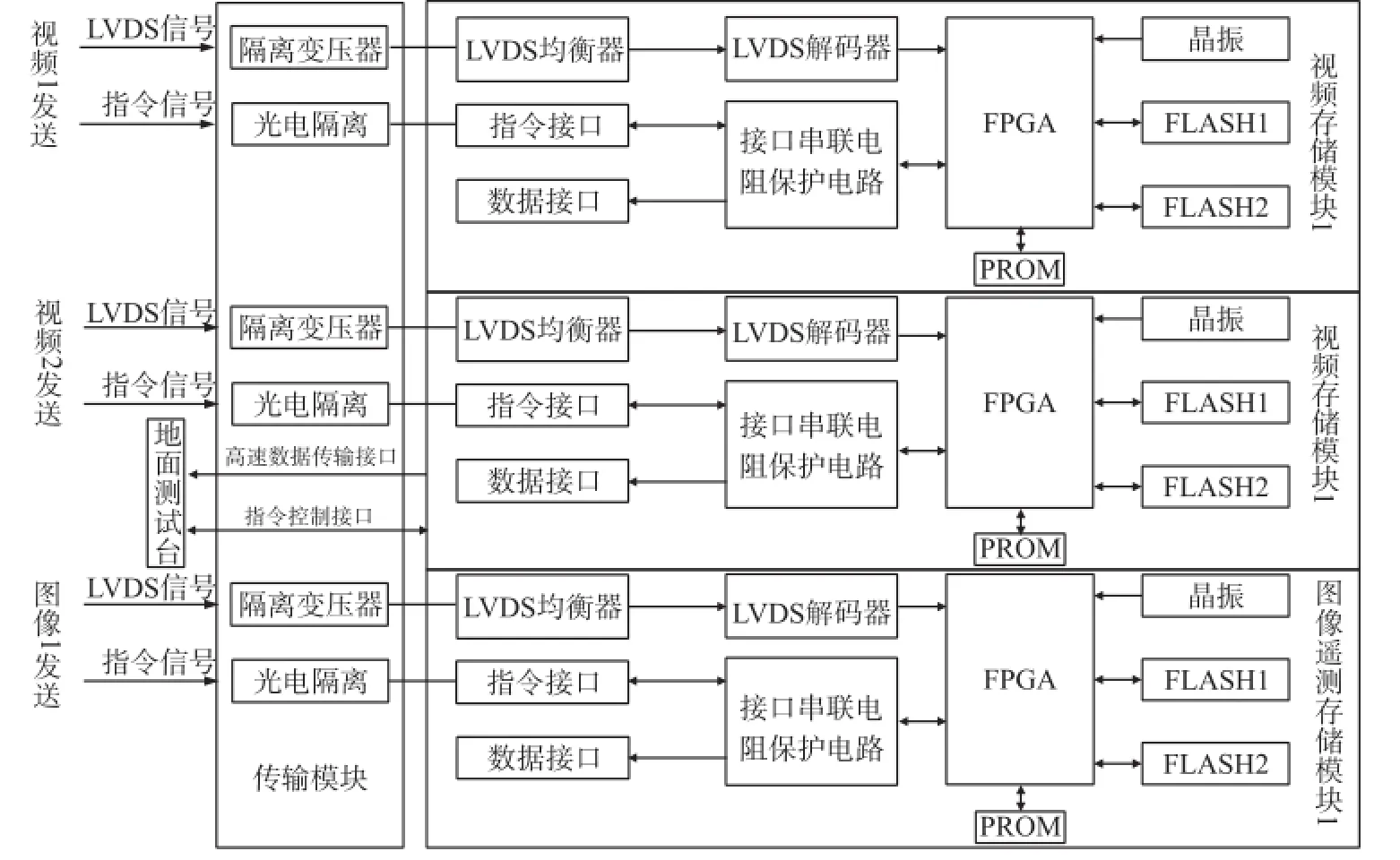

1 系统组成和工作原理

系统由上位机、地面测试台和数据记录器组成,其中数据记录器由1传输模块和3路存储模块组成,3路存储模块分别负责存储雷达回波信号中2路视频信号和1路图像信号,其内部组成如图1所示。

该记录器实现了对2路视频信号,1路图像信号进行实时记录并分别存储在3个存储模块中,3个存储模块使用了相同的电路结构。视频及图像数据输入模块分别采用变压器和光耦来隔离雷达系统发来的启动控制信号和测试台主控卡发出的请求信号、片选信号和读写信号。其中隔离变压器的设计使系统的输入与输出之间绝缘[6],提高了系统的抗干扰能力。LVDS信号进入存储模块后,通过电缆均衡器恢复,到达解串芯片,根据解串时FPGA给出的参考时钟,将并行数据暂存入FPGA内部FIFO中。经过内部的乒乓缓存操作[7],通过FPGA内部时序控制最后送入两片FLASH中进行存储。

项目来源:国家自然科学基金重点项目(51275491)

收稿日期:2015-03-31修改日期:2015-05-15

记录器有指令控制接口和高速读数接口。采用RS-422接口发送芯片DS26C31完成测试台指令的下发,包括复位、擦除、启动记录和读数等命令,验证记录器的工作是否正常,通过RS-422接收芯片DS26C32完成记录器回令的上传,提高了通信的可靠性。另外,通过高速读数接口可以快速地读取各个存储模块的数据至上位机中,进行数据的后续分析与验证。

图1 系统总体设计框图

2 系统逻辑设计

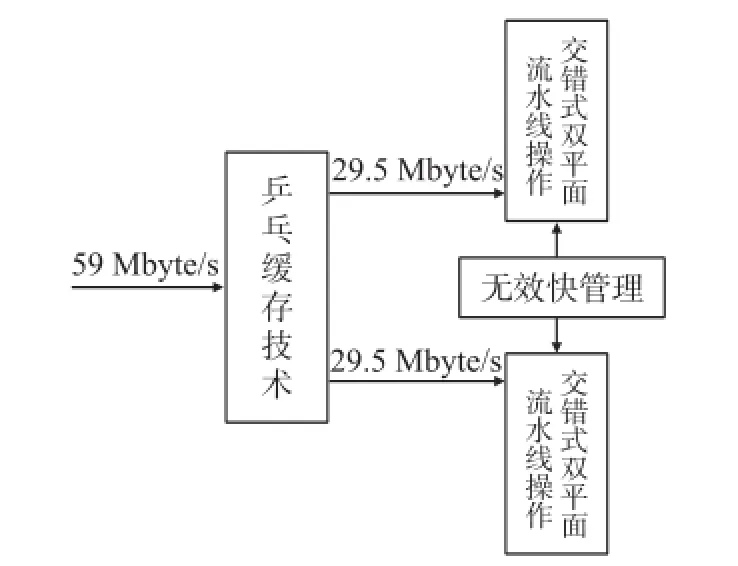

雷达系统产生两路视频、一路图像的高速数据信号,每路信号的传输速度为60 Mbyte/s,每100 μs内平均有效数据传输速度为59 Mbyte/s,为了实现高速存储,FPGA对FLASH的时序控制成为了最关键和最核心的问题。本设计使用了镁光最新生产的MT29F16G08AJADAWP型FLASH芯片,该芯片单片容量为4 G,芯片由两片(chip#1和chip#2)内存为2 G的MT29F8G08AJADAWP组成,分别由CE1和CE2选通,每个chip由2个逻辑单元构成。整个FLASH芯片由4个逻辑单元组成,这就为流水线交错式双平面编程提供了结构基础。其中一个逻辑单元由两个平面组成,一个平面由2 048块组成,64页组成一块,一页由2 kbyte构成,FLASH是以页为单位读写,以块为单位擦除。为了能够实时存储雷达系统产生的回波数据,整个存储模块必须保持最高59 Mbyte/s的有效写入速度。本设计利用了乒乓缓存技术的面积与速度的互换原则使单芯片的有效写入速度降低为29.5 Mbyte/s,通过运用流水线交错式双平面编程和高效的无效快管理,可以使单芯片的理论有效速度达到29.68 Mbyte/s,满足我们的技术指标。其逻辑结构如图2所示。

图2 系统逻辑框图

3 关键技术的研究与实现

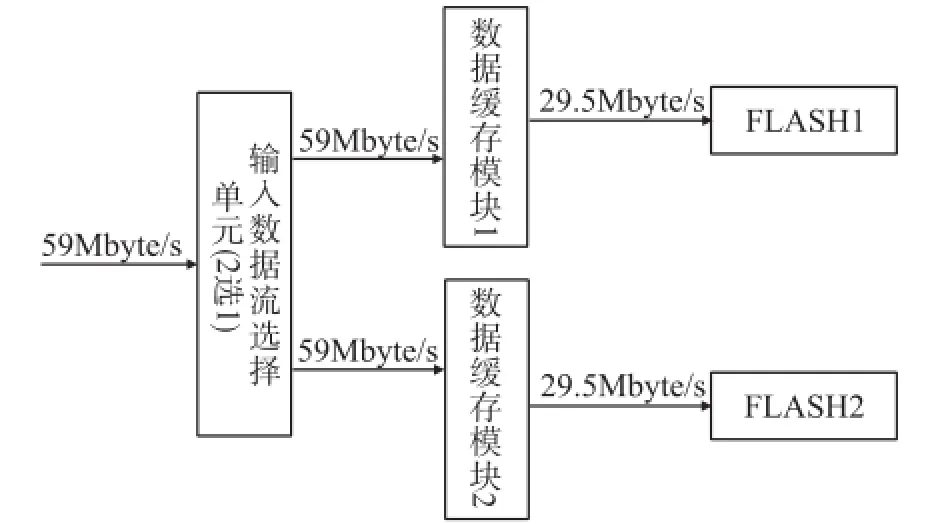

3.1乒乓缓存技术的研究

本设计利用了乒乓缓存的面积与速度互换的原则实现了将一路的59 Mbyte/s的高速数据流分成了两路速度为29.5 Mbyte/s较低的数据流,这样就可以大大减轻了单片FLASH写入时序的压力。其实现原理如图3所示,输入的高速数据流通过输入数据选择单元将数据流等时分配到2个数据缓冲区,数据缓冲模块为FPGA内部的双口RAM(DPRAM),其容量大小设定为128 kbyte,正好是数据存储到FLASH中1块的容量。因此,这样就可以把数据以块为单位分别交叉存储到2片的FLASH中。在第1个缓冲周期,高速数据流向第1个缓存模块以59 Mbyte/s速度写入数据,当写到一半(即64K)时缓存模块1开始向FLASH1中以29.5 Mbyte/s的速度写入数据,当高速数据流写完缓存模块1时,FLASH已经写入了32 kbit数据。在第2个缓存周期,通过输入数据选择单元的切换,将输入的高速数据流缓存到数据缓冲模块2,当写完数据缓冲模块2时,FLASH1中已经写入了96 kbit的数据。在第3个缓冲周期通过输入数据选择单元的再次切换,将输入的数据流缓存到数据缓冲模块1,当高速数据流写入缓存模块1一半的容量(64 kbit)时,数据缓冲模块1中上一次写入的数据正好以29.5 Mbit/s的速度全部写入了FLASH1。此时,数据从数据缓冲模块1的起点开始再次写入FLASH1,并以此循环。这样就通过乒乓缓存操作,写入FLASH1所要求的数据处理速度仅仅为输入数据速度的1/2。同理,FLASH2的写入速度也仅仅要求为高速数据流速度的一半。

图3 乒乓缓存的实现原理图

3.2流水线交错式双平面编程技术的研究

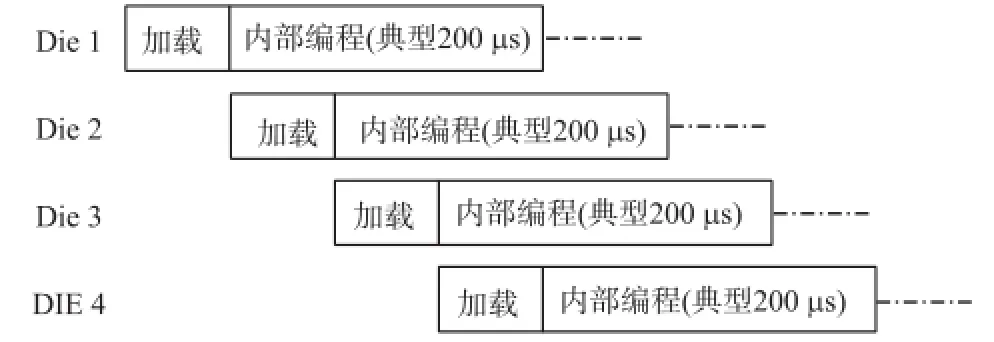

为实现单片FLASH写入的平均有效速率达到29.5 Mbyte/s,FLASH的存储方式起着至关重要的作用。本设计运用了交错式双平面编程,配合流水线操作,可以极大的的提高芯片的写入速度。芯片写入数据是以逻辑单元(die)为基础的,一片FLASH芯片有4个逻辑单元。写入数据的页编程操作可分为加载操作和自动编程操作,其中自动编程操作是FLASH芯片自动完成数据从页寄存器中写入内部存储单元的编程操作,等待时间的典型值为200 μs,在此期间,此逻辑单元不响应其他操作,因此自动编程时间成为约束写入速度的瓶颈。为了突破这一瓶颈,本设计采用流水线操作,充分利用200 μs的自动编程时间完成加载操作,实现了时间上的复用。如图4所示流水线操作示意图。

图4 流水线操作示意图

本设计将FLASH的写入时序配置为交错式双平面编程,所谓交错式双平面是指当写满同一逻辑单元中两页时,便一齐执行200 μs的页编程操作,同时开始进行另一逻辑单元的数据写入。MT29F16G08AJADAWP芯片中的4个逻辑单元中每个逻辑单元包含了2个平面,每个平面共有2 048块。其中,CE1中的block(2*n+0)、block(2*n+1)、block(2*n+4 096)、block(2*n+4 097)和CE2中的block(2*n+0)、block(2*n+1)、block(2*n+4 096)、block(2*n+4 097)表示MT29F16G08AJADAWP内部阵列每行的八个块,根据n值的不同,可以把对应的八个块命名为BLOCK n。对于单片FLASH,每次写入2 kbit数据的存储顺序为:从左到右依次写入BLOCK 0对应八个块中的page 0,当所有page 0都存满之后,再依次按顺序写入BLOCK 0对应所有page 1。直到写完BLOCK 0中所有的页,然后按照n递增的顺序依次跳入所有的BLOCK,最终实现了单片FLASH芯片MT29F16G08AJADAWP的4G存储。

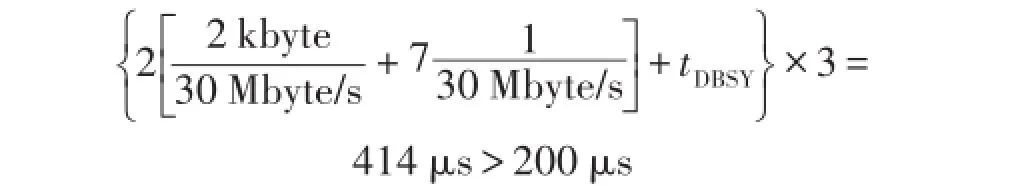

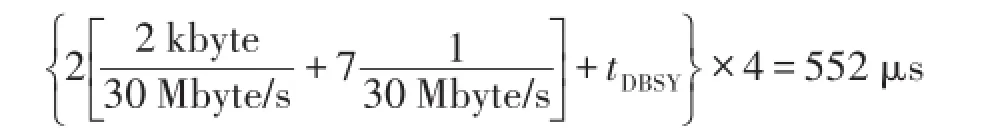

当第一个逻辑单元完成4K数据写入页寄存器后,进入200 μs的页编程时间,在此期间依次对第2、3、4个逻辑单元开始写页寄存器操作,后3组完成写页寄存器操作的时间为:

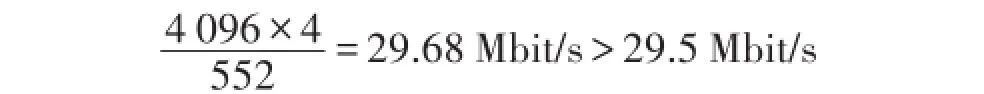

在此时间段内完成了4 096×4 byte的写入,故单片FLASH的平均写入速度为:

因此单片MT29F16G08AJADAWP可以达到29.68 Mbit/s的存储速度,大于要求的有效数据传输速度,达到了数据存储速率与传输速率的匹配,可以实现对数据流进行正确可靠的存储。

3.3无效块管理

无效块是FLASH中存在的不能正常操作的坏块,它在NAND FLASH芯片内的位置是随机分布的,在出厂时FLASH芯片自身的无效块信息都被标记在每个块第一页的空闲区首字节上,如果该地址的数据为00h则认为是无效块[8]。本设计要求在每次上电时先对FLASH内部所有的块按照块的顺序进行无效块检测,并将无效块信息按顺序存入FPGA内部RAM中,形成无效块缓存列表。FLASH按照无效块列表信息执行各种操作,即使在操作过程中出现新的无效块,无效块列表信息也能被及时地更新,进而保证了存储器的稳定工作。具体的管理方法如下:当chip#1中Block(2*n+0)、Block (2*n+1)、Block(2*n+4 096)、Block(2*n+4 097)和chip#2中Block(2*n+0)、Block(2*n+1)、Block(2*n+ 4 096)、Block(2*n+4 097)任何一块为无效块时,则认为这八块都是无效块直接跳过,并把chip#1中Block(2*n+0)的无效块地址按顺序依次写入FPGA中事先建立好的RAM列表中。每次对chip#1中 Block(2*n+0)的当前块进行读/写/擦除操作时,只需依次与RAM中保存的无效块地址信息进行对比即可,如果是无效块,只需n值加1,跳到chip#1中下一块;如果是有效块,则无需再对另外7块进行校验,可以直接对八块进行读取、写入操作。这样就节省了无效块校验时间,提高了数据存储和读取速度。

4 系统测试

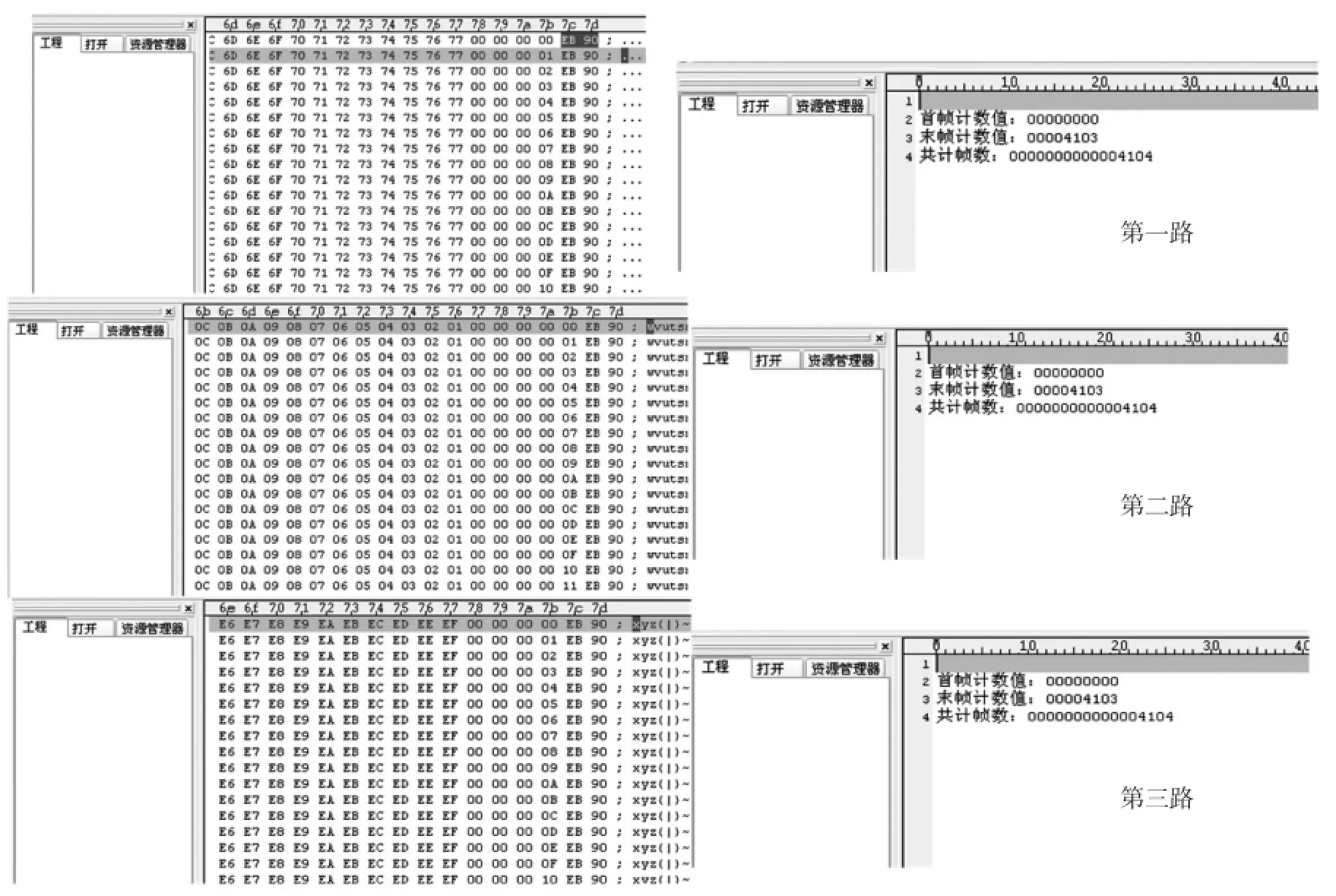

地面测试台发送3路数据供三个存储模块存储。记录器存储完毕之后,通过上位机回读存储的3路数据,根据上位机软件分析数据结构可知,回读数据与模拟信号源发出的数据格式一致,未出现丢帧、误码的现象,实现了对高速LVDS模拟信号的实时、可靠存储。由此可见,记录器的存储功能正常,性能指标满足技术要求。三路回读数据及测试结果如图5所示。

图5 上位机测试结果

5 结束语

本文基于新的逻辑思想和芯片设计了一种高速大容量雷达数据记录器,用最新型号的镁光FLASH芯片替换了已经停产的三星FLASH,使用了乒乓缓存的面积与速度互换原则大大减轻了单芯片操作时序的压力,单片FLASH使用了交错式双平面编程和高效的无效块管理,极大的提高了芯片的写入速度。此数据记录器已经通过了振动、高低温、电磁兼容和冲击等实验,运行可靠稳定,同时已经交付部队使用。

[1] 杨立宏.基于FLASH的红外相机高速存储[D].长春:长春理工大学,2008.

[2] 吴鹏.高速实时FLASH阵列数据采集系统研究与实现[D].南京:南京理工大学,2007.

[3] 吴萌,刘波,WU Meng.高速、大容量视频数据存储、传输系统设计[J].电子器件,2009,32(3):638-642.

[4] 舒文丽,吴云峰,孙长胜.基于NAND Flash的海量存储器的设计[J].电子器件,2012,35(1):107-110.

[5] 车艳霞,任勇峰,刘东海.一种小体积高速数据记录器的设计与实现[J].自动化与仪表,2011,26(11):9-11.

[6] 刘文豫,任宏.高速数字光电耦合器HCPL-260L/060L及其应用[J].国外电子元器件,2003(9):59-60.

[7] 康艳霞,曹剑中,田雁.实时视频处理系统中乒乓缓存的设计[J].弹箭与制导学报,2007,27(4):218-221.

[8] The Datasheet of MT29F16G08AJADAWP[R].

雷超群(1990-),男,汉族,山西平遥人,硕士研究生,主要研究方向为FPGA数字信号处理技术,1395456058@qq.com;

苏淑靖(1971-),女,汉族,山西吕梁人,副教授,硕士生导师,主要研究方向为感知与探测,信号处理,sushujing@nuc.edu.cn。

New High-Speed Large-Capacity Data Logger Designed Radar*

LEI Chaoqun1,2,SU Shujing1,2*

(1.Key Laboratory of Instrumentation Science&Dynamic Measurement,North University of China,Ministry of Education,Taiyuan 030051,China;2.Science and Technology on Electronic Test&Measurement Laboratory,North University of China,Taiyuan 030051,China)

Design of a new type of high speed large capacity radar data recorder.In order to effectively speed 59 Mbyte/s radar echo data flow timely and reliable storage to the recorder,logic system used the ping-pong cache technology to decompose the two-way speed 29.5 Mbyte/s data flow and cross write two pieces of FLASH,this greatly reduced the monolithic FLASH operation timing of pressure.And monolithic FLASH using staggered biplane type programming and efficient invalid block management greatly improves the writing speed of the chip.The data recorder has been through the vibration,high and low temperature,electromagnetic compatibility and impact experiments,stable and reliable operation,also has been delivered to the army.

high-speed storage;MT29F16G08AJADAWP;ping-pong buffer;staggered biplane programming

TN787

A

1005-9490(2016)03-0634-05

EEACC:632010.3969/j.issn.1005-9490.2016.03.026