基于FPGA高速视频图像实时采集与处理系统设计

田 杰,王广龙,乔中涛,高凤岐

(军械工程学院纳米技术与微系统实验室,石家庄050003)

基于FPGA高速视频图像实时采集与处理系统设计

田杰,王广龙*,乔中涛,高凤岐

(军械工程学院纳米技术与微系统实验室,石家庄050003)

针对高速视频图像实时采集与处理系统处理数据量大与系统实时性之间的矛盾,设计了一种基于高性能FPGA的高带宽处理系统。采用Cyclone IV GX系列芯片为核心处理器,4片DDR2构造64 bit总线。完成了高速系统硬件电路设计,系统主要由视频图像传感器、FPGA、DDR2、VGA控制器件等组成。实现了高速视频图像数据的实时采集、缓存、处理、显示等一系列过程。实验表明,利用此系统进行高速视频图像的实时采集、处理与显示时动态画面流畅、实时性好。

FPGA;实时性;视频图像处理;时序分析

随着经济的快速发展,各个领域对高速视频图像采集与处理的速度与精度提出了更高的要求,譬如:机器人导航领域、现场监控领域、安防领域等。在此背景下,高速视频图像实时采集与处理技术得到了长足的发展[1]。

20世纪70年代,人们开始利用高速摄像机来记录运动的物体,但当时高速摄像机是以胶片的形式作为记录介质,无法实现数据的实时处理[2]。现如今,在国外,高速工业相机的采样频率高达1 000 frame/s[3],而国内高速视频图像采集处理系统正处于发展中阶段,一般来说采样频率不超过100 frame/s。目前,对高速视频图像进行采集处理可以分成两类。第1类,基于软件的处理技术,这类处理方式是在PC机的平台上利用应用软件对高速视频图像进行处理,此类处理方式对系统的实时性要求低,处理结果更加理想;第2类,基于硬件的处理,利用FPGA、DSP对高速视频图像进行处理,实时性好,更多地应用于工业控制领域,但其图像处理结果不如前者理想[4]。由于高速视频图像实时采集与处理系统具有数据量大,数据相关性高,而且对图像的帧、场时间具有严格的限制,因此,高速视频图像实时采集与处理领域对中央处理芯片、外部存储芯片的工作速率以及核心算法的运算复杂度等都提出了极大的挑战。

本课题设计的系统应用于工控领域,国内一些公司开发的高速视频图像采集卡多是基于DSP芯片进行处理,但DSP的串行处理方式限制了处理速度[5],由于FPGA具有并行处理能力与流水线技术,因此,本文选用高性能FPGA进行实时采集与处理[6]。

收稿日期:2015-06-12修改日期:2015-09-12

1 系统总体设计

高速视频图像采用300 frame/s的速率进行采样,分辨率为640像素×480像素的标清像素,采用四路高速摄像头同步进行数据采集,则每秒采集的数据量达369 Mbyte,传输速率约为3 Gbit/s。因此,对主要芯片型号的选择提出以下两点要求:FPGA芯片应具有丰富的通用I/O接口以及逻辑单元;高速数据缓存模块应构造多位数据传输总线以实现数据的高速缓存。

鉴于此,选择Altera公司Cyclone IV GX系列芯片作为核心处理器,其可用I/O数达310,逻辑单元数为49 888;选择4片DDR2构造64 bit总线,每片DDR2的容量为1 Gbit。当FPGA与DDR2之间的时钟频率为200 MHz时,传输速率达12.8 Gbit/s,充分满足系统设计需求。

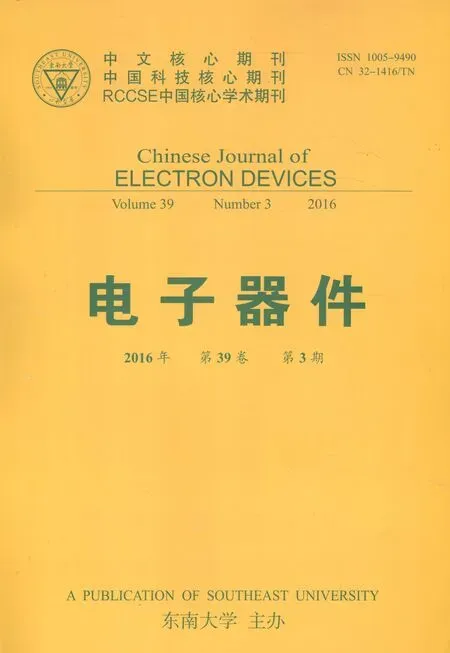

系统采用核心板+扩展板的方式构成。核心板主要包括FPGA+4片DDR2,承担起高速视频图像采集处理的核心算法。系统功能模块如图1所示,图中细线代表控制总线,粗线代表数据总线。

图1 系统框图

高速视频图像实时采集与处理系统工作原理为:首先采用4路高速CMOS摄像头作为输入,将得到的视频信号经视频解码芯片转换后再传输给FPGA,其中,FPGA通过IIC控制视频解码芯片;然后FPGA控制DDR2实现图像数据的高速缓存,当DDR2完成一帧图像的存储以后,FPGA读取DDR2中的数据并对其进行图像处理;并将得到的结果输出给VGA显示模块,并最终通过VGA接口进行显示。

2 高速视频图像系统硬件设计

2.1高速视频输入模块

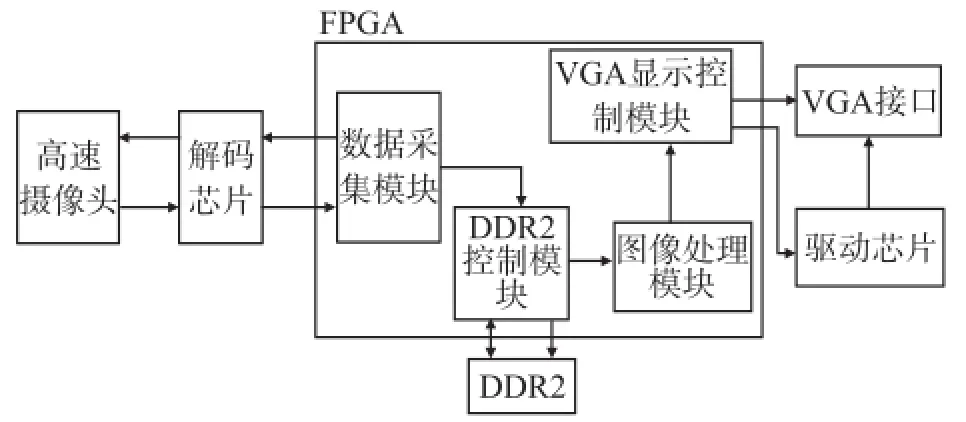

本设计利用4路高速CMOS摄像头采集到的视频图像信号作为输入,采用Techwell公司的TW2867作为视频解码芯片,其可输入4路复合视频信号,PAL/NTSC/SECAM自动识别,输出BT656,可多路复用总线,FPGA端解复用,实现多通道视频图像数据的同步输入。FPGA通过IIC总线与视频解码芯片进行通信,FPGA与视频解码芯片之间的连接关系如图2所示。

图2 FPGA与TW2867连接关系示意图

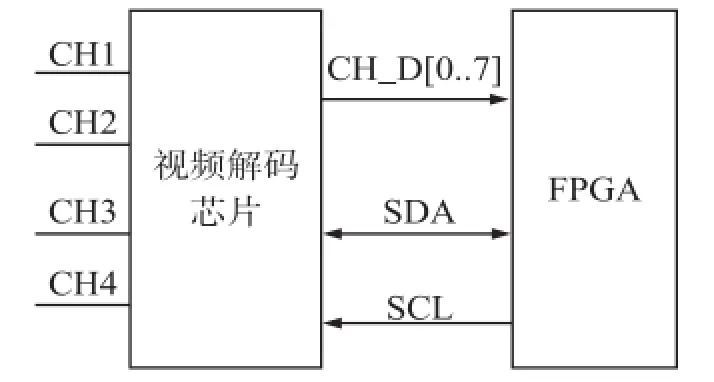

2.2高速缓存模块

高速缓存DDR2在整个高速视频图像实时采集与处理系统硬件电路设计过程中占有重要位置。其总线宽度、存储容量等参数对系统实时性产生极大的影响。本文采用4片DDR2构造64 bit总线,总容量为4 Gbit,FPGA与DDR2之间的时钟工作频率达200 MHz,DDR2内部时钟频率达400 MHz。图3所示为高速缓存模块(4片DDR2)与FPGA之间数据、地址、控制线之间连接关系示意图。

图3 FPGA与DDR2连接图

在DDR2原理图设计过程中,DDR2的时钟信号线必须连接到FPGA中的differential I/O上;命令线、地址线连接到FPGA的通用I/O上即可;数据线DQ、数据选通信号线DQS必须连接到FPGA的DQ/DQS引脚上。

在PCB布线过程中,为保证系统运行过程中时序的正确性,要保证高速缓存模块数据线等长布线。

2.3电源模块

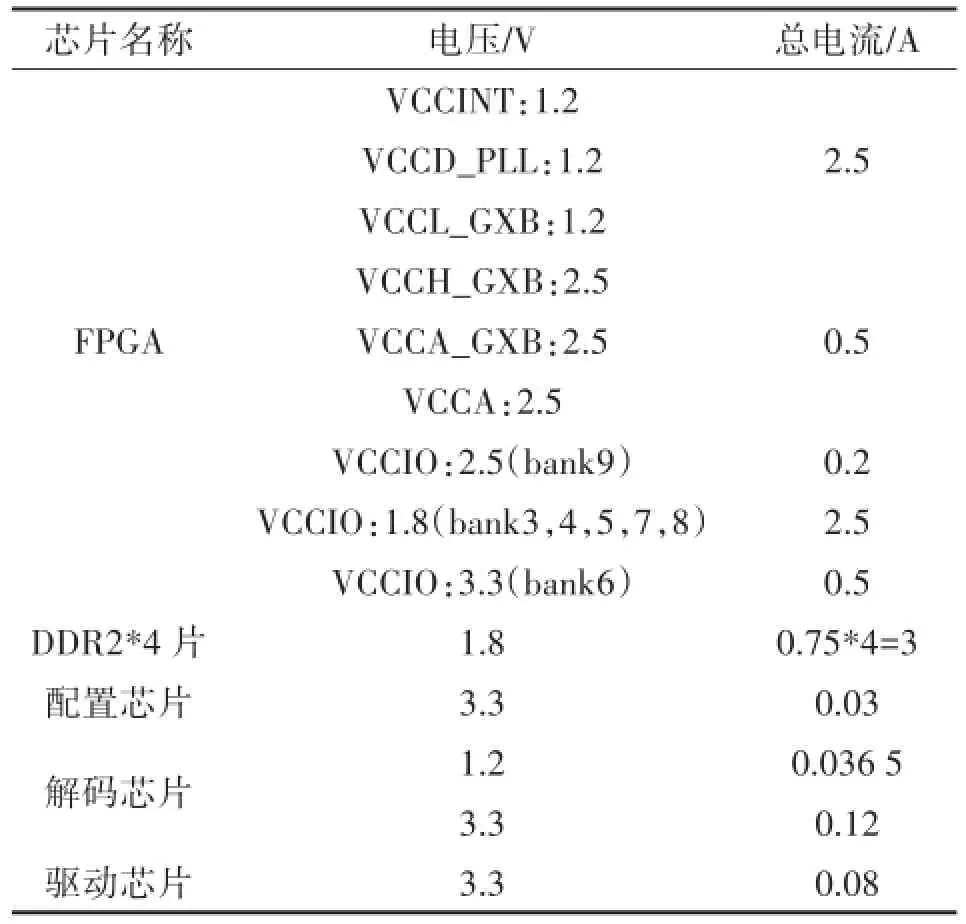

系统电源模块作为整个系统正常工作的动力,其在电子系统设计过程中至关重要。在进行电源模块设计之前,先对系统进行功耗分析,各主要芯片所需电压、电流大小如表1所示。

表1 系统功耗分析

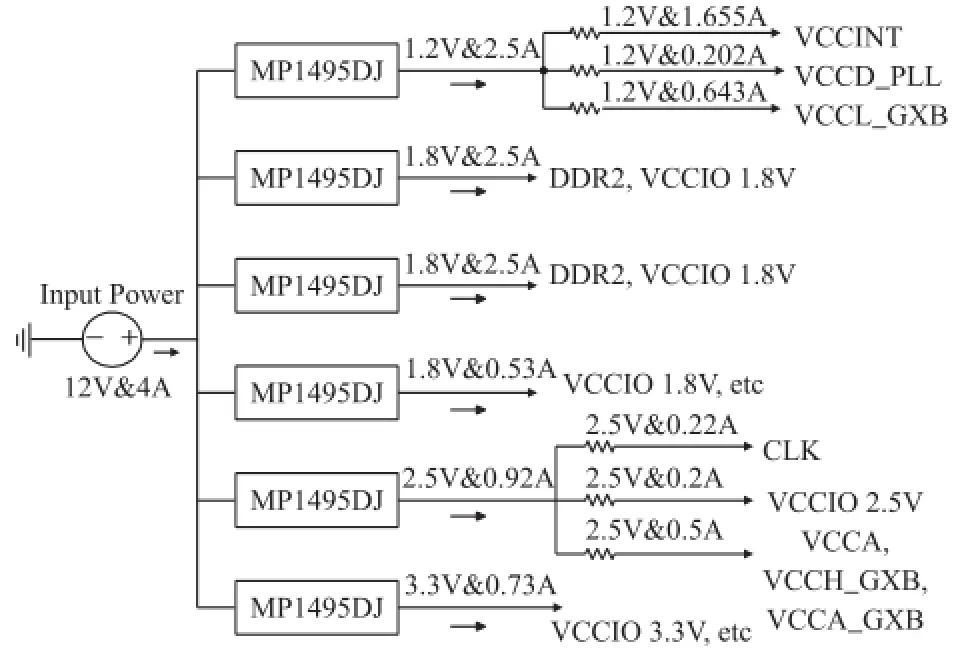

由表1中各芯片所需电压、电流大小进行电源树设计,系统选用专用电源芯片MP1495DJ,其支持4.5 V~16 V电压输入,为简化设计,本系统全部采用12 V电压输入,输出电压由MP1495DJ中8脚的相关电阻R1、R2、RT决定,其中,R1、R2、RT所处位置以及大小可依据MP1495DJ数据手册中给出的参考值进行选择,这里不做赘述。系统电源树设计如图4所示。

图4 电源树设计

2.4电源完整性及信号完整性设计

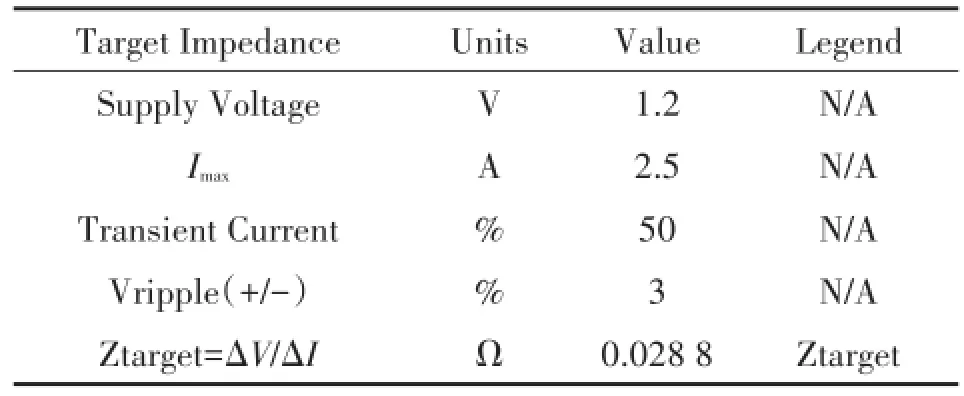

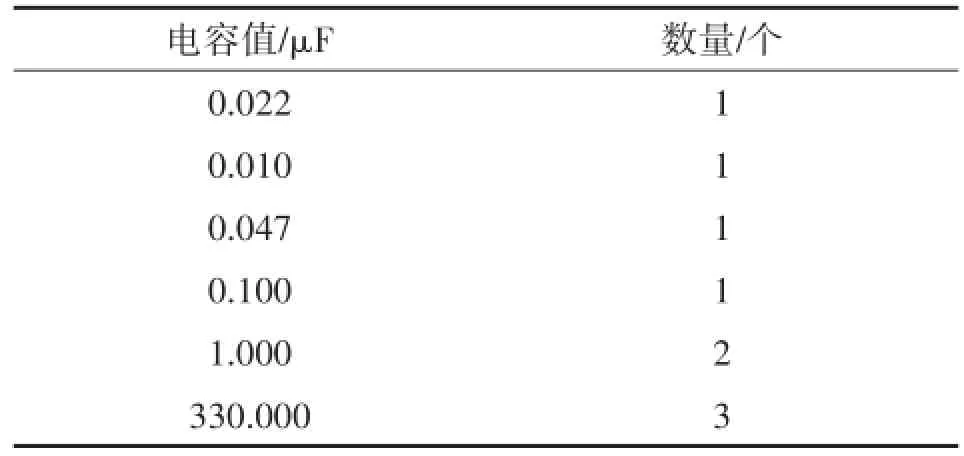

电源完整性设计目的是在保证流经系统的电流足够大的前提下尽可能降低电源的纹波。需要解决的核心问题是得到足够低的电源目标阻抗。解决方案是合理地选择和放置去耦电容,条件允许情况下可以选择添加单独的电源层、地层。利用PDN工具计算VCCINT的电源目标阻抗,结果如表2所示。

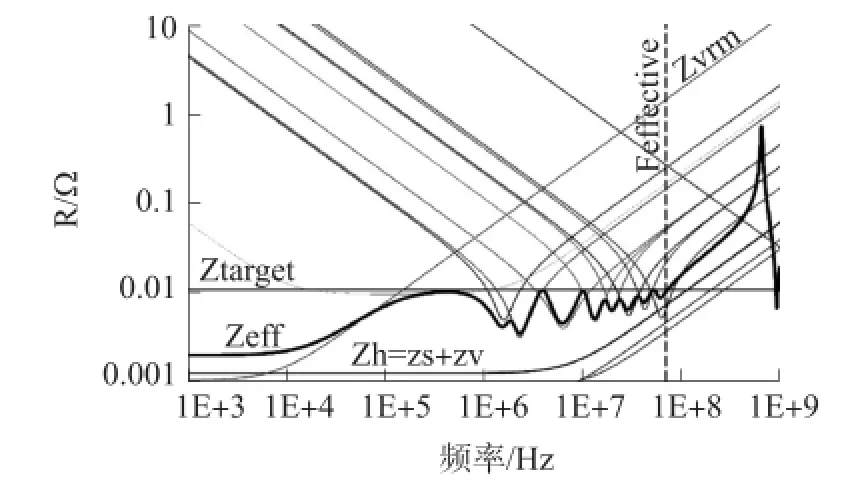

通过添加不同数量、不同大小的去耦电容,以保证VCCINT电源实际阻抗Zeff在Feffctive范围内始终小于电源目标阻抗Ztarget,图5所示为Zeff与频率之间的关系(通过添加去耦电容得到)。表3列出来此时需要添加的去耦电容的大小以及数量。

表2 目标阻抗计算

图5 电源阻抗与频率关系图

表3 去耦电容大小及数量

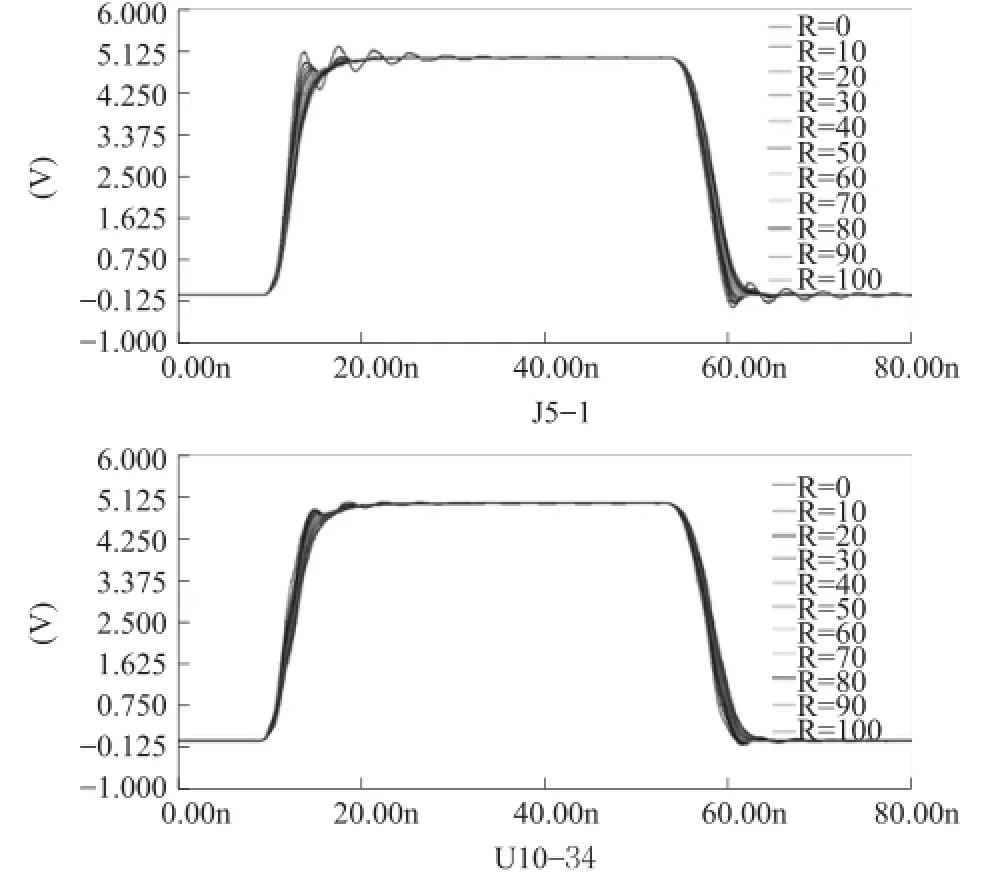

多数信号完整性[7]问题是由于反射问题引起的[8],通过引入合适的终端组件进行阻抗匹配可以将反射影响控制在可接受范围内[9,10],如图6所示。

图6 不同终端阻值时反射分析图

布线结束后,对PCB板进行信号完整性分析,图6所示为某一网络(信号完整性分析结果当中状态显示为failed)反射分析图,通过在其端口增加大小不同的电阻,阻值变换范围由0 Ω~150 Ω,图中上、下部分分别是此网络的连接端口。从中发现,当引入终端阻抗大小为80 Ω时,系统信号完整性检测效果最好。

3 高速视频图像系统软件设计

3.1高速视频图像采集模块

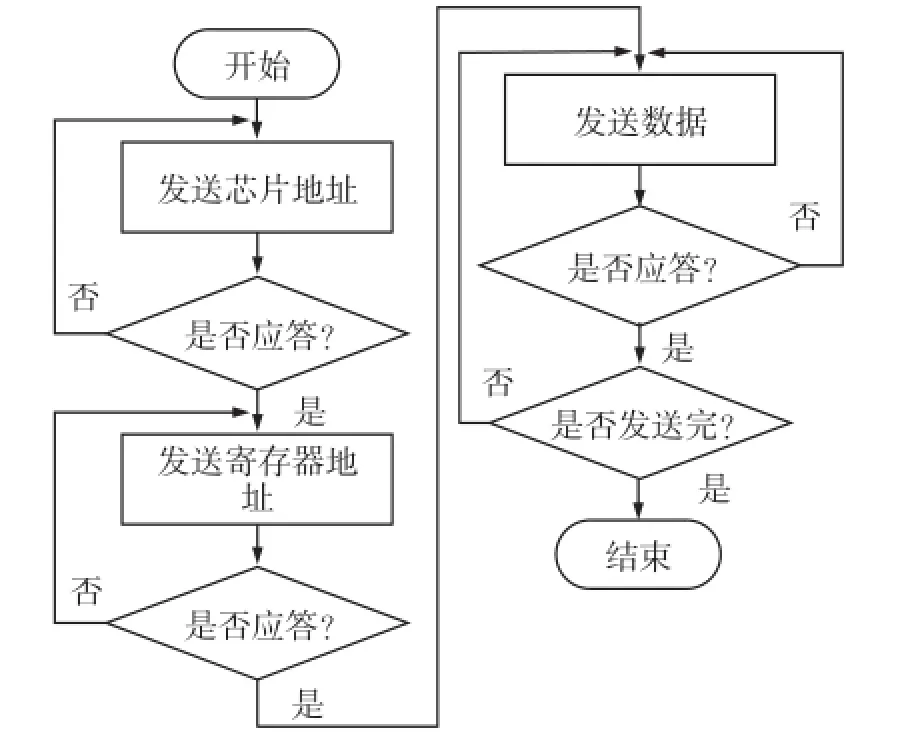

四路图像传感器将得到的模拟视频数据信号通过视频解码芯片传输给FPGA,其中,FPGA通过IIC总线配置视频解码芯片的寄存器。利用FPGA的两个引脚模拟IIC总线时序。图7所示为视频解码芯片内部寄存器配置流程图。

图7 配置视频解码芯片流程图

3.2高速视频图像实时处理模块

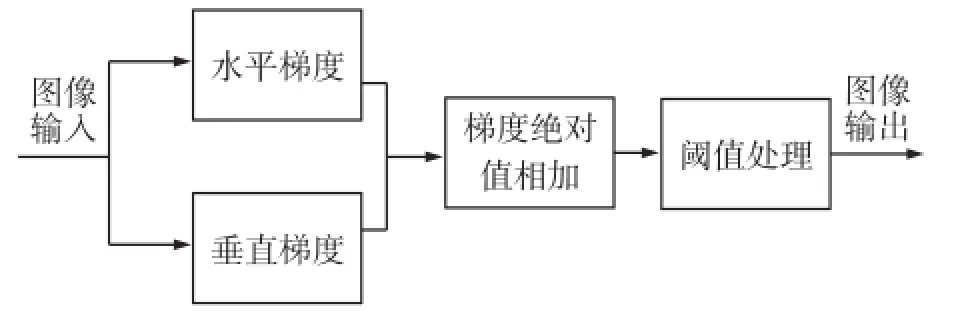

本文以基于Sobel的边缘检测算法为例,采用两个3×3卷积核形成边缘检测算子,分别将之与图像做平面卷积得到横向与纵向检测的梯度,最后将图像两个方向的梯度绝对值相加并进行阈值判断,判断像素是否为边缘点。算法实现框图如图8所示。

图8 Sobel算法实现框图

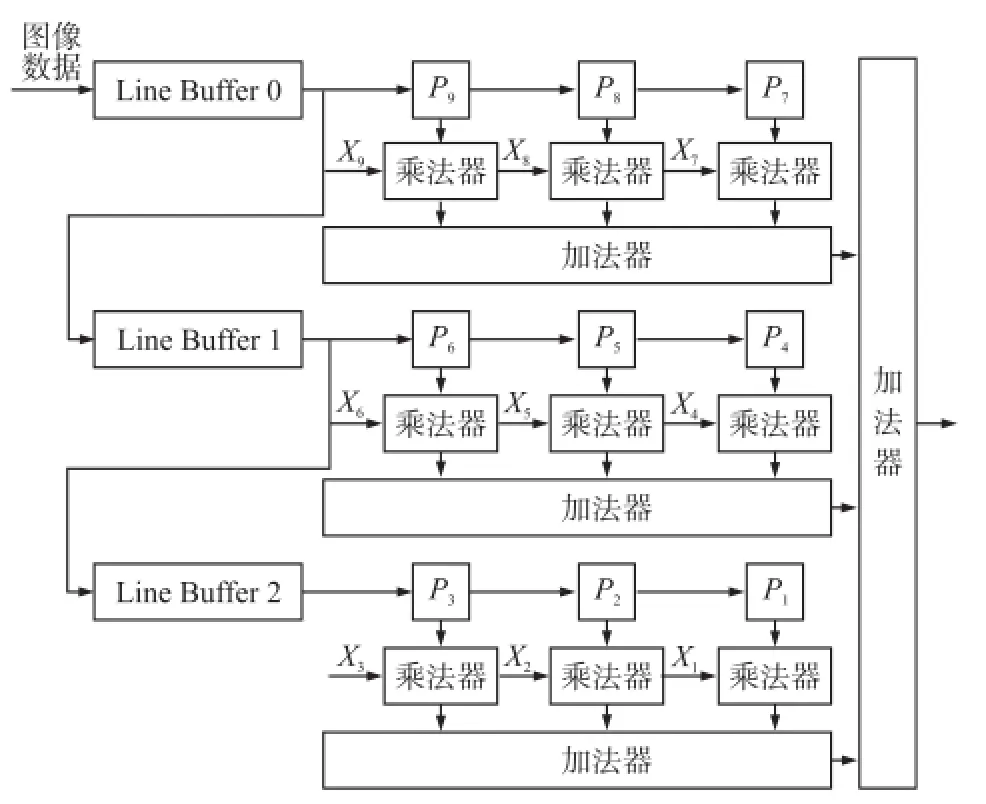

由于FPGA具有并行处理能力与流水线技术,便于实现高速视频图像的的实时处理。以计算水平梯度Gx为例,通过构建Line Buffer的方式计算图像中像素点P5的Gx。梯度Gx实现结构图如图9所示。

图9 梯度Gx实现结构图

图中,P1,P2,…,P9为依次由图像传入的像素点,X1,X2,…,X9为Sobel算子的参数。Line Buffer通过使用 Megafunction中的 altshift_tab实现,其中,tap的个数以及每个tap输出的缓存长度都设置为3。加法器及乘法器亦可以通过Megafunction构造。

3.3系统显示模块

高速视频图像实时采集与处理系统利用FPGA进行处理,并将处理结果通过VGA接口显示。利用FPGA的两个引脚模拟HSYNC与VSYNC控制信号。本文采用的显示模式为640像素×480像素× 60 Hz,其时钟与行扫描信号、场扫描信号之间的关系如图10所示。

图10 VGA接口时序图

其中,场计数器驱动时钟应为行计数器的溢出信号,当行计数器为800时,场计数器加1,场计数器的周期为525。当行计数器与场计数器同时计数到有效显示区域时,图像正确显示。

利用Verilog语言可以方便构造出VGA正常工作所需要的时序信号,保证系统正常显示。

4 系统功能验证

基于FPGA的高速视频图像实时采集与处理系统硬件设计完成后,首先实现四路摄像头的实时显示,显示结果见图11所示。实验过程中,目标实时显示,无时滞发生。

图11 四路摄像头实时显示结果

然后对其中一路摄像头采集到的图像信息进行边缘提取并通过VGA接口显示。图12为通过VGA接口传出的边缘提取后图像。通过系统的显示设备可以检测到系统每帧图像的处理时间为16.7 ms,实时性好,动态画面流畅,且同时边缘提取图像能够清晰显示,符合系统设计需求。

图12 边缘提取图

5 结束语

高速视频图像实时采集与处理系统被广泛应用于安防、智能车、监控等各领域。本文利用高性能FPGA、四片DDR2等器件进行硬件电路设计,充分满足高速视频图像实时采集与处理过程中对系统实时性的需求,并在此基础上实现了目标的边缘检测。实验表明,系统动态画面流畅,实时性好。

[1] Yahia Said,Taoufik Saidani,Fethi Smach,et al.Embedded Real-Time Video Processing System on FPGA[J].Lecture Notes in Computer Science,2012,7340:93-102.

[2] 张祥.高帧率视频图像获取与实时处理系统硬件设计[D].西南交通大学,2014.

[3] Brekke B,Nilsen L C L,Lund J,et al.Ultra-High Frame Rate Tissue Doppler Imaging[J].Ultrasound in Medicine&Biology,2014,40(1):222-231.

[4] 叶敏,周文晖,顾伟康.基于FPGA的实时图像滤波及边缘检测方法[J].传感技术学报,2007,20(3):623-627.

[5] 冯辉宗,陈叶,徐洋.基于FPGA的实时图像采集与Sobel边缘检测[J].传感器与微系统,2011(6):116-118.

[6] 冯伟昌,林玉池,何冬.基于FPGA的双通道实时图像处理系统[J].传感技术学报,2010,23(8):1118-1122.

[7] 白同云.高速PCB电源完整性研究[J].中国电子科学研究院学报,2006,1(1):22-30.

[8] T W,H C,T W.Overview of Power Integrity Solutions on Package and PCB:Decoupling and EBG Isolation[J].IEEE Transactions on Electromagnetic Compatibility,2010,52(2):134-140.

[9] 闫静纯,李涛,苏浩航.高速高密度PCB电源完整性分析[J].电子器件,2012,35(3):296-299

[10]任勇峰,张凯华,程海亮.基于FPGA的高速数据采集存储系统设计[J].电子器件,2015,38(1):135-139.

田杰(1990-),女,汉族,黑龙江哈尔滨人,在读硕士研究生,主要研究领域为视频图像处理与微系统,ysdmhj@ 163.com;

王广龙(1964-),男,教授,博士生导师,主要从事微传感器与微纳米系统研究。

Design of a High-Speed Real-Time Video Acquisition and Processing System Based on FPGA

TIAN Jie,WANG Guanglong*,QIAO Zhongtao,GAO Fengqi

(Laboratory of Nanotechnology and Microsystems,Ordnance Engineering College,Shijiazhuang 050003,China)

A high-bandwidth system based on high-performance FPGA is designed to deal with the contradiction between the high-volume data with real-time performance in video processing system.The system consists of the chips of Cyclone IV GX and four pieces of DDR2 which make up 64-bit bus.The circuit has been completed and the system is made up of image sensors,FPGA,DDR2,VGA controller and so on.The system realizes the real-time data acquisition,data-caching,processing and display.The experiment shows that high-speed real-time video acquisition and processing system can be achieved and the system has the characteristics of excellent real-time performance.

FPGA;real-time performance;video processing;time series analysis

TP391

A

1005-9490(2016)03-0623-05

EEACC:7220;0230H10.3969/j.issn.1005-9490.2016.03.024