采用SSI协议实现的绝对值编码器

王 青,俞建定,袁 飞,周彬彬

(宁波大学 信息科学与工程学院, 浙江 宁波 315211)

采用SSI协议实现的绝对值编码器

王青,俞建定,袁飞,周彬彬

(宁波大学 信息科学与工程学院, 浙江 宁波 315211)

摘要:近年来,随着科技和工业的快速发展,绝对值编码器在其通信技术方面也在逐步地优化与完善,其中SSI协议的输出方式在绝对值编码器领域中应用比较广泛。详细阐述了SSI协议的通信方式,设计出硬件电路,并采用Verilog语言实现了SSI通信协议。通过测试实验,证明了该应用系统抗干扰性强、性能可靠、通信速度快,具有潜在的市场价值。

关键词:绝对值编码器;SSI协议;Verilog

引用格式:王青,俞建定,袁飞,等. 采用SSI协议实现的绝对值编码器[J].微型机与应用,2016,35(13):4-5,9.

0引言

近年来,编码器应用比较多,主要应用于工业控制系统,比如电机的转速测量、机床位置的测量、起重机上升距离的测量等,同时编码器在市场上的规模越来越大,工业的需要量也逐步增长。在未来的几十年里,编码器行业将会达到高速发展的阶段,将会有更多的编码器生产厂商参与这场革命的竞争。

编码器是将数据转换成信号形式的一种设备,这种信号可以用来通讯、传输和存储[1]。编码器的原理是把这些物理位移变换成熟知的电信号。按工作性质划分,编码器可以划分成两大类:增量型编码器和绝对值编码器[2]。增量型编码器主要应用在那些精度要求不高的仪器上。而针对那些精度要求比较高的行业,一般都是重工业,比如设备制造业、电子工业等,通常会采用绝对值编码器。因为绝对值编码器具有启动速度快、数字编码、位置唯一等特点,所以它已经被广泛地应用在各种工业系统中[3]。随着仪器仪表越来越智能化,人们对编码器提出功耗低、质量好、体积小的要求,希望在绝对值编码器的领域中有更多类型的输出方式,让越来越多的装置能够实现自动化。

早期的绝对值编码器的输出大多采用并行输出方式,然而随着科技的进步,绝对值编码器的输出方式也越来越丰富,出现了比如RS-485、PROFIBUS-DP、CAN、DeviceNet 等现场总线输出方式、模拟信号转换输出方式以及SSI协议同步串行输出方式等[4]。这几种输出方式都有各自的优点和缺点。并行输出适用于短距离传输,其价格比较低廉;现场总线型输出一般适用于超大规模的工业领域中,但是价格比较昂贵;而模拟信号转换输出方式目前应用相对比较少。这几种输出方式比较而言,SSI 串行输出方式的优点比较多,比如抗干扰能力强、接线少,因此市场上应用比较广泛。

1工作原理描述

1.1增量型编码器工作原理

增量型编码器的工作原理是先将位移变成具有周期性的电信号,然后把这个信号转换成计数脉冲,通过这样的转变,位移就可以通过脉冲输出的多少来测量[5]。如图1所示,当A相超前B相时,表示正转,反之则反转。增量型编码器主要依靠计数来记忆其位置,但是在突然断电时,如果编码器稍微移动,那么再来电时,记忆的零点就会偏移,造成不精确和记忆损失。需要增加参考点,也就是Z相,用参考位置来处理这些问题。但是此类型编码器每次操作都要先找参考点,抗干扰能力比较差,零点累计时也有误差。如果选用绝对值编码器这些问题都可以得到解决。

图1 增量型编码器工作原理

1.2绝对值编码器工作原理

绝对值编码器的码盘上有很多道光通刻线,它们依次以2线、4线、8线、16线……这样的方式进行排列[6]。这些刻线都有两面,分别为阴面和阳面,通过读取每道刻线的通、暗得到一组从20~2n-1的唯一的二进制编码(格雷码),这就是n位绝对值编码器[7]。每一个位置对应一个具体的数字,这个数字是绝对唯一的,只与起始和终止有关,与中间任何过程都没有关系。当遇到突然断电,重新启动时不用重新再找参考点和零点,也不用像增量型编码器那样重新记录脉冲的数目。任何时候想要知道它的具体位置,都可以去读取它。这种编码器的数据可靠、不容易受外界影响。

1.3SSI协议介绍

绝对值编码器主要是把需要测量的位置信息传输给主控制系统,然后通过主控制系统来发出控制信号[8]。以前的绝对值编码器大多采用并行输出,在位数不多的情况下可以适用,一旦位数越来越多,则并行输出就不适用了,因为总是出现数据不准确、错误等。比如在传输过程中,只要有一根数据线出现问题,就会影响到最终传输的数据,从而影响到绝对值编码器的正常工作。所以根据实际情况,SSI协议的输出方式比较适合。它用串行输出来替代并行输出,通过采用差分的方式来提高数据在传输过程中的可靠性,抗干扰明显增强,同时为了通信双方能够准确地发送和接收数据,故采用同一个波特率。

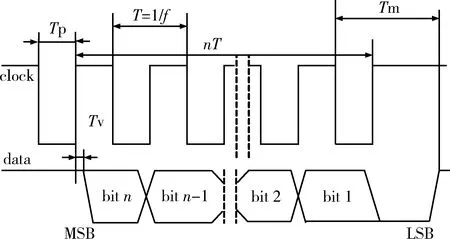

图2 SSI通信协议

SSI协议的通信方式如图2所示。其采用主动读取和接收的方式,包括同步时钟信号CLOCK、数据信号DATA,其中同步时钟的频率决定了数据在传输过程中的速率。在工业控制应用领域中,通过实际传输距离的远近来选择需要的频率。在同步时钟信号的控制下,从最高位(MSB)开始传送[9]。当遇到时钟信号的第一个下降沿时,在Tp这段时间内,把需要发送的数据进行保存,之后遇到时钟信号的每一个上升沿时就开始发送数据,直到所有的数据发送完即结束。然后把数据输出这一端拉至低电平,延长Tm时间之后再把数据输出端拉至高电平,准备等待下一个时钟信号的到来,继续发送数据。在不发送数据时,时钟信号和数据端都应该保持高电平。其中需要发送数据的位数决定了发送同步时钟的个数。图2中参数定义如下:T为时钟频率,Tp为数据之间传输间隔,Tm为单稳触发时间,n为传输位数,MSB为最高有效位,LSB为最低有效位。

2系统方案设计

主控制器可以选择51单片机、RAM微处理器和CPLD逻辑器件。单片机结构简单,价格便宜,但是运行速度很慢,处理速度有限,抗干扰能力也不是很强;RAM微处理器功能强大,但是开发周期长,价格昂贵。要想高速传输,采用CPLD设计比较灵活,其处理速度比较快,抗干扰能力也很强,并且设计时用到大量的时序和逻辑运算。

2.1硬件设计

SSI电路的输入和输出都采用差分方式,如图3所示,有4根信号线: CLK+、CLK-、DATA+、DATA-,其中CLK+和CLK-为时钟输入端,DATA+和DATA-为数据输出端。时钟输入端的接收采用光耦,数据端的输出采用422输出芯片。

图3 SSI电路设计框图

2.2软件设计

对于软件部分的设计,有两种方法可以实现SSI协议,一种方法是用单片机模拟SSI通信,另外一种是用CPLD来实现SSI通信。用单片机模拟的关键技术主要包括两个方面:同步时钟信号的准确获取和数据起始位的准确判断[10]。很明显,这需要输入端口和输出端口,另外还需要一个定时器来实现单稳态触发器。在输入端口捕获时钟的上升脉冲,遇到时钟的第一个下降脉冲时定时器开始工作。数据传输结束时定时器需要复位重新开始计数。软件流程图如图4所示。

用单片机来模拟SSI通信,结构比较简单,但是通信速度会受到约束。所以要想实现高速通信必须采用CPLD。CPLD的软件部分设计可以分为两个部分,一部分是单稳态触发器,在外加脉冲的作用下,可以从一个稳定状态翻转到一个暂稳态。它的输入为同步时钟上升沿,在一段时间内如果没有遇到上升脉冲,则将输出信号复位。另一部分是一个并入串出的移位寄存器,在单稳态触发器

图4 程序流程图

输出复位信号后,将需要发送的数据存入寄存器,继续等待下一个周期的移位时钟。并串转换的寄存器用Verilog语言描述如下:

Always@ (posedge clock or posedge load)

Begin

If(load==1.b1)

Out<=indata[24: 0];

Else

Out[24: 0]<=Out{[23: 1], 1.b0}

End

3结论

本文分别从硬件和软件两个方面进行研究和设计,实现了绝对值编码器的SSI通信协议,设计出的SSI通信板,成功与西门子S7-300系列PLC配置的SM338模块进行通信,PLC能够正确读出码值。根据市场分析,在工业控制领域中,具有SSI协议的绝对值编码器实用性比较强,应用比较多,因此本文的研究具有潜在的市场价值。

参考文献

[1] 张丽娟.关于电气传动设备手动控制增加自动模式方法[J].阴山学刊(自然科学版),2013,27(1):81-83.

[2] 王仲亮,杨广,薛秀生,等.基于RS485总线的多编码器数据采集系统研制及改进验证[J].测控技术,2014,33(11):144-145,149.

[3] 韦凤. 浅谈光电编码器的应用[J].科技风,2014(6):97.

[4] 陈志同. 基于SSI协议的绝对值编码器通信接口研究[D].天津:天津理工大学,2014.

[5]肖博,李剑锋,陈洪芳,等.多通道绝对式光电编码器数据采集系统[J].仪表技术与传感器,2013(1):27-29.

[6] 彭雨. 基于FPGA的绝对式光电编码器通信接口研究[D].武汉:华中科技大学,2008.

[7] 王文. 基于平台罗经的稳定平台控制系统研究[D].成都:电子科技大学,2009.

[8] 胡东轩. 永磁交流伺服系统多种位置检测与集成方法研究[D].杭州:浙江理工大学,2014.

[9] 靳红涛,赵勇进,陈朝基,等. 一种SSI接口光电编码器数据并行采集设计方法[J].电子技术,2008,45(5):23-25.

[10] 聂旭中. 编码器用SSI协议及实现[J].洛阳师范学院学报,2010,29(2):73-75.

中图分类号:TM33

文献标识码:A

DOI:10.19358/j.issn.1674- 7720.2016.13.002

(收稿日期:2016-03-01)

作者简介:

王青(1990-),女,在读硕士研究生,主要研究方向:嵌入式系统与应用。

俞建定(1968-),男,高级实验师, 主要研究方向:嵌入式系统与应用。

袁飞(1992-),男,在读硕士研究生,主要研究方向:嵌入式系统与应用。

The implementation of absolute encoders using SSI protocol

Wang Qing,Yu Jianding,Yuan Fei,Zhou Binbin

(Institute of Information Science and Engineering, Ningbo University, Ningbo 315211, China)

Abstract:In recent years, with the rapid development of science and industry technology, absolute encoder in its communication technology is also in the gradual optimization and improvement, in which the output mode of the SSI protocol is widely used in the field of absolute encoder. This paper describes communication ways of the SSI protocol in detail, designs a practical circuit, using verilog language to achieve the SSI communication protocol. The test results show that the proposed system has strong anti-interference, reliable performance and fast communication, and has potential market value.

Key words:absolute encoder; SSI protocol; Verilog