一种基于GTP的光纤高清视频传输系统设计

闵应涛,唐清善,李亚捷,钟海丽,曾鹏飞,罗 振,陈 凯,黎 欢

(长沙理工大学 物理与电子科学学院,湖南 长沙 410004)

一种基于GTP的光纤高清视频传输系统设计

闵应涛,唐清善,李亚捷,钟海丽,曾鹏飞,罗振,陈凯,黎欢

(长沙理工大学 物理与电子科学学院,湖南 长沙 410004)

摘要为满足视频传输系统对远距离、高清画质、无失真、抗干扰性和稳定性的需求,提出了一种基于GTP的高速串行传输以取代以往的并行传输模式,实现高清视频的无压缩远距离传输。FPGA采集数字视频数据后识别视频格式并经过SDRAM缓存,在GTP中转换为高速串行数据后通过单模光纤传输。GTP在2.5 Gbit·s-1的速率下传输,接收端对视频数据进行解码、缓存、显示。经过仿真、调试、验证,系统能稳定传输720p、1 080p等8种主流分辨率的视频,且可实时切换。

关键词GTP;高清视频;光纤传输;实时切换分辨率

随着高清视频的普及,远距离传输带宽高、数据量大的高清视频信号成为趋势[1],人们越来越需要通过高清画面获得更丰富的细节信息,而传统的传输方式一般将视频压缩后传输,传输速率通常为1.485Gbit·s-1,以适应较低的带宽,虽然能够完成传输但影响画面细节甚至失真,特别是犯罪监控、危险场所等无法捕获关键的细节信息。国内市场视频传输系统多采用标准串行接口,支持NTSC、PAL、SECAM制式视频格式输入,采集的视频信号多为CVBS视频信号或者直接从前端CMOS、CCD摄像头获取的原始视频信号[2],而采集DVI接口的高清视频,以2.5Gbit/s-1的速率直接传输无压缩视频,能够传输多种分辨率并能自适应调整分辨率的产品较少。另外,多数产品将视频的数据、行场信号、像素时钟封装成帧同步传输,即使行场消隐期间的无效数据仍然被传输,不仅浪费带宽,且由于像素时钟的传输需要外加波分复用器,增加了成本[3]。为解决上述问题,本文研究了一种能够远距离传输无压缩高清视频的光纤传输系统,具有一定的应用价值。

1系统设计方案及工作流程

1.1系统设计方案

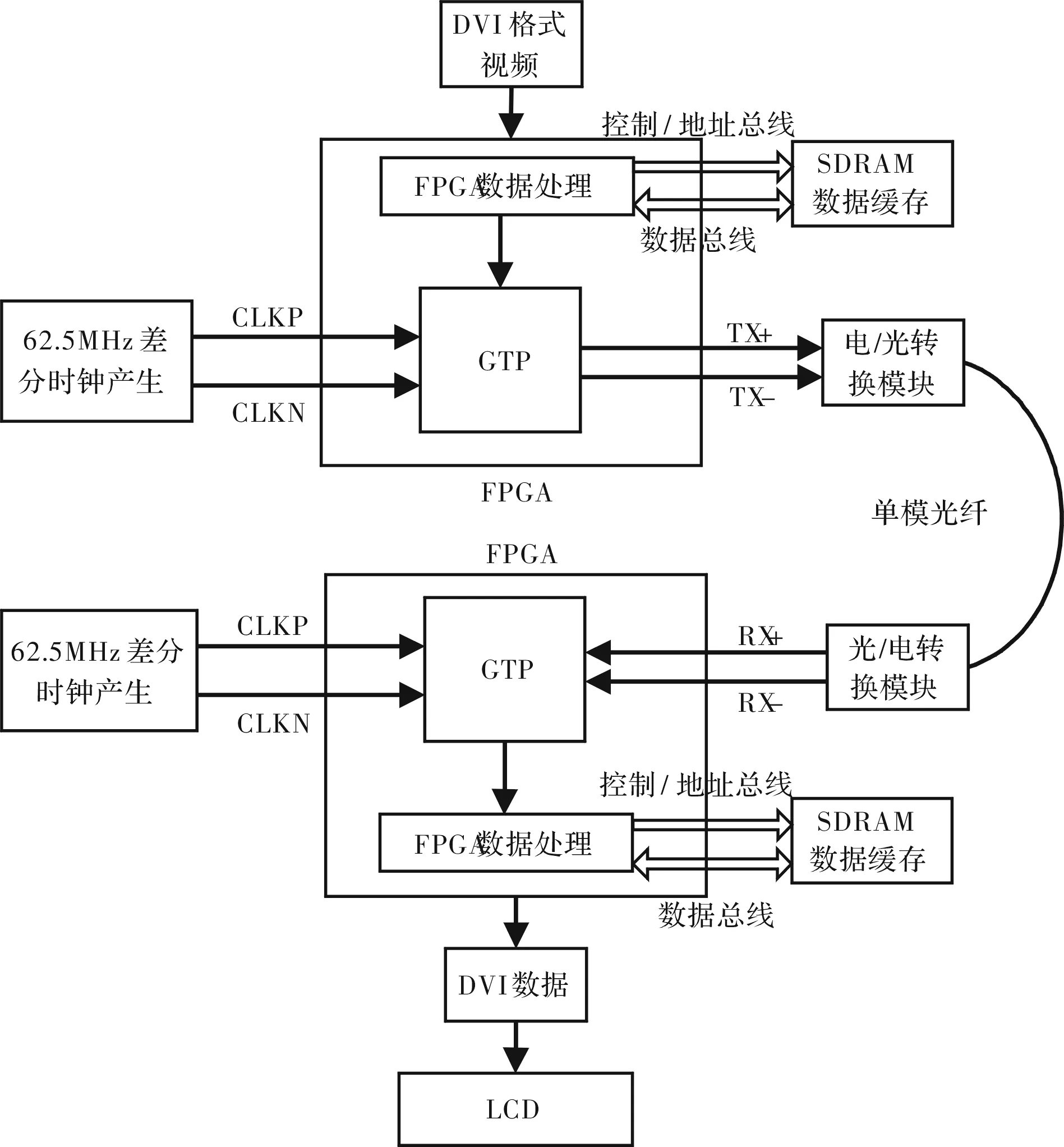

系统是在FPGA具有足够的带宽和数据处理能力的基础上工作的,FPGA通过视频采集芯片获得图像数据后进行处理,并控制一片SDRAM进行缓存,最后通过GTP发送出去,接收端将通过单模光纤收到的视频数据进行处理、SDRAM缓存并通过TFP410显示到LCD上,系统设计方案框图如图1所示。

图1 系统设计方案框图

1.2系统工作流程

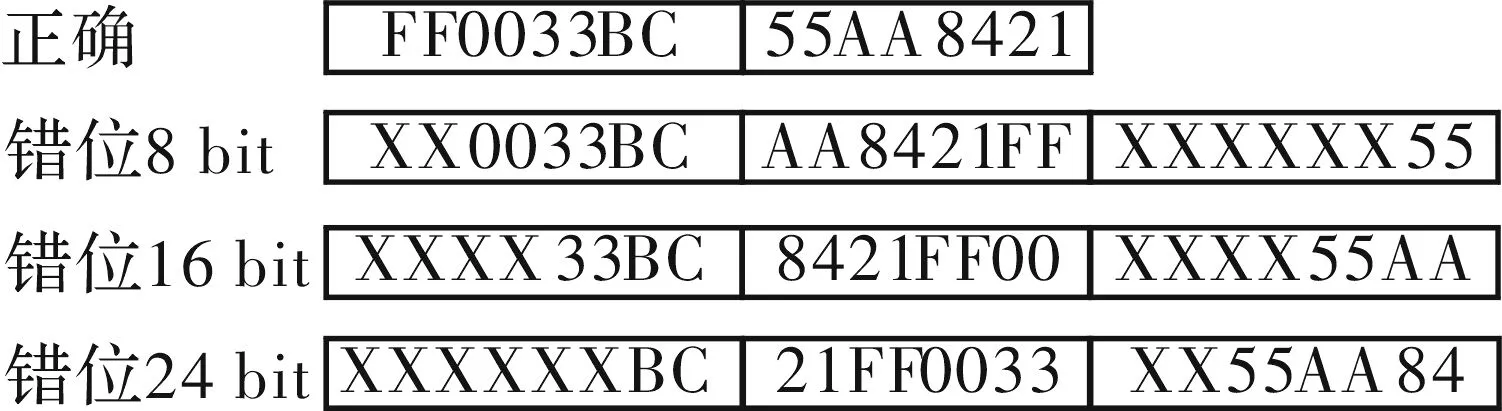

高清视频数据经过FPGA内部逻辑采集编码后,在一片SDRAM中进行缓存,通过两个容量为8k×32bit的FIFO进行数据跨时钟域处理,最后通过GTP和单模光纤将FPGA中的视频数据发送出去,接收端GTP收到数据后进行逆向处理,最终在LCD上显示出视频图像。不同模块所处时钟域如图2所示。

图2 各模块所处时钟域

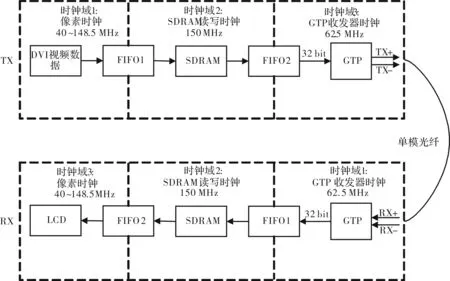

(1)系统上电后完成一系列初始化工作,ARM通过I2C配置差分晶振芯片SI570,使其输出62.5MHz的LVDS电平格式差分时钟,提供给FPGA中GTP使用;(2)FPGA中的视频数据采集模块在像素时钟频率下采集视频数据并写入FIFO1中,只采集有效视频数据,行同步和场同步时的数据均舍弃;(3)视频格式编码模块根据不同的分辨率对应产生一个8位的视频格式编码,并插入到4个32bit的场同步码中,在场同步时向FIFO1写入;(4)SDRAM控制器轮流进行读写操作,将FIFO1中数据读出写入到SDRAM,并将SDRAM中数据读出写入到FIFO2,在读FIFO1和写FIFO2时,都需要对场同步码进行解码操作,解出场同步码后产生一个SDRAM读写行地址清零信号;(5)数据读出FIFO2后送入到GTP模块,GTP在每32个数据中插入两个同步码,然后将并行数据转换为高速串行数据,并通过SFP光模块转换为光信息后通过单模光纤发送出去;(6)接收端GTP收到数据后转换为并行数据,并通过同步码对错位的数据进行纠正,然后将去掉同步码后的数据写入到FIFO中,同步码错位方式如图3所示;(7)与发送端一样,接收端同样在一片SDRAM中进行数据缓存,通过两个容量为8k×32bit的FIFO进行数据的跨时钟域处理[4];(8)接收端对场同步码解码后得到视频格式编码,以此为依据产生对应的行场格式和像素时钟,并最终将视频数据显示到LCD上。

图3 GTP同步码错位

2系统关键部分设计及调试

FPGA内部逻辑处理包括用于视频数据缓存的SDRAM控制器,实现视频数据跨时钟域处理的FIFO,这部分在发送端和接收端的原理相同,另外发送端有视频格式识别与编码部分,接收端有像素时钟动态重配置部分和行场格式产生部分。

2.1GTP配置及带宽计算

在Spartan-6系列FPGA中,GTP由物理编码子层PCS和物理媒体适配层PMA组成[4],除了并行/串行时钟、底层IP包选择、8B/10B编码选择、数据宽度、Comma字符等参数的配置[5],还需通过Xilinx的集成比特错误率测试仪IBERT,配置收发端预/去加重的权重值、接收端均衡值、接收终端电压及发送端差分输出电压等关键参数[6],找到适合硬件的最佳通信参数,以达到最小的误码率。

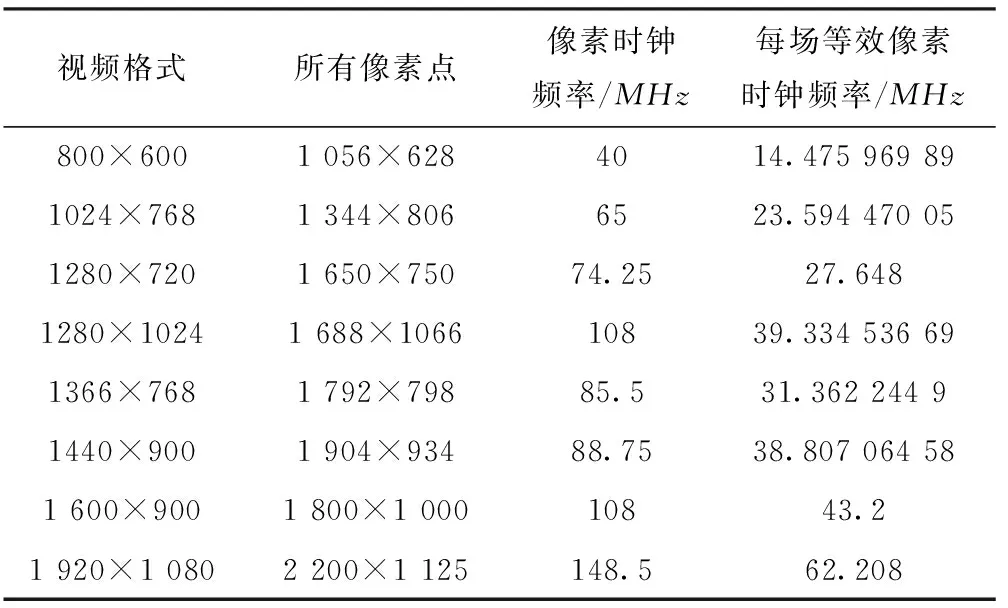

GTP的带宽选取与最大视频格式的场有效时钟有关,在SDRAM缓存一幅图像的前提下,GTP要在下一幅图像到来前将当前图像传输完。传输的分辩率为800×600~1 920×1 080,最大分辨率1 920×1 080的像素时钟为148.5MHz,一场的像素点共为2 200×1 125个,实际像素时钟频率为f1=148.5MHz,实际周期为T1=1/f1,有效像素点为1 920×1 080个,有效像素时钟频率f2和有效周期T2。

一场图像连续传输2 200×1 125个像素点,虽有24bit,但经过RGB转YUV后只有16bit,每个像素的时间长度为T1,所以每场的实际时间为2 200×1 125×T1。

实际上每场只有1 920×1 080个像素点,FIFO将两个16bit转换为一个32bit数据再送给GTP,且经过FIFO处理后其并不间断,而是连续的,所以有效像素个数为1 920×1 080/2个,即一场的时间内,只传输了1 920×1 080/2个32bit数据,所以每个数据的等效时间应该为T2=(2 200×1 125×T1)/(1 920×1 080/2),将T写为1/f,变成1/f2=(2 200×1 125/f1)/(1 920×1 080/2),因此f2=(1 920×1 080)×f1(2 200×1 125×2)=62.208MHz,这就是分辨率1 920×1 080的等效像素时钟频率,其余分辨率的值一样可以计算出来,如表1所示。

表1 不同分辨率的场等效像素时钟

表1中的场有效时钟频率最大为62.208MHz,因此GTP工作频率高于62.208MHz即可。当GTP工作于62.5MHz的速率时,由于使用了8B/10B编码,系统的串行速度为62.5MHz×10/8=2.5Gbit·s-1,这就是GTP的串行工作速度。

2.2SDRAM控制器

系统使用SDRAM缓存视频数据,使用FPGA设计高可靠性的SDRAM控制方案[7-8],选用三星的64Mbit大容量SDRAM存储器K4S643232H-UC60[6]。SDRAM控制器工作在150MHz时钟频率下,FPGA读出FIFO1的数据后进行解码判断,一旦解出场同步码就将VSYNIN_CLR信号置位并保持一段时间,等待SDRAM操作完成,然后状态机返回继续读数据解码。当FIFO1不为空且VSYNIN_CLR为低时产生一个高有效的RD_FIFO1_RDY信号给SDRAM控制器。同理,读出SDRAM的数据写入FIFO2时也会对读出的数据解码,一旦解出场同步码就置位VSYNOUT_CLR信号,等待一段时间,等待SDRAM操作完成后继续对读出SDRAM的数据解码。当FIFO2未满且VSYNOUT_CLR信号为低时产生一个高有效的WR_FIFO2_RDY信号给SDRAM控制器。最大分辨率1 080p共有1 920×1 080个24bit有效数据,经过RGB转YUV后为1 920×1 080/2个32bit数据,而选择的SDRAM有21位行列地址线,即最多存储2M个32bit数据,因此一片SDRAM可存储2.02幅高清图像,每缓存一幅图像后读写SDRAM的行号均清零,因此只需一片SDRAM即可实现图像数据的缓存。

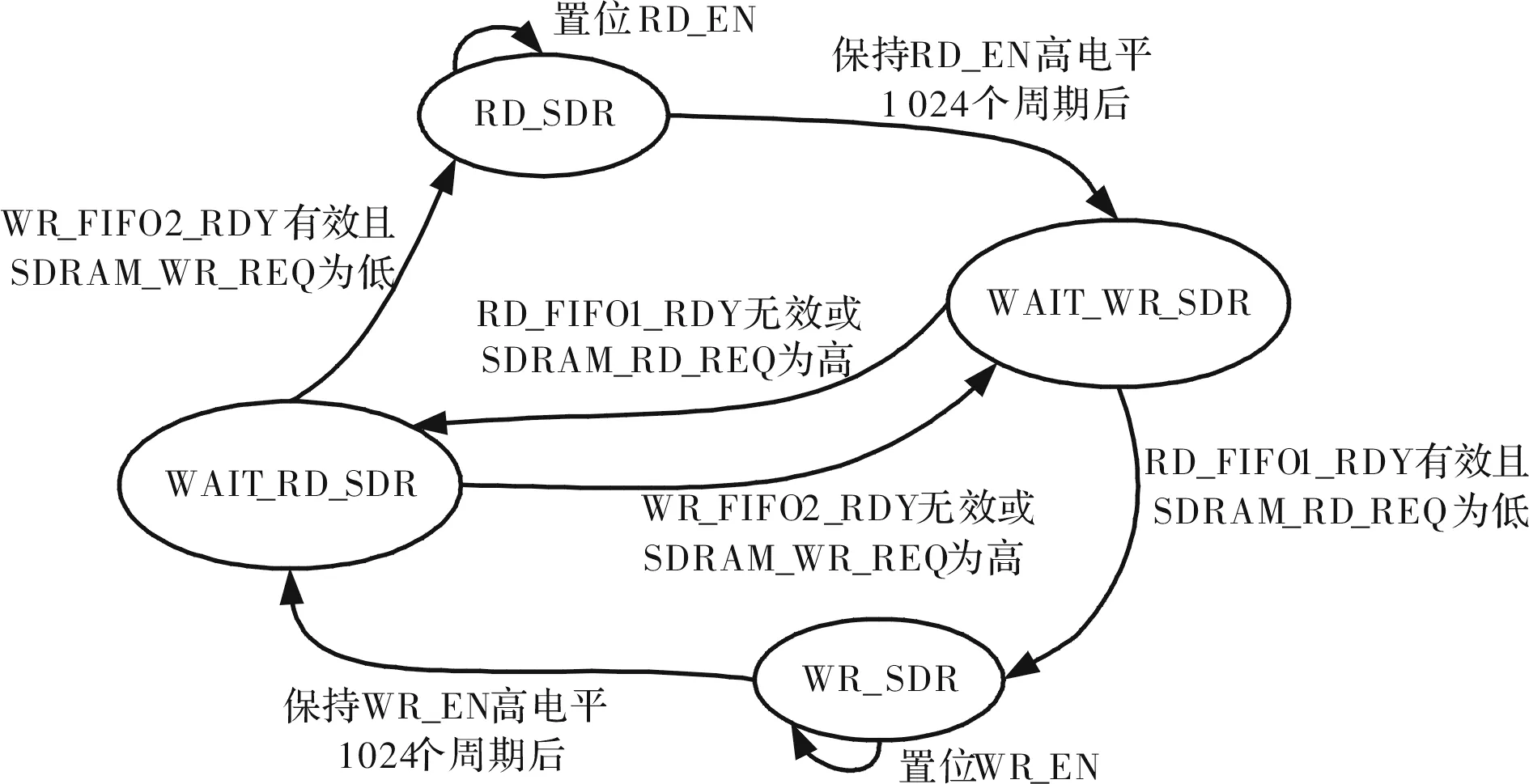

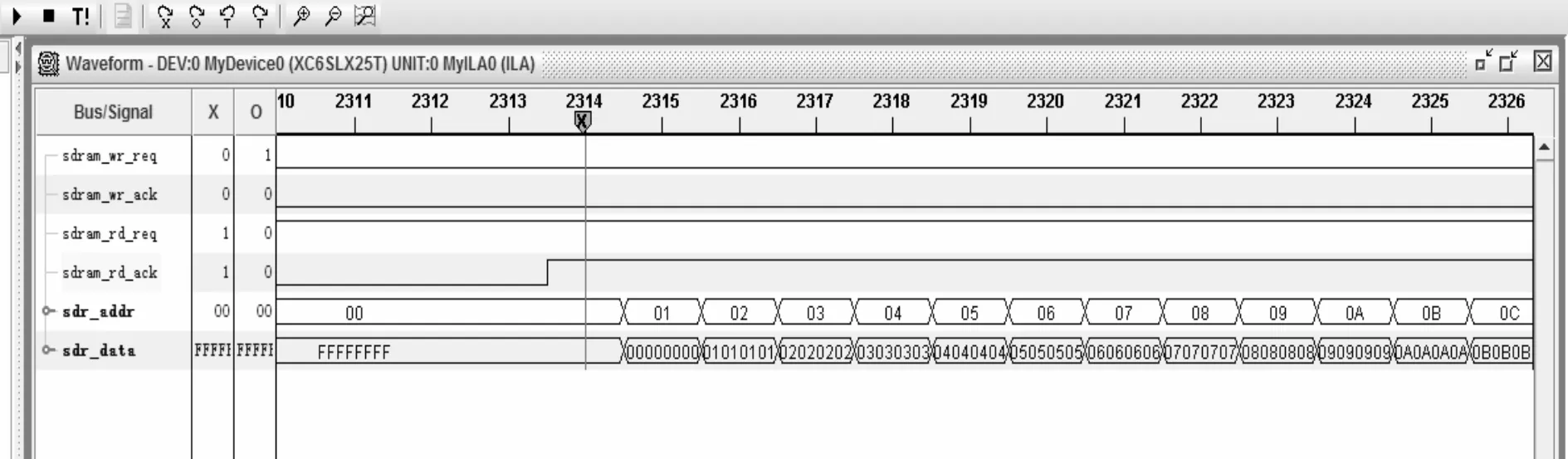

SDRAM控制器中的读写使能控制状态机首先在WAIT_WR_SDR状态进行判断,若RD_FIFO1_RDY信号有效且SDRAM_RD_REQ为低,则置位WR_EN信号并进入WR_SDR状态,状态机在WR_SDR等待1 024个时钟周期后清零WR_EN信号并跳转到WAIT_RD_SDR,如果在WAIT_WR_SDR状态时RD_FIFO1_RDY无效或SDRAM_RD_REQ为高,则状态机直接跳转到WAIT_RD_SDR。在WAIT_RD_SDR状态,如果WR_FIFO2_RDY信号有效且SDRAM_WR_REQ为低,则置位RD_EN信号并进入RD_SDR,等待1 024个时钟周期后清零RD_EN信号并跳转到WAIT_WR_SDR,在WAIT_RD_SDR状态,如果WR_FIFO2_RDY信号无效或SDRAM_WR_REQ为高,则状态机直接跳转到WAIT_WR_SDR状态。图4是SDRAM读写控制状态机流程图。SDRAM使用页突发的方式进行读写,每次读写一整行256个32bit数据,每次WR_EN信号有效或RD_EN信号有效都连续突发读写4次共1 024个32bit数据,因此在WR_SDR和RD_SDR状态都等待1 024个时钟周期,以完成4次突发读写的请求。图5为Chipscope抓取的读出SDRAM数据。

图4 SDRAM读写控制状态机

图5 SDRAM读出数据

2.3视频数据跨时钟域处理

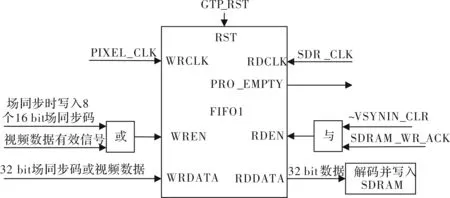

使用一个FIFO进行视频数据的跨时钟域处理,解决SDRAM数据接口与像素时钟、GTP时钟之间的不匹配问题[9]。FGPA获取TFP403芯片采集到的视频数据后写入到FIFO1中,在场同步时向FIFO1中写入场同步码,场同步码由4个32bit数据组成,包含2个相同的8bit视频格式码,视频格式码在视频格式识别与编码部分产生。FIFO1的复位信号为GTP输出的复位信号,写入时钟为视频数据的像素时钟,大小为40~148.5MHz,视频数据有效或写入场同步码时WREN信号都有效,而读信号RDEN则由VSYNIN_CLR信号和SDRAM_WR_ACK信号共同产生,读出FIFO1的数据解码后写入SDRAM,而读出SDRAM的数据同样经过一个FIFO进行处理再以62.5MHz的时钟读出到GTP中。使用FIFO1进行视频数据的跨时钟域处理框图如图6所示。

图6 视频数据跨时钟域处理框图

2.4像素时钟动态重配置

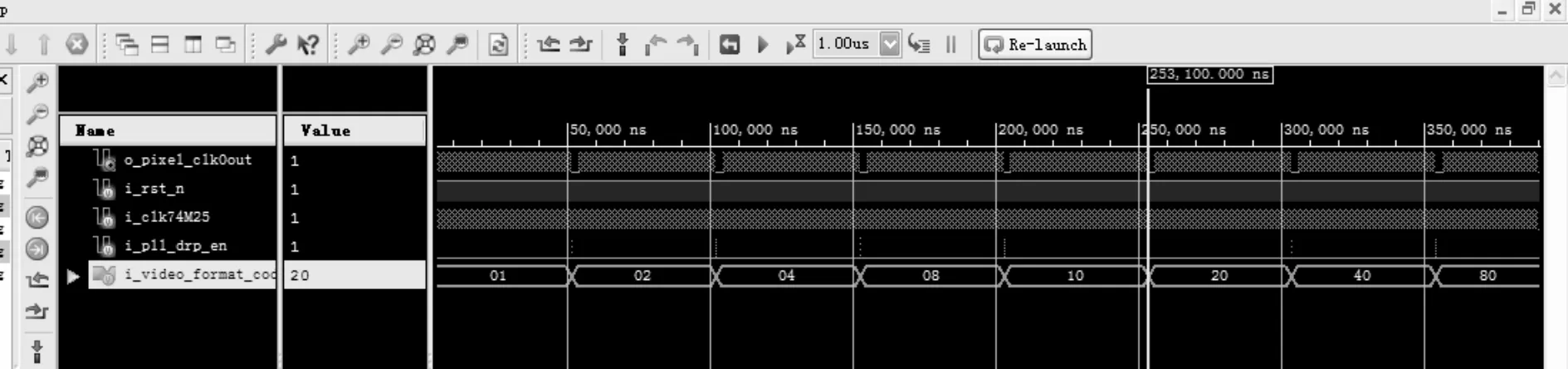

为在接收端及时配置正确像素时钟,发送端要识别8种分辨率的视频格式并编码,通过每行的有效数据个数和每场的有效行数来识别要比通过像素时钟来识别更加准确。接收端解码得到视频格式编码后,若发现视频格式有变化,立即通过PLL_ADV的动态重配置产生对应的像素时钟频率[10]和行场时序,并将视频数据显示到LCD上,经过测试,视频格式变化后产生新的像素时钟频率需要2.452us,可确保视频格式切换的实时性,像素时钟的动态重配置仿真如图7所示。

图7 像素时钟动态重配置仿真图

图8 系统运行实物图

经过调试和验证,使用PC机作为视频源,通过DVI线连接到发送端电路板,发送端经过内部处理后将数据通过光纤发送给接收端电路板,接收端接收数据并通过DVI线连接到LCD显示,实验证明能够清晰流畅地播放视频。实物如图8所示。

3结束语

本文利用GTP在高速串行传输中的优势和FPGA的并行处理优势,实现了720p、1 080p等8种主流分辨率的高清视频数据的传输,解决了传统视频传输系统清晰度不高,对于关键的细节信息无法捕获,无法进行远距离传输等问题。FPGA采集数字视频数据后识别视频格式并经过SDRAM缓存,在GTP中转换为高速串行数据后通过单模光纤传输。视频像素时钟为40~148.5MHz,GTP工作速率2.5Gbit·s-1,接收端对视频数据进行解码、缓存、显示。经过仿真、调试、验证,视频能够清晰稳定显示,并在8种分辨率之间实时切换。

参考文献

[1]廖加文.基于FPGA的高清视频光纤传输系统的研究与实现[D].西安:中国科学院研究生院西安光学精密机械研究所,2013.

[2]张朝春.高清视频光纤传输系统[D].成都:成都理工大学,2012.

[3]熊先越,高进,李保雪.基于Spartan-6的高清视频传输系统[J].光通信技术,2014,38(7):36-38.

[4]Xilinx.XilinxSpartan-6FPGAGTPtransceiversadvanceproductspecification[M].USA:XilinxCorporation,2010.

[5]孙科林,周维超,吴钦章.高速实时光纤图像传输系统的工程实现[J].光学精密工程,2011,19(9):2228-2235.

[6]李凯,何松华,欧建平.Virtex-5GTP和Virtex-6GTX间匹配通信研究及应用[J].计算机应用,2014,34(2):325-328.

[7]朱文斌,刘春平,黄振.基于FPGA的高可靠性SDRAM控制器设计与实现[J].电讯技术,2011,51(10):113-116.

[8]陈雨,陈科,安涛.高速图像处理系统中DDR2-SDRAM接口的设计[J].现代电子技术,2011(12):104-107,110.

[9]庾志衡,叶俊明,邓迪文.基于FPGA与DDR2SDRAM的大容量异步FIFO缓存设计[J].微型机与应用,2011(4):34-36.

[10]KarlKurbjun.PLLdynamicreconfiguration[M].USA:XilinxCorporation,2011.

Design of Fiber Optic High-definition Video Transmission System Based on GTP

MINYingtao,TANGQingshan,LIYajie,ZHONGHaili,ZENGPengfei,LUOZhen,CHENKai,LIHuan

(SchoolofPhysicsandElectronicScience,ChangshaUniversityofScienceandTechnology,

Changsha410004,China)

AbstractTo meet the needs of the long-distance, high-definition picture quality, anti-interference and stability in video transmission system, a high-speed serial transmission based on GTP is proposed to replace the conventional parallel transmission mode, implements long-distance transmission of uncompressed HD video. FPGA identifies the video formats and cached data in SDRAM after acquiring digital video data, which are converted to high-speed serial data in GTP and then transmitted via single-mode fibers at 2.5 Gbit·s-1. The receiver decodes, caches and displays the video data. Simulation, debugging and verification show that the system is capable of stable transmission of and real-time switching between 8 mainstream resolution videos such as 720p and1 080p.

KeywordsGTP; HD Video; fiber transmission; real-time switching resolution

收稿日期:2015- 11- 04

作者简介:闵应涛(1989-),男,硕士研究生。研究方向:数字视频处理。唐清善(1977-),男,博士。研究方向:数字信号处理等。李亚捷(1980-),女,副教授。研究方向:基于光纤的全光处理器件。钟海丽(1967-),女,副教授。研究方向:光电子技术及其应用等。

doi:10.16180/j.cnki.issn1007-7820.2016.07.040

中图分类号TN919.8

文献标识码A

文章编号1007-7820(2016)07-139-04