基于伪PLL的DCDC转换器自适应斜坡补偿电路

修文梁,亓娅魏

(西安电子科技大学 电路CAD研究所,陕西 西安 710071)

基于伪PLL的DCDC转换器自适应斜坡补偿电路

修文梁,亓娅魏

(西安电子科技大学 电路CAD研究所,陕西 西安 710071)

摘要针对时钟外同步DCDC转换器不同,应用频率所需电感值不同对斜坡补偿斜率的影响,提出了一种基于伪PLL的自适应斜坡补偿电路。该电路能够根据DCDC转换器不同的外同步频率自动调节斜坡补偿斜率的大小,在保证转换器稳定工作的同时,不会影响转换器的带载能力和环路的反应速度。通过基于0.35 μm 的标准CMOS工艺,对不同的外同步频率下伪PLL电路产生自适应斜坡补偿斜率的过程进行了仿真验证,在250 kHz~1.5 MHz的频率范围内,伪PLL均能产生自适应的斜坡补偿斜率,保证DCDC工作环路的稳定性。

关键词斜坡补偿;伪PLL;时钟同步;DCDC转换器

随着各类便携式电子产品和大规模集成电路的发展,传统单模块开关电源已不能满足大负载、高效率、小纹波、高频率、更小体积的应用要求,基于锁相环时钟外同步功能的多相交错并联的单电源模块的并联应用可满足上述应用要求。采用峰值电流模控制模式的DCDC开关电源可降低环路补偿难度[1],加快系统对输入电压和负载电流变化的瞬态响应速度,但当占空比>50%时,电感电流会发生次谐波振荡[2]。既有文献已提出了多种方法来解决次谐波振荡的问题,例如分段斜坡补偿、二次斜坡补偿、自适应斜坡补偿等[3-4]。但这些方法只适用于输入输出电压变化导致占空比变化对斜坡补偿影响的问题。所以,本文提出了一种基于伪PLL的用于时钟外同步DCDC转换器的自适应斜坡补偿电路,在不同频率应用时,自动调节斜坡补偿量避免次谐波振荡以获得稳定的工作环路。

1自适应斜坡补偿电路设计

1.1自适应斜坡补偿原理

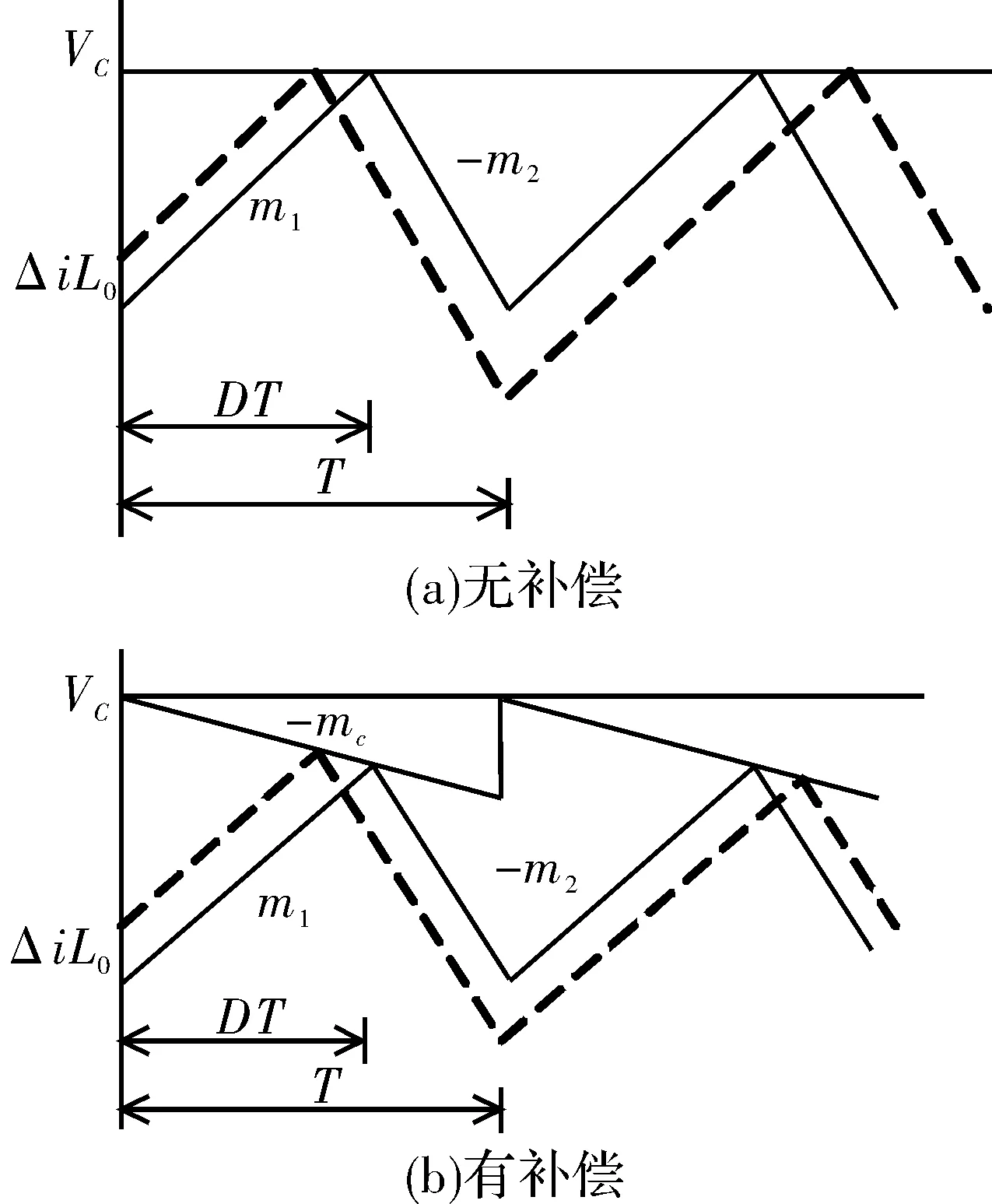

虽峰值电流控制方式的闭环瞬态响应较快,补偿网络较简单,但是当占空比>50%时,CCM模式下,电感电流会发生亚谐波振荡,使转换器工作不稳定[5-6]。如图1(a)所示为CCM模式下占空比D>50%时,无斜坡补偿的电感电流加入扰动ΔiL0时,经过一个周期后扰动量变大了。其中,实线为未加入扰动的电感电流波形,虚线为加入扰动ΔiL0的电感电流波形,m1和-m2分别为电感电流的上升斜率和下降斜率。

如图1(b)所示,当加入斜坡补偿-mc,经过一个周期后扰动量变小了。n个周期后的扰动量ΔiLn与ΔiL0的关系可表示为

(1)

为避免次谐波振荡,mc必须满足的关系式

(2)

图1 CCM模式D>50%,电感电流在无补偿和有补偿的对比波形

对于升压型DCDC来讲,m1和-m2的表达式分别为

(3)

(4)

将式(3)和式(4)带入式(2)中,得

(5)

可见,mc与电感L成反比关系,在不同时钟应用下,电感电流纹波ΔiL通常为电感电流最大值的20%~50%,电感电流纹波ΔiL的表达式为

(6)

将式(6)中的L值带入式(5)中,得

(7)

所以,在相同的电感电流纹波ΔiL要求下,相同的输入输出电压下,所需的斜坡补偿斜率mc与时钟频率fs成正比。在不同的时钟应用中,若针对最小时钟频率进行斜坡补偿,mc值有可能不够而造成电感电流的次谐波振荡;若针对最大时钟频率进行斜坡补偿,mc值有可能较大,使环路接近于电压环控制,降低系统的带载能力[7-8],降低系统环路反应速度。因此,需要针对不同时钟频率fs进行自适应的斜坡补偿[9]。

1.2自适应斜坡补偿电路设计

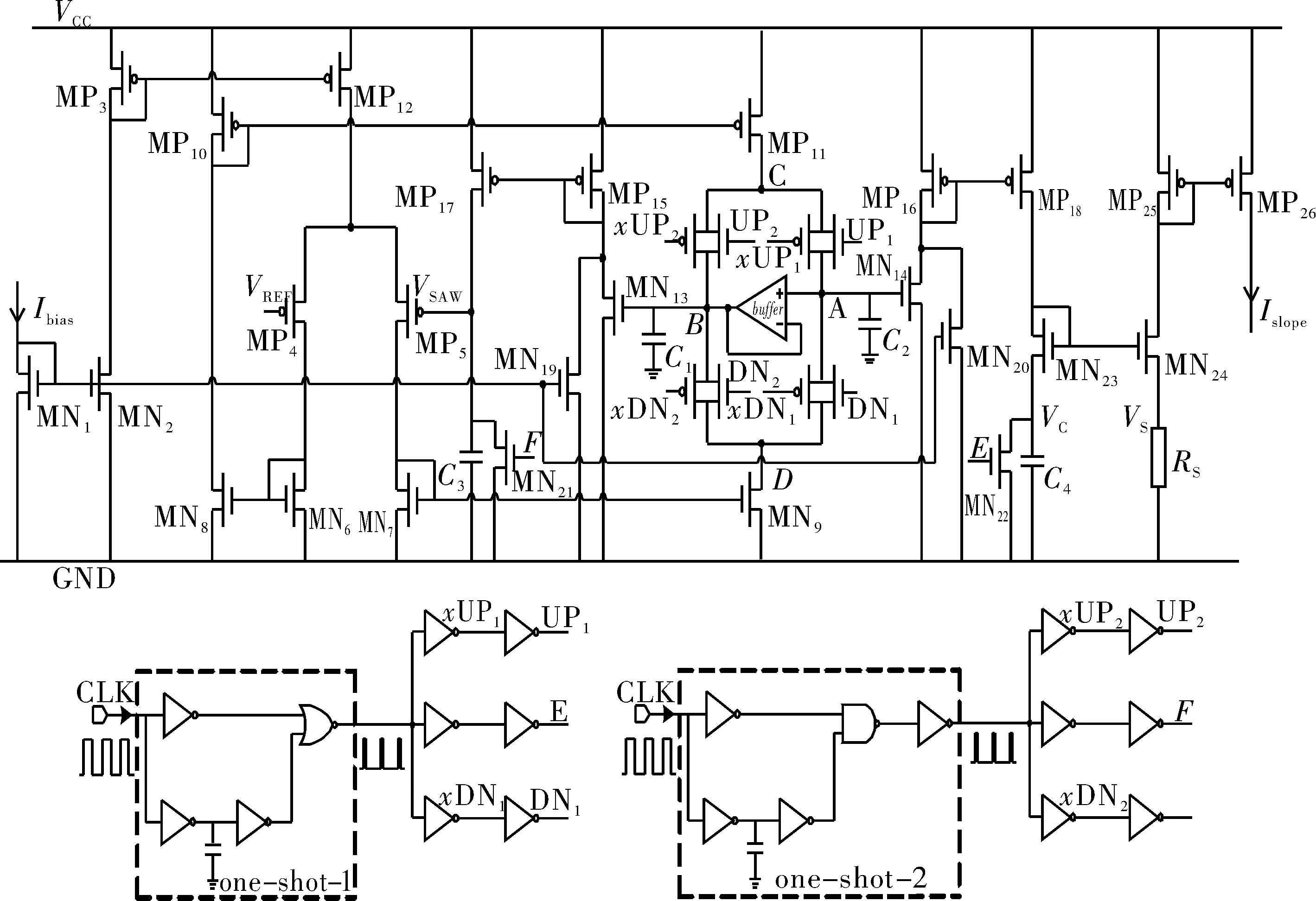

如图2为本文提出的基于伪PLL的自适应斜坡补偿的具体电路,与传统PLL环路相似,伪PLL也存在4个基本单元[10]。

图2 基于伪PLL的自适应斜坡补偿产生电路

由MP4~MP5,MN6~MP8,MP10构成的两级运放作为第一级电路,类似于传统PLL中鉴相器的功能,完成对VREF和VSAW的误差放大;由MN9,MP11这4个传输门和单位增益运放Buffer构成电荷泵电路;C1、C2作为低通滤波器工作;MN13~MN14、MP15~MN18、MN19~MN22、C3、C4作为压控振荡器工作。此外,MN23~MN24、MP25~MP25、RS构成简单的共栅级运放,产生带有自适应斜坡补偿斜率的电流Islope。

第一级鉴相器的误差信号,通过电荷泵电路转换成电流信号IMP11、IMN9对电容C1、C2进行充放电,并产生控制电压VCTRL(A、B点电压),作为压控振荡器的控制电压,通过Buffer的作用使A点电压VA和B点电压VB相等。本文提出的伪PLL有两个压控振荡器电路,MN13、MP15、MP17、MN19、MN21、C3构成一个压控振荡器,作为反馈通路在C3上反馈电压平均值VSAW,使得VSAW≈VREF;MN14、MP16、MP18、MN20、MN22、C4构成一个压控振荡器,作为前向通路在C4上产生电压VC;两个压控振荡器共同作用,使得VC≈VREF,VC再经过共栅级运放产生带有自适应斜坡补偿斜率的电流Islope。

其中,为增加压控振荡器的动态调节范围,MN19、MN20提供固定偏置电流。为减小时钟馈通效应,开关管采用互补开关电路。反馈通路电荷泵的开关信号通过对内部时钟CLK取上升沿得到,前向通路电荷泵的开关信号通过对内部时钟CLK取下降沿得到。

通过伪PLL的环路控制作用,稳态下,可得到如下电压关系

(1)

VC=VSAW=VREF

(2)

其中,μn是电子迁移率;Cox是栅极单位面积电容;W、L分别为沟道宽度和长度;VTN是MN13(MN14)的阈值电压。

IMP16=IMP14+IMP20,IMP20作为固定偏置电流为保证在宽频率范围内,IMP16有一个合理的值,以便该环路能够建立,并得到更宽的动态调节范围。同样,IMP15=IMP13+IMP19。

MP15、MP16、MP17、MP18完全相同,动态变化电流IMP17、IMP18可表示为

IMP18=IMP17=VSAWfSC3=VREFfSC3

(3)

电流IMP18流入由共栅级运放,并对电容C4进行充放电,则电压VC的斜率可表示为

(4)

MN23和MN24完全匹配,共栅级运放两输入端VS与VC大小相等,电阻RS把电压VS转换成斜坡补偿电流Islope,则斜坡补偿电流Islope的斜率

(5)

由式(6)可知,伪PLL得到的斜坡补偿电流的斜率与外同步时钟CLK的工作频率fS成正比例关系。

2仿真结果与分析

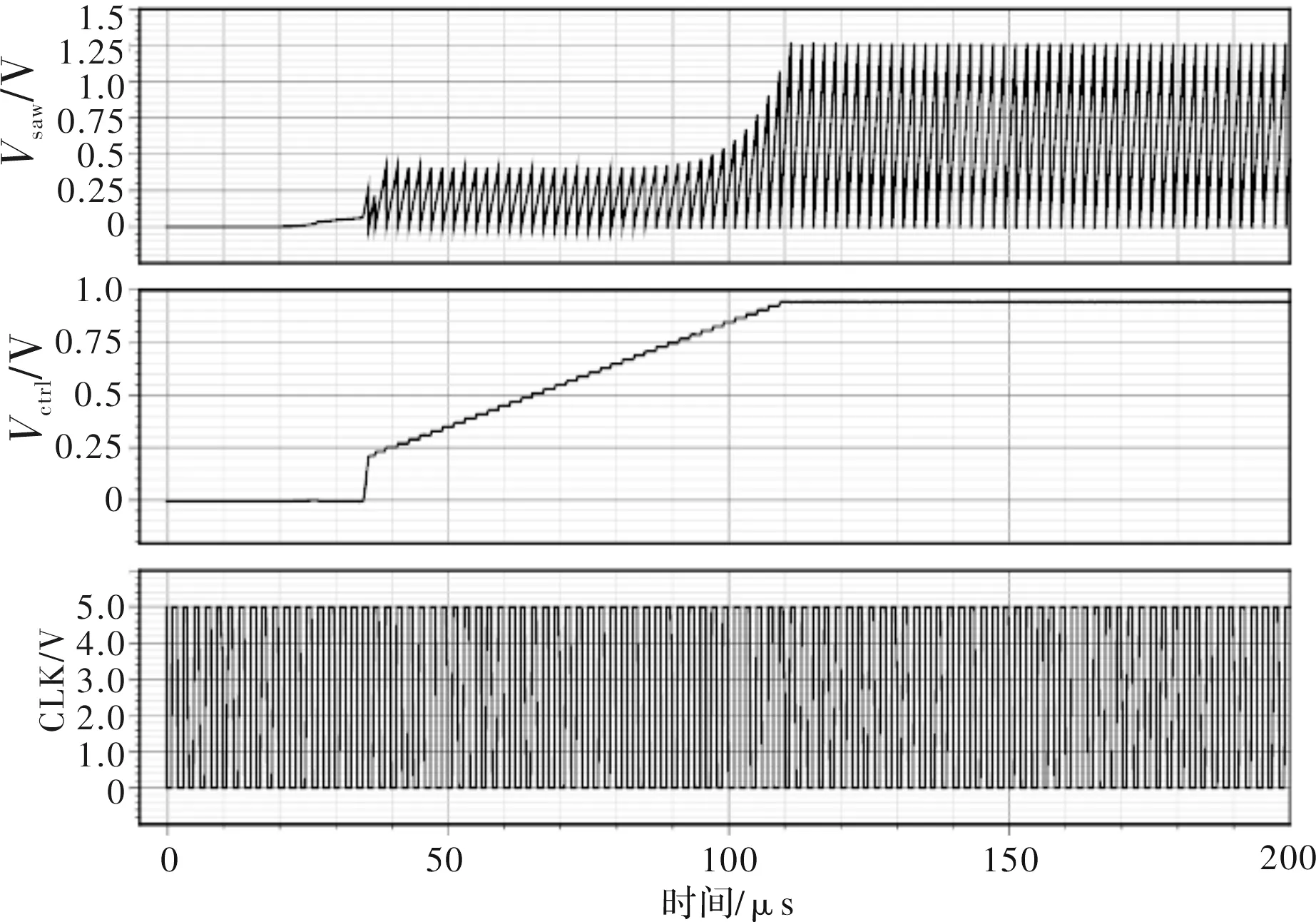

本文提出的伪PLL电路的实现基于0.35μm的标准CMOS工艺,并基于Cadence平台,应用Spectre软件,对不同外同步时钟频率CLK下伪PLL的工作进行了仿真验证。如图3所示为外同步频率fS为500kHz时,反馈电压VSAW、A点电压VCTRL、外部时钟频率CLK的仿真波形图。

图3 CLK频率为500 kHz的主要信号波形

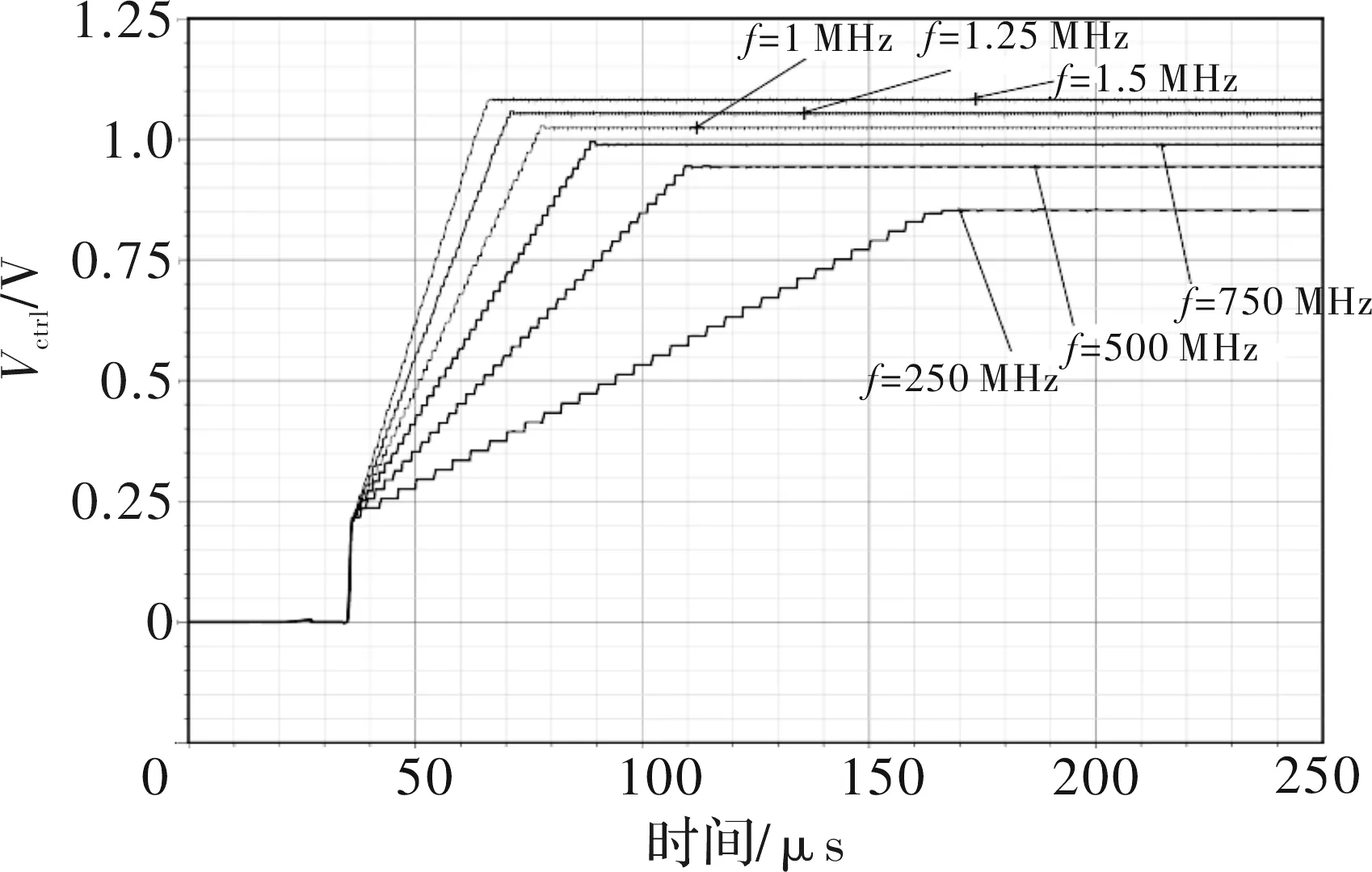

由图3可看出,低通滤波器控制电压VCTRL、反馈信号VSAW是一个逐步建立的过程,三角波VSAW的频率与CLK的频率大小相等,稳态下VCTRL将被稳定到一个值。对于不同的CLK频率,VCTRL的稳态值也不同,三角波VSAW的频率也不同且跟随CLK的频率。不同CLK频率对应的VCTRL稳态值如图4所示。

图4 不同CLK频率对应的VCTRL稳态值

由图4可看出,不同CLK频率对应不同的VCTRL稳态值,伪PLL的稳态建立时间也有差异,CLK频率越大稳态建立时间越快。不同的VCTRL稳态值将会产生不同的斜坡补偿电流Islope,对不同频率下斜坡补偿电流斜率进行自适应调整。

3结束语

针对DCDC转换器在时钟外同步应用中,不同外围电感值对电感电流斜坡补偿斜率的影响问题,提出了一种基于伪PLL的自适应斜坡补偿电路,并进行了仿真验证。与固定斜坡补偿和既有的自适应补偿电路相比,本文提出的伪PLL自适应斜坡补偿电路能够产生一个与外同步时钟频率成正比的电感电流斜坡补偿斜率,保证了不同时钟频率应用时,避免次谐波振荡的发生,又不至于产生过补偿而降低环路反应速度和带载能力。

参考文献

[1]RidleyRB.Anewsmall-signalmodelforcurrent-modecontrol[D].Blacksburg:VirginiaPolytechnicInstituteandStateUniversity, 1990.

[2]RidleyRB.Anew,continuous-timemodelforcurrent-modecontrol[J].IEEETransactionsonPowerElectron,1991,6(6) :271-280.

[3]YangCC,WangCY,KuoTH.Current-modeconverterswithadjustable-slopecompensatingramp[C].Beijing:ProceedingofInternational.ConferenceonSympCircuitsandSystems,2006.

[4]SugimotoY,SugimotoY,SaiY,etal.Feedbackloopanalysisandoptimizedcompensationslopeofthecurrent-modebuckDC-DCconverterinDCM[J].IEEETransactionsonCircuitsSystemⅠ,2015, 62(1): 311-319.

[5]代国定,欧建,马任月,等.提高带载能力的高稳定性自适应斜坡补偿电路[J].电子科技大学学报,2014,43(2):226-230.

[6]SakuraiH,SugimotoY.Analysisanddesignofacurrent-modepwmbuckconverteradoptingtheoutput-voltageindependentsecond-orderslopecompensationscheme[J].IeiceTransactionsonFundamentalsofElectroncsCommunications&Computer, 2005,88(2):490-497.

[7]代国定,胡波,马晓辉,等.提高峰值电流模DC/DC带载能力的限流设计[J].华中科技大学学报:自然科学版,2011,39(4):29-32.

[8]王红义,来新泉,李玉山.减小DC-DC中斜坡补偿对带载能力的影响[J].半导体学报,2006,27(8): 1484-1489.

[9]LiuYX,LiuShibin,LiYanming,etal.DesignofaswitchingfrequencyadaptiveslopecompensationcircuitforfrequencysynchronousDC-DCconverters[J].MicroelectronicJournal, 2013(44):39-346.

[10]BehzadRazavi.模拟CMOS集成电路设计[M].陈贵灿,程军,张瑞智,等,译.西安:西安交通大学出版社,2003.

Adaptive Slope Compensation Based Pseudo-PLL for DCDC Converters

XIUWenliang,QIYawei

(InstituteofElectronicCAD,XidianUniversity,Xi’an710071,China)

AbstractAn adaptive slope compensation circuit in frequency synchronous DCDC converters is presented. Based on a pseudo phase-locked loop (PLL) structure, the slope compensation is dynamically adjusted according to the synchronized switching frequency to guarantee the stability of DCDC converters, as well as the response speed of load transient. Based on 0.35 μm CMOS process and Cadence software platform, simulations in the Spectre simulator verify the function of pseudo-PLL to generate adaptive slope compensation under different synchronous frequencies. Simulation results show that the proposed pseudo-PLL circuit can generate adaptive slope compensation with the frequency range 250 kHz~1.5 MHz, and guarantee the stability of DCDC converters.

Keywordsslope compensation; pseudo phase-locked loop; frequency synchronous; DCDC converters

收稿日期:2016- 11- 14

作者简介:修文梁(1989-),男,硕士研究生。研究方向:模拟CMOS集成电路设计。

doi:10.16180/j.cnki.issn1007-7820.2016.07.034

中图分类号TN386.1

文献标识码A

文章编号1007-7820(2016)07-117-04