以太网、PCle和Rapid lO高速总线比较分析

祝树生,解春雷,仇公望,詹景坤,王小辉(中国运载火箭技术研究院研究发展中心,北京,100076)

以太网、PCle和Rapid lO高速总线比较分析

祝树生,解春雷,仇公望,詹景坤,王小辉

(中国运载火箭技术研究院研究发展中心,北京,100076)

摘要:目前在嵌入式系统中有许多连接元件的方法,但最主要的还是以太网、PCI Express(PCIe)和Rapid IO这三种高速串行标准。本文主要从协议层次结构、带宽选项、拓扑结构、数据包协议、可靠性、可用性和应用场景几个方面对这三种总线的特点进行了比较分析,以供在实际应用中选用分析。

关键词:以太网;PCIe;Rapid IO;高速总线

0 引言

随着电子技术的快速发展,用于设备间、板间和嵌入式系统的可用高速数据传输方式越来越多。目前常用的板间和设备间互联高速总线主要有以太网、PCIe和Rapid IO总线,由于每类总线的原理、机制和应用场景都存在共同点和不同点,因此需要从多方面对这三种总线进行比较分析。

1 总线概念

1.1以太网

以太网是由Xerox、Intel和DEC公司联合开发的基带局域网规范,是一种“尽力而为”的数据包传送方式。在以太网物理层上建立的软件协议,如TCP/IP,需要提供信息的可靠传输,因为基于以太网的系统一般在网络层执行流量控制,而不是在物理层。一般基于以太网的系统带宽都要超配20%到70%。因此以太网最适合对时延要求不高的设备间应用,或带宽要求较低的板上/板间应用。

1.2PCIe总线

PCI Express(简称PCIe)总线由Intel于2001年提出,属于一种基于数据包的串行连接总线,为第三代I/O总线,在第二代总线基础上主要针对板上互连的数据包可靠传送作了优化。PCIe协议交换的是事务处理层数据包(TLP),如读和写,以及被称为数据链路层数据包(DLLP)的少量特殊链路信息。DLLP用于链路管理功能,包括物理层的流量控制。PCIe后向兼容传统的PCI和PCI-X器件,因此PCIe具有能够充分利用与PCI相关的软件和硬件知识产权的优势。

1.3Rapid IO总线

Rapid IO互联架构是一种高性能点对点的包交换技术,支持芯片间以及板间的互联通信,分为并行Rapid IO和串行Rapid IO(SRIO),能满足从嵌入式结构到桌面运算的各种应用需求。与PCIe一样,Rapid IO协议交换的是数据包和被称为控制符的少量特殊链路信息。Rapid IO兼具PCIe和以太网的特性。Rapid IO技术主要面向高性能嵌入式系统的互连通信,它采用高性能LVDS技术,可以在4对差分线上实现10Gbps的有效传输速率,而且具有比万兆以太网、PCI express更高的传输效率。

2 总线比较

2.1协议层次结构

以太网采用三层分级体系结构,即传输层、网络层和数据链路层。传输层提供用用程序之间的通信。网络层也称为IP层,主要是把源主机上的分组发送到其他任何一台目标机上,网络层对路由通道进行选择。链路层包括网络接口设备及其驱动程序,把数据报与传输介质的交换。

PCIe采用三层分级体系结构,即事务层、数据链路层和物理层。事务层主要产生事务包,数据链路层对TLP事务包进行处理,物理层对TLP包进行8b/10b编码。

RaPidiO采用三层分级体系结构,即逻辑层、传输层、物理层,目前逻辑层定义了报文格式,支持五种规范:存储器映射/I/ O系统、消息传递、全局共享存储模式、流量控制和流数据。传输层定义了Rapid IO的地址空间并提供必要的路由信息。物理层描述了设备级接口,说明报文机制、流控机制、电气特性和底层错误机理。

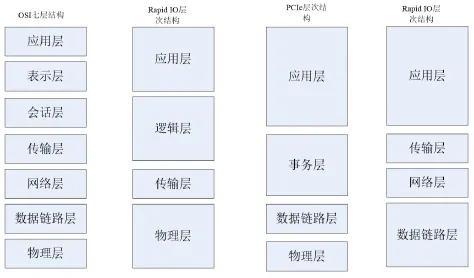

三种协议分层与OSI分层对应关系如图1所示。

2.2带宽选项

以太网、PCIe和Rapid IO在物理/链路层方面的最显著区别是所能支持的带宽选项。以太网带宽具有一代增加10倍的悠久历史。以太网目前工作在10Mbps、100Mbps、1Gbps。

PCIe和Rapid IO采用了不同的方法,因为板上、板间和设备间互连要求功率与数据流匹配。因此与以太网相比,PCIe 和Rapid IO支持更多的通道速率和通道带宽组合。PCIe 2.0 x16通道带宽可达8Gbps,最新的PCIe 3.0的目标是带宽达到10Gbps,而Rapid IO支持1.25、2.5、3.125、5和6.25Gbps的通道速率。PCIe和Rapid IO都支持从单个通道到多个通道的通道带宽组合。PCIe规范中还支持32通道端口。对于给定的通道带宽,Rapid IO端口可以提供多于或少于PCIe的带宽,因此允许系统设计人员调整系统中用于数据流的功率大小。

2.3拓扑结构

Rapid IO和以太网都是模糊拓扑结构。任何端点组都可以用任何拓扑结构连接,包括环形、树形、网状、超立方体以及超复杂网络等更深奥的几何图形。数据包则根据它们的网络地址在这些拓扑中完成路由,并支持不同拓扑选项还允许系统设计人员通过匹配数据路径和数据流程消除系统中的性能瓶颈。系统扩展和演变在Rapid IO和以太网络中是不受约束的。

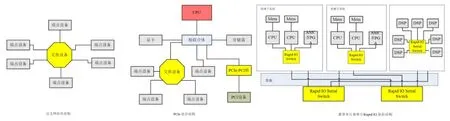

相反,PCIe在顶层支持带单个根联合体的树状结构,具体如图 2所示。其中组成部分包括一个根联合体,多个端点设备,一个交换设备(Switch),和一个PCIe-PCI桥。所有的内部互联都是通过PCIe链路。根联合体是将CPU/存储器子系统和I/O连接起来的设备,能够支持不止一个PCIe接口。每个接口都可以连接单个PCIe端点设备,也可以连接PCIe交换设备或者桥接设备。端点设备作为PCIe传输的请求者或者完成者,是PCIe链路中不可或缺的设备。

2.4数据包协议

Rapid IO、PCIe和以太网在逻辑层方面也有多个差异较大的地方,最明显的区别是所支持的语义。

PCIe数据包支持基于地址的读写语义。在PCIe系统中,发起读或写的实体必须知道系统的全局存储器映射图中的目标地址,这对控制平面应用而言是一种很自然的方法。然而,这种对全局地址映射图的依赖性也会导致难以发展的紧耦合软件系统。PCIe协议也支持通过消息TLP的消息传送。不过消息TLP只支持有限数量的功能,如中断和复位信号。这点与以太网和Rapid IO消息包有很大的不同,后者可用于进程间通信。

与PCIe不同,建立在以太网物理层之上的软件协议只支持消息语义。在发送消息时,发送者只需知道接收地址。寻址机制一般是分层的,因此没有哪个节点必须知道所有的地址。地址可能会随系统发展而改变,支持软件单元实现相互间的松散耦合。这些属性对数据平面应用来说是必要的。

Rapid IO同时支持读/写和消息语义。除了明显的架构优势和系统灵活性外,对读/写和消息处理的支持允许单路互连同时用于控制和数据平面。Rapid IO系统因此要比必须结合PCIe和以太网的系统来得更简单,从而具有降低功耗和成本的优势。

2.5可靠性和可用性

大多数系统对可靠性和可用性都有要求。有可靠性和可用性要求的系统需要误码检测、误码提醒、故障元件分析与隔离以及恢复机制。从高层看,PCIe、Rapid IO和以太网在所有这些方面都要相似的功能。不过在备份策略以及快速隔离系统使之免受故障元件影响的功能方面有很大差别。

图1 三种协议分层与OSI分层对应关系

图2 三种总线拓扑结构

Rapid IO具有与以太网类似的备份、误码捕捉和误码提醒功能。PCIe支持有限的备份策略,因为它的传输层仅限于树状结构。上文提及的PCIe非透明桥接(NTB)允许两个或多个树状结构进行通信,足以实现1+1备份(也称为1:1备份)。NTB很难拓展到采用N+M备份机制的系统。理论上多根I/O虚拟化(MRIOV)可以用来在PCIe系统中支持N+M备份,其中N+M的总数量不超过8。然而,由于MRIOV系统中的子树无法相互通信,从故障恢复可能要求系统中断运行,目的是重新配置系统,以便隔离故障元件,并采用新的元件。

与PCIe和Rapid IO相比,以太网的误码检测机制通常比较慢,因为以太网是针对全球范围内分布的网络设计的。PCIe和Rapid IO都有误码检测和提醒机制,其时延要比以太网小得多。

虽然PCIe和Rapid IO都保证数据包的发送,但在误码条件下它们会弃包,以防止故障元件造成致命拥塞。然而,PCIe误码条件机制是不可配置的。当链路必须再学习时数据包通常会被丢弃。另外,PCIe隔离机制只在几个毫秒后就被激活。这些并不是所有系统都认为理想的行为。

相反,Rapid IO标准允许对误码作出特殊系统响应,如链路再学习。当误码发生时,系统会立即开始弃包,或者它会保留包,并允许拥塞发生。Rapid IO使用“漏桶”式误码计数方法,并有两个可配置门限。DEGRADED门限能尽早提醒系统管理软件链路上正在发生误码。FAILED门限用于触发丢包以实现用户定义的误码率。Rapid IO误码管理的灵活性反映了嵌入式系统设计人员的不断变化需求。

2.6应用场景

由于以太网具有便于连接数量庞大的客户终端,因此其在很多领域都具有不可动摇的技术地位,多年来一直在LAN以及WAN领域被广泛应用,如数据存储、无线终端、电话、工业领域以及其他嵌入式应用。无论在软硬件的可行性、专家的可支持性还是降低系统的复杂性、投入市场的时效性方面,以太网都能大大降低开发成本。

PCIe的应用具有很强的灵活性,PCIe总线可以用于芯片组间的连接,由于其超高的带宽也可以用于连接图形芯片,整个IO系统将重新统一起来,简化计算机系统,增加计算机的模块化。目前已经作为计算机行业的最流行的总线结构,目前大部分的I/O接口采用PCIe总线。

Rapid IO作为一种系统内部互连技术,定位于内部系统互联层次,Rapid IO互连适用于多器件紧耦合的工作环境,可应用在很多场合:DSP连接、处理器和其他器件的点对点主/从连接、控制和数据背板连接、基带和RF板连接等。Rapid IO非常适合于热插拔应用,因为Rapid IO的点到点拓扑结构可以使设备的抽离对相邻设备或子系统仅有非常少的电气影响,甚至没有影响。

2.7互联总线对比分析

综合以上内容,从软件开销、带宽选项、传输模式、拓扑结构、互联模式、传输距离、数据包有效长度等几个方面对三种总线进行对比,具体如表 1所示。

通过上述分析,以太网最适合地理上分散的、具有长时延并且动态网络配置的网络。PCIe则能对单板上的分层总线结构提供最理想的支持。这两种技术都可用于板上、板间和设备间通信,而且在许多应用场合被同时用于同一系统。Rapid IO能将这两种互连的优势结合到单个互连中,并可显著节省功率和成本。

Rapid IO是嵌入式系统的最佳互连选择。Rapid IO具有与PCIe和以太网相似的功能,并具有其它互连技术无法复制的功能,如:低时延、低抖动的系统事件分发;组合式链路层和网络层流量控制机制;可配置的误码检测和模糊拓扑路由可实现高效的备份、高可靠性和可用性;读/写和进程间通信消息语义的硬件实现。这些功能允许系统架构师创建性能更高、功耗更低并且更容易扩展的系统。

3 结束语

未来实时应用系统的高性能需求,使得对总线的带宽、效率、功耗等要求越来越高。随着DSP处理器和嵌入式系统的快速发展,总线技术将成为限制系统的主要因素之一,因此可提供更高带宽、可集成功能、基于硬件协议处理且更加有效的Rapid IO总线技术在未来一段时间将广泛的应用于计算机的的各个领域。

参考文献

[1] Rapid IO Trade Association. Rapid IO Interconnect Specification. http://www.rapidio.org.2002-06.

[2] 樊博.基于PCIe的高速图像采集处理关键技术研究[D].硕士学位论文.中国科学院大学.2013.

[3] 吴强.基于Rapid IO系统互连协议的逻辑设计与验证[D].硕士学位论文.西南交通大学.2009.

[4]赵政.以太网交换及应用技术研究[D].硕士学位论文.西安电子科技大学.2008.

[5]张强.串行Rapid IO互联系统设计与实现[D].硕士学位论文.南京理工大学.2013.

A Comparative analysis of high-speed bus in Ethernet、PCIe and Rapid IO

Zhu Shusheng,Xie Chunlei,Qiu Gongwang,Zhan Jingkun,Wang Xiaohui

(R&D Center,China Academy of Launch Vehicle Technology,Beijing,10076)

Abstract:There are many methods in connection components of embedded system,but the most important menthods are the Ethernet,PCIe and Rapid IO。This paper mainly compares and analyzes the protocol structure,bandwidth,topology structure,message protocol,credibility,usability and application scenario of three kinds of bus,which is provided to choose for actual application.

Keywords:Ethernet;PCIe;Rapid IO;High Speed Bus

中图分类号:TP334

文献标识码:A

作者简介

祝树生(1984-),男,山西朔州人,工程师,主要从事电气系统总体设计工作。

表1 互连总线对比