基于单片VLSI的边界扫描主控器的设计与实现

周同旭

(皖西学院机械与电子工程学院,安徽 六安 237012)

基于单片VLSI的边界扫描主控器的设计与实现

周同旭

(皖西学院机械与电子工程学院,安徽六安237012)

摘要:针对边界扫描主控器常规实现方案执行速度慢, 与通用处理器配合的专用边界扫描接口芯片仍然是依靠处理器运行边界扫描软件,测试速度不高,设计灵活性受到了接口芯片的限制的问题,提出了一种基于VHDL语言描述、FPGA实现的边界扫描主控器的硬件实现方法,设计了边界扫描主控器的基本结构,完成了主控器的VHDL模块化设计,并通过QuartusII开发平台,对各模块进行时序与功能仿真,实现了边界扫描主控器的单片集成。结果表明:用FPGA实现边界扫描主控器,时序验证方便,测试码加载速度快,修改灵活、系统集成度高,是实现边界扫描技术的一种新的有效思路。

关键词:边界扫描;VHDL;FPGA; 可测性设计

随着集成电路(IC)的发展,印制电路板(PCB)越来越复杂,多层板(MCM)设计越来越普遍,芯片管脚数目和密度不断提高,使得基于物理探针的传统测试技术难以为继。新兴的边界扫描技术由于在设计之前就考虑到测试的需求,不但方便芯片故障定位,测试检验效率高,控制逻辑简单方便,而且易于实现,有效地解决芯片测试技术的瓶颈[1],受到了全球测试工业界的广泛认同和支持。目前,许多主流公司的IC芯片均支持边界扫描机制。

边界扫描主控器是实施边界扫描测试技术核心部件,其功能是产生支持边界扫描技术的标准测试信号。主控器的常规实现方案是采用软件编程,这种方式移植性好,但执行速度慢,在高速测试场合下不适用;随着微机接口技术的发展,一些与通用处理器配合的专用边界扫描接口芯片应运而生(SCANPSC100F、SN74ACT8990等),这种方式仍然是依靠处理器运行边界扫描软件,测试速度不高,设计灵活性受到了接口芯片的限制[2]。近年来,大规模集成电路(VLSI)的强势发展使得边界扫描标准的超高速硬件描述语言(VHDL)和现场可编程门阵列(FPGA)实现得到广泛开展,开发具有全硬件实现技术的边界扫描主控器成为可能。本文依据边界扫描测试标准总线,利用VHDL语言在EP1S10F780C6ES芯片上建立边界扫描主控器,并在QuartusII开发平台上通过仿真验证各模块时序与功能,以实现边界扫描主控器的单片集成。

1支持边界扫描标准的芯片结构

边界扫描标准定义了一个4-wire串行总线(另有一条可选的测试线),并且通过这四条测试总线访问边界扫描单元,达到测试芯片内核与外围电路的目的[3-4]。

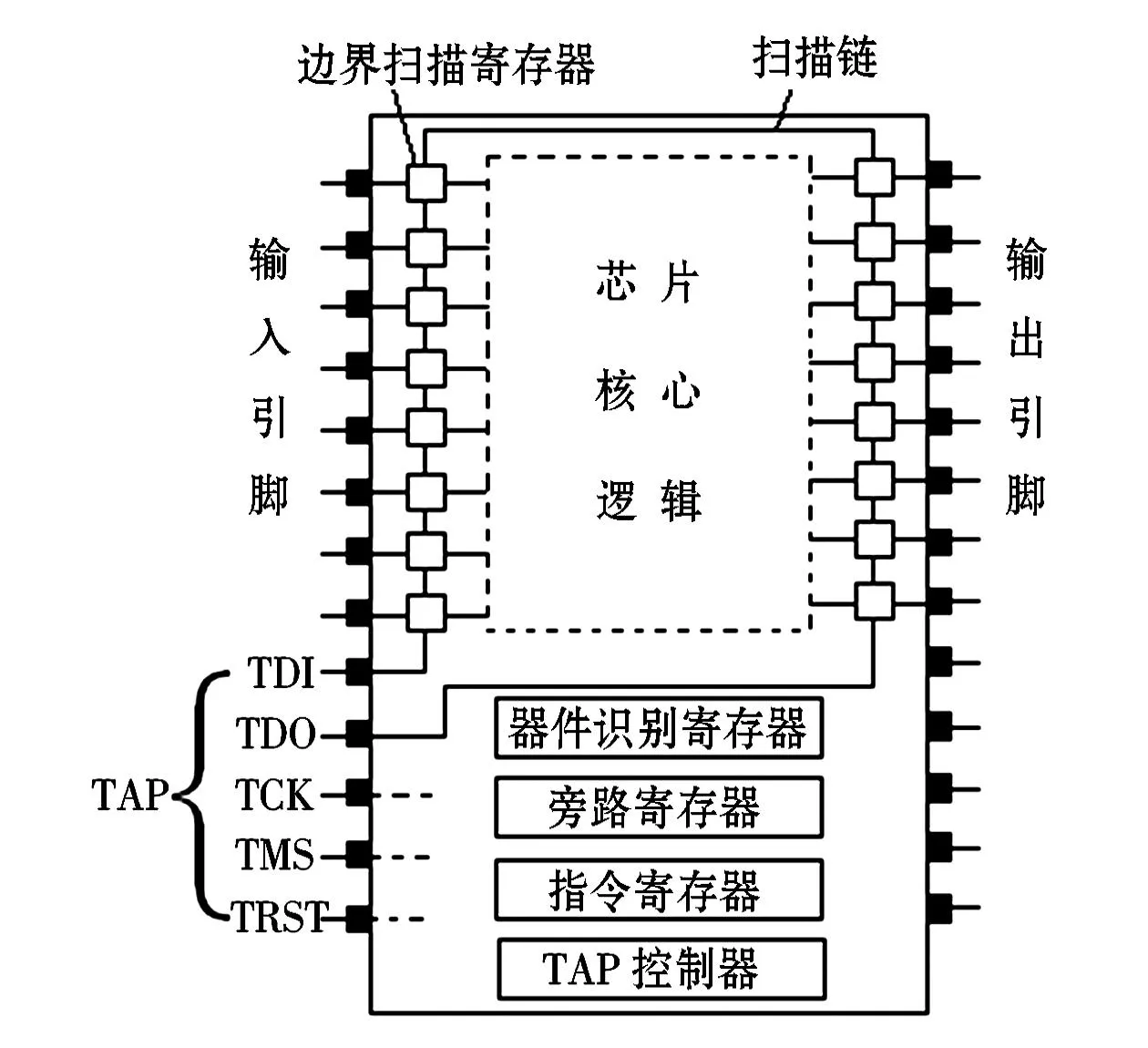

支持边界扫描标准的芯片结构[5],由测试存取通道(TAP)、边界扫描寄存器(BSR)、TAP控制器、指令寄存器(IR)和辅助寄存器组成(见图1)。TAP由四条测试总线组成:测试时钟输入线(TCK),测试方式选择输入线(TMS),测试数据输入线(TDI),测试数据输出线(TDO),边界扫描标准定义的所有操作都是由这四条测试总线来控制。IR、BSR和辅助寄存器的工作由TAP控制器的信号来控制。TAP控制器是一个时序电路,通过TAP接受它的控制信号。标准的TAP至少需要四个IC管脚,同时提供可选择的第五个管脚TRST(测试复位),能使测试逻辑异步复位,复位操作通常也是由TAP控制器完成的[6]29。

图1 支持边界扫描标准的芯片结构

1) TCK。TCK信号允许测试指令和数据进入边界扫描单元或者从边界扫描单元输出。从TDI输入管脚移进的数据必须在TCK时钟脉冲的上升沿进行,向TDO移出数据必须在TCK时钟脉冲的下降沿进行;从系统输入管脚加载数据则在TCK时钟脉冲的上升沿进行。

2) TMS。在TMS输入端接收到的逻辑信号(0或者1)由TAP控制器解码,并用以控制测试操作。在TCK上升沿时,对TMS信号采样,被采样到的信号在TAP控制器中被译码,从而产生芯片内部需要的控制信号。当TAP未被驱动时,必须保持高电平。这可通过在TMS输入管脚接一上拉电阻来实现。

3) TDI。加到TDI上的数据进入到指令寄存器还是边界扫描单元里,是由TAP控制器的状态来决定。在TCK的上升沿,移进数据;当TDI没有被驱动时,必须保持高电平,这可以通过在TDI管脚接一个上拉电阻来实现。

4)TDO。数据从TDO引脚输出发生在TCK时钟脉冲的下降沿。当没有数据输出时,TDO通常设置为高阻态。

5) TRST。TRST是一个可选择的信号,在任何情况下,TRST引脚上出现低电平,都可以使TAP的测试逻辑异步强制进入它的复位方式。边界扫描标准规定,一个TRST信号可用于使TAP控制器逻辑在开机时强制进入复位状态,而与TCK和TMS信号无关。

2边界扫描主控器模块

2.1基本结构

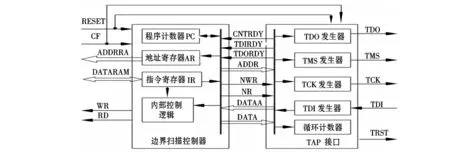

边界扫描主控器主要用于产生相应的测试总线,对被测器件进行测试[7];也可接收被测器件的输出信号,并与预期的输出值进行相应的比较。边界扫描主控器的基本结构如图2所示。

图2 边界扫描主控器基本结构

从图2中可见,边界扫描主控器结构可分为边界扫描控制器和TAP接口两大部分。边界扫描控制器中程序计数器存放当前立即要执行的指令的地址,具有加“1”功能;地址寄存器是提供存储器的地址;指令寄存器长8位,存放当前立即要执行的8位指令码。TAP接口中循环计数器长度为32位,具有减“1”功能,当计数器的值减为“0”时,表示数据串行传送完毕;TMS发生器是根据当前的指令产生相应的测试方式选择信号;TDO发生器具有串行右移的功能,接收边界扫描控制器送来的数据(测试指令码或测试数据码),并将其串行输出到目标器件中;TDI接收器具有串行右移的功能,接收从目标器件发来的测试响应值,可由边界扫描控制器读取并送入存储器进行保存,以便和预期响应值进行比较。测试时钟产生器是一个分频电路,将系统时钟CP进行若干分频,产生测试时钟TCK。

2.2边界扫描控制器实现

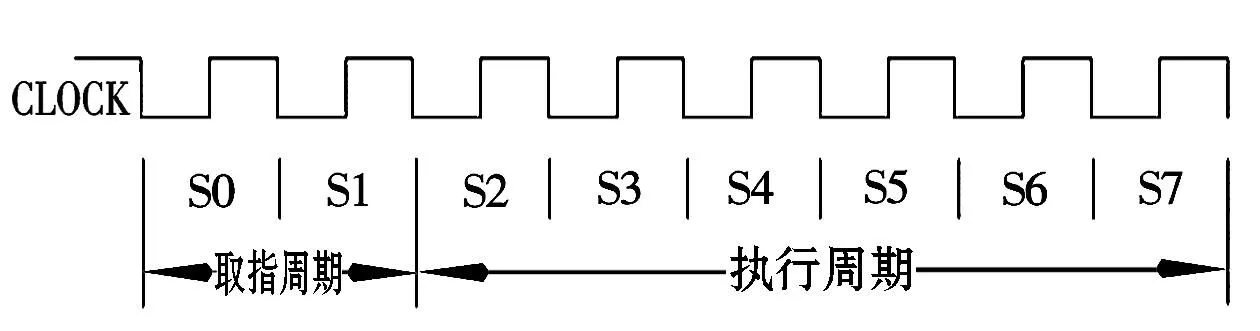

一个完整边界扫描测试系统包括边界扫描控制器和经过可测性设计的被测电路[6]30。边界扫描控制器产生边界扫描测试总线,控制被测电路TAP控制器测试状态的相互转换。因此,边界扫描控制器指令系统主要用于TAP接口的TDO,TDI,TMS及TCK四个信号的产生和有序配合。由于被接收TAP测试总线的被测电路TAP控制器是一个由十六个状态组成状态机,所以本文采用状态机实现边界扫描控制器,实现被测电路状态机的状态转换。该状态机有S0~S78个状态,指令系统中每条指令的指令周期总长度基本上都是8个脉冲长度,其中S0、S1为取指令周期,而S2~S7为指令执行周期(见图3)。

图3 指令周期

每条指令的取指令状态S0、S1都是相同的,即根据程序计数器的值从存储器中取出指令送指令寄存器IR,同时PC自增;而对于不同指令,其执行周期S2~S7是不同的。在进行每一次边界扫描测试时,首先对被测系统电路装载测试指令,然后才能加载测试数据。这些指令和数据都是从 TDO发生器出来,最后在TAP接口TDO引脚加载。所以边界扫描控制器首先控制TMS发生器生成串行指令,接着控制TDO发生器加载测试指令,同样的方法加载测试数据,而此时必须控制TDI发生器自动读取测试响应。以上操作都是在TCK的时钟中进行,即命令控制单元同步于控制TCK生成单元模块输出TCK信号。

2.3TMS发生器

被测电路TAP控制器在TMS与TCK的作用下进行十六个状态的转换,因此TMS发生器主要生成TMS信号来控制TAP控制器完成边界扫描测试的全部过程。根据边界扫描结构中TAP控制器的工作过程,用状态机设计TMS发生器状态的转换,从而TAP控制器在TMS的信号下进行边界扫描测试状态的转换。

用VHDL语言描述状态转换过程,主程序如下:

Case Current-State Is

When Test-Logic-Reset=>

IfOpcode="00001000" Then

If Endir-State="00" OR Endir-State="01" OR Endir-State="10" Then

Next-State:=Run-Test-Idle;

Tms<='0';

End If;

End If;

When Run-Test-Idle=>

⋮

When Exit2-DR=>

⋮

End Case;

Current-State:=Next-State;

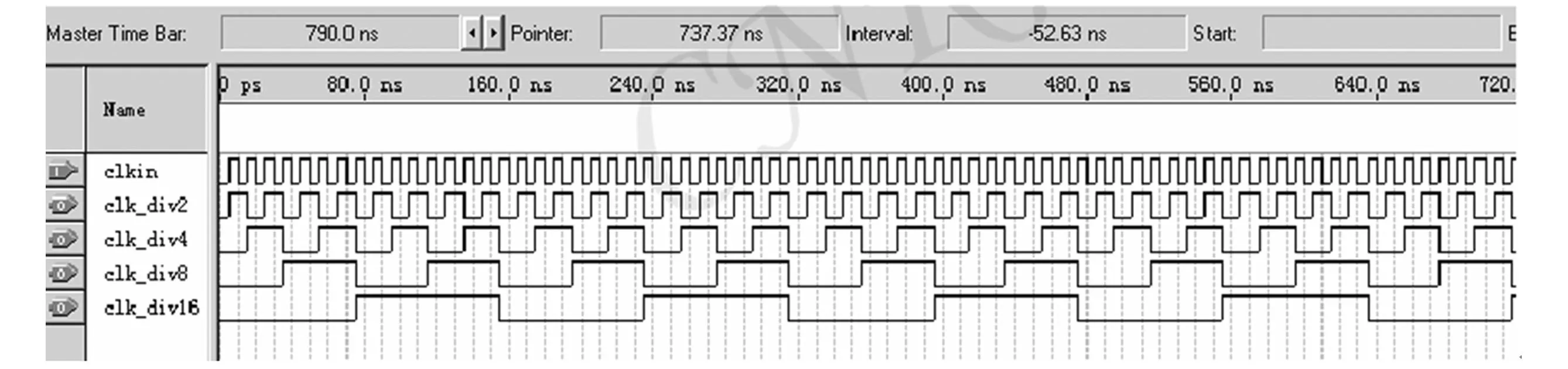

2.4TCK发生器

TCK是测试时钟,它是被测器件进行测试所必需的时钟信号。TMS和TDI信号是在TCK上升沿时取样的,而TDO数据则在TCK下降沿时取样。用VHDL语言描述2分频、4分频、8分频、16分频电路,然后根据寄存器的配置选择分频系数来作为TCK信号的输出。在QuartusII开发平台对模块RTL级仿真,电路时序仿真如图4所示。

图4 TCK发生器时序仿真图

2.5TDO发生器

TDO发生器包括:输出寄存器tdobuffer、4*8的缓冲区tdo-fifo以及一些状态信号。tdobuffer是一个8位的寄存器,存放的是从边界扫描控制器发来的要输出的数据,因为串行输出比较慢,因此将该数据保存到输出缓冲区中进行串行输出,而tdobuffer则变为空,可接受控制器发来的下一个数据,下一个数据也可保存到缓冲区的下一个单元中,依此类推,直至输出缓冲区tdo-fifo已满,则tdobuffer需要等待。一旦tdo-fifo出现空闲的单元时,tdobuffer便可将数据再次送进tdo-fifo中等待串行移位。

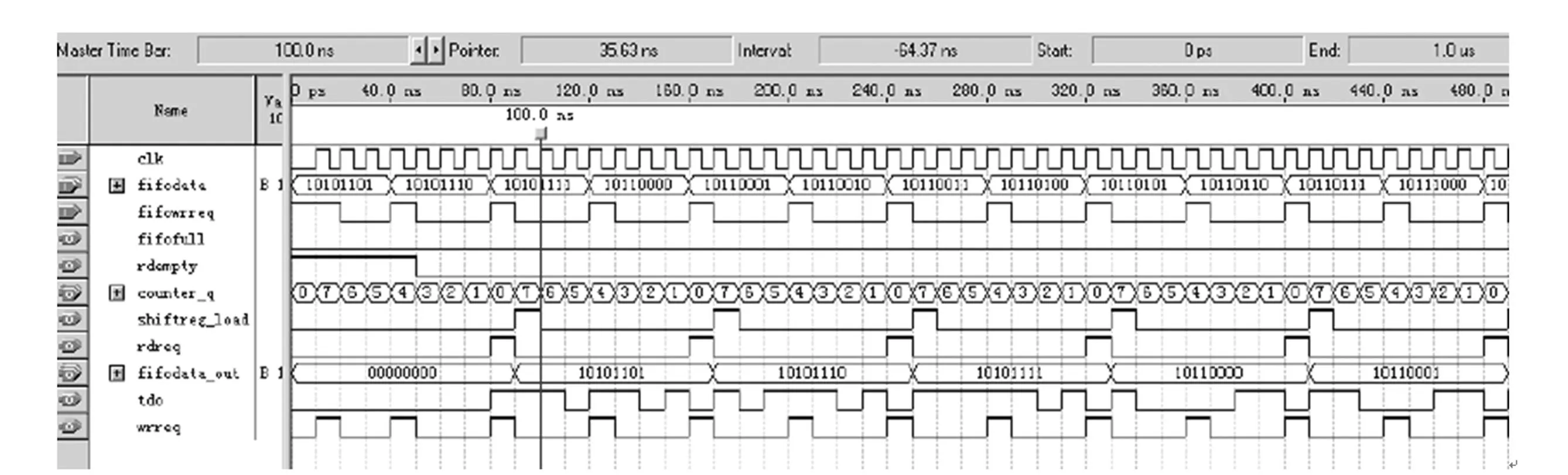

用VHDL语言对上述TDO模块进行描述,并在QuartusII开发平台对模块RTL级仿真,电路时序仿真如图5所示。

图5 TDO发生器时序仿真图

2.6TDI发生器

TDI信号是由被测器件的TDO端口发送来的。当TDO信号产生时,可将其通过被测器件的TDI端口送至被测器件内部,同时可从被测器件的TDO端口接收输出串行数据,送至接口的TDI引脚。该数据是实际从被测器件的TDO端口中输出的值,要将其进行保存,以便和预期的TDO进行比较。TDI接收器的结构类似于TDO发生器,只是数据传送方向与其相反。

用VHDL语言对上述TDI模块进行描述,并在QuartusII开发平台对模块RTL级仿真,电路时序仿真如图6所示。

图6 TDI发生器时序仿真图

3边界扫描主控器FPGA实现

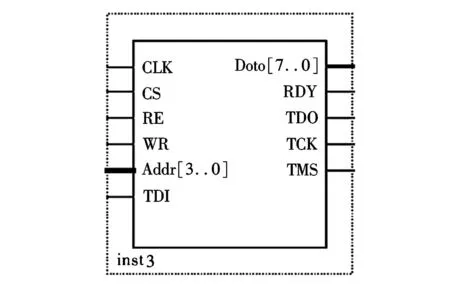

在QuartusII开发平台上对边界扫描主控器顶层模块(见图7)进行编译、综合、优化,通过ALTERA公司Stratix系列的EP1S10F780C6ES器件进行适配和时序仿真,利用固核实现边界扫描控制器及TAP接口,完成边界扫描主控器专用芯片的开发[8]。EP1S10F780C6ES器件有780个引脚,采用BGA封装,工作速度144MHz[9]。

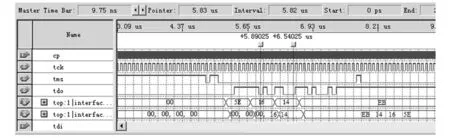

为了验证边界扫描主控器功能,设计了将32位数据“EB14165EH”串行传送至被测器件的IR中,在QuartusII开发平台上仿真了测试执行过程(见图8)。

图7 边界扫描主控器顶层模块

图8 验证仿真波形

在移位指令状态下,TMS一直输出‘0’,进行循环移位,先取低8位“5E”、再依次取“16”、“14”、“EB”进行串行传送,传送时应该串行右移,例如先将低8位“5E”(“01011110”)送至接口中的tdo-fifo,进行串行移位,TDO输出信号依次为‘0’、‘1’、‘1’、‘1’、‘1’、‘0’、‘1’、‘0’,然后取第二个字节的数据“16H”(“00010110”),这时TDO的输出应为‘0’、‘1’、‘1’、‘0’、‘1’、‘0’、‘0’、‘0’,再取第三个数据“14H”(“00010100”),TDO输出为‘0’、‘0’、‘1’、‘0’、‘1’、‘0’、‘0’、‘0’,再取最后一个数据“EB”(“11101011”),这时TDO输出值应为‘1’、‘1’、‘0’、‘1’、‘0’、‘1’、‘1’、‘1’。在最后一个TDO数据输出时,TMS输出‘1’,移位指令结束[10-11]。

4结束语

本文用FPGA实现边界扫描主控器,方便可行,主控器各模块均可使用VHDL语言描述、FPGA实现,无需增加额外的硬件电路,系统集成度高。采用纯硬件FPGA并行处理方式实现主控器,加载速度快,提高了边界扫描的测试效率。由于FPGA具有在系统可重配置性能,使得设计修改灵活、易升级,有助于系统的单片集成。

参考文献:

[1]JTAG. IEEE std 1149.1-2001:IEEE Standard Test Access Port and Boundary Scan Architecture[S]. IEEE. 2001.New York, USA.

[2]LEE NAYES, LARRY LAUENGER. Addin Boundary Scan Test Cability to an Existing Multi-strategy Tester.[J].Autotestcon,1993:110-113.

[3]陈光禹,潘中良.可测试性设计技术[M].北京:电子工业出版社,1997:135-138.

[4]杨廷善.边界扫描技术及其应用[M].测控技术,2000,19(9):5-8.

[5]中国集成电路大全编委会. 专用集成电路和集成系统自动化设计方法[M].北京:国防工业出版社,1997:246-252.

[6]高平,成立,王振宇,等. 数字VLSI电路测试技术——BIST方案[J]. 半导体技术2003,28(9):29-32.

[7]杨士元. 数字系统的故障诊断和可靠性设计[M]. 北京:清华大学出版社,2000:98-105.

[8]游方,钱颜岭. 边界扫描测试软件系统开发[J]. 国防科技大学学报,2000,22(3):114-117.

[9]ALTERA CORPORATION.FLEX 10K Devices[EB/OL].(2011-12-20)[2014-10-27].http://www.altera.com.cn/literature/lit-mp2.jsp.www.altera.com.cn/products/devices/flex10k/f10-index.html.[10]ALTERA CORPORATION.MAX+PLUSII ACCESS Key Guidelines[EB/OL].(2012-6-20)[2014-10-27]http://www.altera.com.cn/literature/lit-mp2.jsp.

[11]WAYNE WOLF.FPGA-Based system design[M].北京:机械工业出版社,2005:197-206.

(责任编辑:何学华,吴晓红)

Design and Implementation of the Boundary Scan Master Controller Based on a Single Chip VLSI

ZHOU Tong-xu

(Department of Mechanical and Electronic Engineering, West Anhui University, Lu an Anhui 237012, China)

Abstract:In the conventional implementation of the boundary scan master controller, the program implementation is slow, and the specialized interface chip matching with the general processor is still used by the processor to run boundary scan software, thus the test speed is not high and its design flexibility is limited by the interface chip. Based on VHDL language description, the hardware implementation method of boundary scan master controller realized by FPGA was proposed. The basic structure of the boundary scan master controller was designed, VHDL modular design of the main controller was completed, the timing and function of each module were simulated by using the Quartus II development platform, and a single chip integration of the boundary scan master controller is realized. The results showed that for the boundary scan master controller realized by using FPGA time sequence verification is convenient, loading speed in code testing is fast, modification is flexible and the system integration is high. It is a new effective way to realize the boundary scan technology.

Key words:boundary scan, VHDL, FPGA, design for testability

收稿日期:2015-06-26

基金项目:安徽省科技厅2013年度自然科学研究资助项目(1301023001);安徽省教育厅2015年度安徽高校省级自然科学研究一般资助项目(KJ103762015B02)

作者简介:周同旭(1975-),男,安徽六安人,讲师,硕士,研究方向:可测性设计,故障测试与诊断技术,分布式发电与控制。

中图分类号:TN407

文献标志码:A

文章编号:1672-1098(2016)01-0040-06