一种基于VPX标准的侦测雷达信号处理系统设计方法

王 锐,翟刚毅,许树军,饶 卿

(中国船舶重工集团公司第七二四研究所,南京 211153)

一种基于VPX标准的侦测雷达信号处理系统设计方法

王锐,翟刚毅,许树军,饶卿

(中国船舶重工集团公司第七二四研究所,南京 211153)

摘要:介绍了一种基于VPX标准的侦测雷达信号处理系统的技术设计和工程实现。在VPX通用平台架构下设计了符合VPX规范的高速采集模块,并结合高速FPGA通用信号处理模块实现了侦测雷达信号的采集与处理功能。

关键词:VPX标准;侦测;信号处理;采集

0引言

随着雷达侦测技术的不断发展,需要传输和处理的信息量也越来越大,对信号处理系统的运算处理速度、数据带宽和传输速率等要求也不断提高[1-2]。传统侦测信号处理以多个功能模块组合而成,集成度较低,设备量较大,单模块数据处理能力较弱,模块间数据传输速率较低,已经无法满足新型侦测产品的使用需求。而基于VPX 标准的信号处理平台具备强大的信号处理、数据处理能力,以及高性能数据交换能力[3],其高密度计算及高速交换架构使得较少的设备量即可以实现复杂的信号处理功能。本文通过该处理平台实现了侦测雷达信号处理系统的设计,完成了宽带侦测信号的高速采集和多通道信号处理功能。

1系统功能

侦测雷达信号处理主要对较大瞬时带宽内的信号进行接收和处理[4]。根据需要侦测目标信号带宽范围的不同,并从提高信号接收灵敏度和信号检测参数精度等方面进行考虑,通常可将前端宽开接收的较大瞬时带宽划分为若干个子信道分别进行信号处理。多通道信号处理可以是时域多通道信号处理、频域多通道信号处理,也可以是频域时域混合的多通道信号处理。时域多通道信号处理系统对每个子信道分别进行数字信号采集和信号处理,系统功能框图如图1所示。模拟前端将接收的射频信号转换为中频信号后,通过A/D模数转换将模拟信号转换为数字信号。数字信号通过数字正交和低通滤波得到信号的幅度和相位值。将信号幅度与算法生成的门限进行过门限判断,如果信号幅度大于门限值则对信号进行参数测量计算,最终将计算得到的信号的中心频率、脉宽、功率电平等信息送至数据处理进行后续处理。

图1 信号处理功能框图

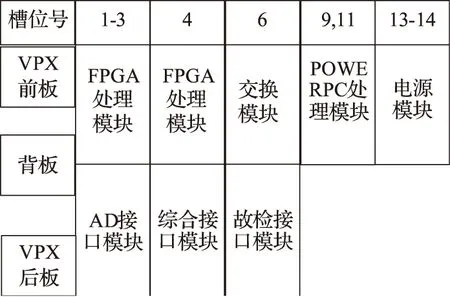

2VPX通用信息处理平台系统结构

基于VPX架构的通用信息处理平台由插(机)箱、背板、散热单元、电源模块、FPGA通用处理模块、PowerPC处理模块、交换模块、接口扩展模块等组成。模块在插(机)箱中通过背板采用前后对插形式,前插模块用于数据的交换和处理,后插模块用于机箱内各板卡状态的故障监测和实现对外信息的输入与输出。VPX内部的模块间通过背板互联或通过交换模块实现数据交换。

3系统实现

在信号采集A/D模数转换时,AD芯片有效位数越多转换精度越高。采样时钟越高,可采样处理的信号带宽越大,但同时对芯片数据传输速率的要求也越高。在200 MHz采样时钟时,12位有效位的采样数据加上4位数据包头和校验位后的数据速率达到3.2 Gbps。而数据传输速率由A/D模数转换芯片、光模块和FPGA芯片收发数据速率的能力决定。

在FPGA信号处理中,时域多通道信号处理系统的运算量主要体现在数字正交和多通道滤波。通常需要保证滤波器的特性能满足通带较小纹波,过渡带较窄且带外抑制能达到60 dB以上。以16 MHz带宽为例,FIR滤波采用128阶4抽取的设计,数字正交后的I、Q两路信号通过128阶滤波器进行频域滤波需要34个DSP处理单元。信号的处理结果通过缓存合成时每个子信道需要8个36 K的BRAM。

根据A/D模数转换芯片、光模块和FPGA芯片收发数据率,以及FPGA芯片DSP和BRAM等资源数量综合考虑,选择Xilinx公司Virtex-6系列的XC6VLX550T作为信号处理芯片。设计采用200 MHz的采样时钟,12位有效位的A/D模数转换芯片,在满足Nyquist采样定理的前提下,将1 GHz的瞬时带宽划分为19个信道,每个信道再划分为4个子信道。采用时域多通道信号处理方法进行信号处理,并根据信号处理对FPGA芯片的资源需求确定每块FPGA处理模块最多可对8路子信道信号进行信号处理。

根据FPGA处理模块的处理能力对应设计了后插板形式的8通道高速ADC信号采集模块,实现了多通道的模数转换功能。采集数据通过背板传输至前插槽与之对应的通用FPGA信号处理模块。通用FPGA信号处理模块实现对信号的数字信道化处理、信号检测、参数测量等功能,并将最终得到的信号频率、脉宽等信息通过背板以RapidIO方式传输至PowerPC数据处理模块。

如前所述,信号处理系统需要处理19个子信道的接收信号,而每个AD信号采集模块最多可以采集8个通道,因此需要3个AD信号采集模块。同时,需要3个FPGA处理模块处理相对应采集模块送来的信号。前3个FPGA处理模块将处理得到的信号参数信息通过背板送入第4个FPGA处理模块。第4个FPGA处理模块将数据合成后再通过其后插槽综合接口模块的光模块送出,并通过背板将数据送至PowerPC处理模块。硬件组成如图2所示。

图2 系统平台框图

前3块FPGA处理模块工作原理相同,将经过脉冲参数测量得到的信号幅度、宽度和载频值,再加上信道标记和脉冲到达时间、天线方位等信息按规定格式合成,形成脉冲描述字后通过背板串行传输至第4块FPGA处理模块。第4块FPGA处理模块将送来的数据进行合成打包处理后通过串行RapidIO总线送入PowerPC处理模块,在PowerPC处理模块中对数据进行进一步处理。具体数据流程如图3所示。

3.1多通道ADC信号采集

ADC信号采集模块对模拟中频信号进行模数转换,转换后的高速数字信号以高速串行方式通过VPX背板传输至与之对应的FPGA通用信号处理模块。每块 FPGA通用信号处理模块包含2个FPGA处理芯片,每片FPGA处理芯片对4路送入的ADC采集数据分别进行解码,并将解码数据转换为并行数据,同时对每包数据头进行误码检测,当发现错误数据时对ADC芯片进行复位操作和初始化配置操作。信号采集流程如图4所示,模拟信号通过50 Ω匹配后送入ADC芯片,转换后的数字信号通过VPX背板送入FPGA处理模块。

图3 数据流程框图

图4 信号采集流程图

ADC信号采集芯片选择了ADI公司的AD9239,每片AD9239包含4个通道可对4路数据同时进行模数转换。AD9239模数转换后的数据格式如表1所示,由8位的数据包头、4包12位的采样数据、8位校验码组成。在初始化芯片时,可以选择芯片的PGM控制信号管脚让芯片输出测试数据,用于FPGA芯片接收对齐数据位,当数据位对齐后再控制芯片输出真实采样数据。芯片的默认测试数据格式为CCAA DDBB 3553 66A5。数据在传输时有3种编码格式可以选择,在FPGA芯片接收数据后需选择对应的解码公式对数据包进行解码。8位的数据包头可在配置芯片时自行选择,也可使用默认值0xFD。

表1 AD9239数据包格式

在FPGA程序中观测接收到ADC芯片4路测试数据和实际数据结果如图5所示。程序初始化配置ADC芯片结束后,先接收固定64位的测试数据CCAA DDBB 3553 66A5用于对齐数据位。当数据位对齐后,程序控制芯片发送真实数据,接收到的64位数据包以0xFD为数据包头,0x00校验位为数据包尾。

3.2FPGA信号处理

FPGA通用信号处理模块对接收到的中频数据首先进行数字正交和频域滤波得到I、Q数据。同时,为了保证系统对小信号的灵敏度,在设计中采用4个低通滤波器对每个通道的信号进行滤波,得到4路子信道I、Q数据分别进行后续处理。

对经过数字正交后的I、Q数据进行求模和相位计算,得到信号包络和瞬时相位。同时统计噪声均值,根据一定虚警率得到门限值;将I、Q求模的结果与门限值比较,得到信号检测结果。然后根据检测结果对信号参数进行计算,得出信号的幅度、宽度和载频值。

图5 ADC 4通道接收数据

在脉冲参数测量中,脉冲的幅度并不是恒定不变。如果采用固定门限,对到达时间的测量将产生较大误差。而对脉冲到达时间采用自适应门限测量,则可以克服脉冲幅度起伏对到达时间的影响。具体方法是将在有效检测结果后0.5 μs内出现的最大值作为信号的幅度估计值,把求模结果和幅度估计值的一半比较,大于该值则认为是超过了门限,对超过门限的数据进行统计平均即可得到脉冲幅度。原理框图如图6所示。图中,A表示幅度,PW为脉宽。

图6 自适应门限测量方法示意图

进行脉冲宽度参数的计算时,在脉冲前沿到达时起始脉宽计数器,在脉冲后沿到达时将结果输出。在脉冲前沿锁存脉冲的到达时间。

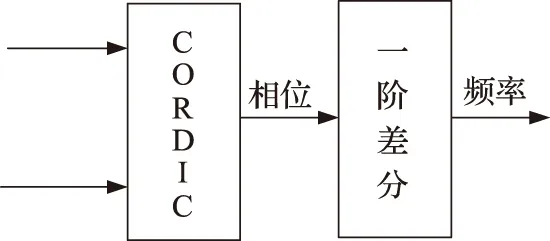

利用CORDIC算法得到瞬时相位后,可以利用频率和相位的关系实现数字鉴频:

f(m)(φ(m)-φ(m-1))/Ts

数字鉴频原理如图7所示。计算得到相位差后即可得到信号的瞬时频率。CORDIC算法可利用FPGA芯片中的IPcore实现。

图7 基于CORDIC算法的数字鉴频原理图

3.3FPGA数据传输

FPGA通用信号处理模块之间的数据主要通过FPGA芯片内部的高速GTX模块进行收发,可通过芯片的IPcore对GTX功能模块进行配置操作。本系统设计的串行最高线速率为2 Gbps,以满足多通道高速数据流传输的需要,其物理传输路径通过背板总线进行分配从而实现模块的高速高集成互联。

3.4信号处理系统测试结果

利用信号源从ADC信号采集模块输入一路脉宽1 μs的脉冲信号,运用Xilinx公司提供的调测软件ChipScope对FPGA内部信号流逐级观测,系统处理结果如图8、9所示。图8为ADC采集模块对脉冲信号采集后传输至与之对应的FPGA处理模块接收解码后的时域结果。图9为第4块FPGA处理模块对前3块模块通过参数测量形成的脉冲描述字合成为一路的结果。脉冲描述字的格式如表2所示。

图8 脉冲信号

图9 合成的脉冲描述字

Bit[0:31]Bit[32:63]Bit[64:95]Bit[96:127]Bit[128:159]Bit[160:191]Bit[192:223]Bit[224:255]报文头通道号和脉冲宽度中心频率到达时间低32位达到时间高32位脉冲幅度方位报文尾和噪声均值

4结束语

作为新一代的总线标准,VPX具有很高的传输速率和带宽,特别适用于数据流量大、运算量大、实时处理要求高的航天、军工等场合。基于VPX标准的通用信号处理和数据处理平台很好地迎合了上述这种发展趋势,使VPX标准成为新一代标准总线的最佳选择。本文通过VPX平台实现了一种侦测雷达信号的采集和处理功能,达到了系统的指标要求。

参考文献:

[1]GE Fanuc Embedded Systems,Inc.VPX:VMEbus for the 21 st Century [M].2007:3-6.

[2]Mercury Computer Systems,Inc.Technology Overview:VITA 46 (VPX)[M].2006:2-4.

[3]郑东卫,陈矛,罗丁利.VPX 总线的技术规范及应用[J].火控雷达技术,2009(12).

[4]宋虎,陈建军.被动探测中的信号技术研究[J].雷达与对抗,2005(4).

Design of signal processing system of reconnaissance and detection radar based on VPX standard

WANG Rui, ZHAI Gang-yi, XU Shu-jun, RAO Qing

(No. 724 Research Institute of CSIC, Nanjing 211153)

Abstract:An implementation method of the signal processing system of the reconnaissance and detection radar is introduced based on the VPX standard. According to the VPX general platform architecture, the high-speed collection module is designed, which is in accordance with the VPX specifications, and the signal collection and processing of the reconnaissance and detection radar are realized in combination with the high-speed FPGA general signal processing module.

Keywords:VPX standard; reconnaissance and detection; signal processing; collection

收稿日期:2015-12-02;修回日期:2016-01-19

作者简介:王锐(1982-),男,工程师,硕士,研究方向:雷达信号处理;翟刚毅(1978-),男,研究员,研究方向:雷达信息处理;许树军(1985-),男,工程师,硕士,研究方向:雷达信号处理;饶卿(1988-),男,工程师,硕士,研究方向:雷达信号处理。

中图分类号:TN911.7

文献标志码:A

文章编号:1009-0401(2016)02-0022-04