基于高速图像数据Flash存储阵列无效块管理

任勇峰,薄 仕,储成群,李 杰,闫安斌

(中北大学 电子测试技术国家重点实验室,山西 太原 030051)

基于高速图像数据Flash存储阵列无效块管理

任勇峰,薄仕,储成群,李杰,闫安斌

(中北大学电子测试技术国家重点实验室,山西太原030051)

摘要:针对高速图像数据FPGA大容量存储的需求,提出了两种基于高速并行化Flash大容量数据存储结构的无效块管理策略,并对比了在不同应用环境下,基于超级块地址映射的无效块管理及基于位索引的无效块管理的优缺点,列出了两种方式的数据无效块列表资源占用情况和存储容量损耗。通过多个工程项目的验证,这两种无效快管理策略各有所长,满足高速并行化存储Flash阵列的不同应用环境。

关键词:存储阵列;无效块管理;超级块地址映射;位索引

在高速图像应用中,分辨率要求一般较高。因此数据的高速大容量有效存储成为了Flash存储研究的重点。由于单片NANDFLASH芯片的存储容量相对较小、读写速度也比较慢,常常需要构建以闪存为基本单元的存储阵列,以此扩大存储容量、提高存储速度[1]。同时由于工艺因素,NANDFLASH不可避免地存在无效块,且数量不等,存在的位置也具有不确定性。因此,在复杂的FLASH阵列系统中对无效块的有效管理是数据可靠存储的关键。

传统的无效块管理策略是以单片Flash作为基本的管理单元。而大容量存储结构体系中存在存储芯片多的特点,若以这种最基本的细粒度完成的无效块管理方式,会使得Flash存储阵列的驱动程序复杂化,并占用过多的FPGA资源。若直接将其应用到大容量存储结构体系中,将不能发挥多通道构架的并发读写和资源的整合与优化设计的优势[2]。因此,针对大容量存储结构的特点,本文提出两种不同应用环境下的无效块管理策略:一种是基于超级块地址映射的无效块管理策略。另一种为基于位索引的无效块管理策略。这两种方法相较于传统方法优势巨大,超级块地址映射的无效块管理极大地节约了映射地址的存储空间,而位索引的无效块管理策略能实现无延时匹配。在高速大容量数据存储结构中,这两种方法更适合应用环境。

1大容量高速存储体系结构

图1为基于FPGA的多片大容量m×nNANDFlash高速存储阵列模块结构,其中m表示存储通道的数量,n表示每个存储通道所含有的Flash芯片的个数。该结构采用FPGA作为主控单元,实现了高速输入数据的接口转换,并利用其片内的丰富的RAM资源构成数据缓存,送入到相应的存储控制逻辑中[3]。

图1 m×n高速存储模块结构

每个存储通道的Flash芯片组的所有数据总线接口D0~D7分别复接在一起,其控制线接口ALE,CLE,WE,RE信号也将复用,忙信号RB是由OC门输出,也可以将其直接连接到一起。而所有芯片的使能信号,包括单个芯片中存在的片选信号(CE1,CE2)必须占用单独的I/O资源。

2无效块管理策略

2.1基于超级块地址映射的无效块识别与预匹配机制

超级块是由多个实际的物理块组成的集合,与使用基本逻辑块的块地址映射的方法相比,其占用的内存将减小为原来的1/N,能大幅度地减小资源占用率,在实现多个NANDFlash芯片的无效块管理中具有绝对的优势。

NANDFlash芯片在进行读、写擦除操作之前,均需要对当前操作块进行有效性识别。这一操作在高速应用中,将占用大量的时间,因此,亟需一种高效可靠的无效块识别方法来提高数据的高吞吐率。其基本原理是,当一个超级块内部的任何一个子逻辑块被检测为无效块时,即认为该超级块是无效块。

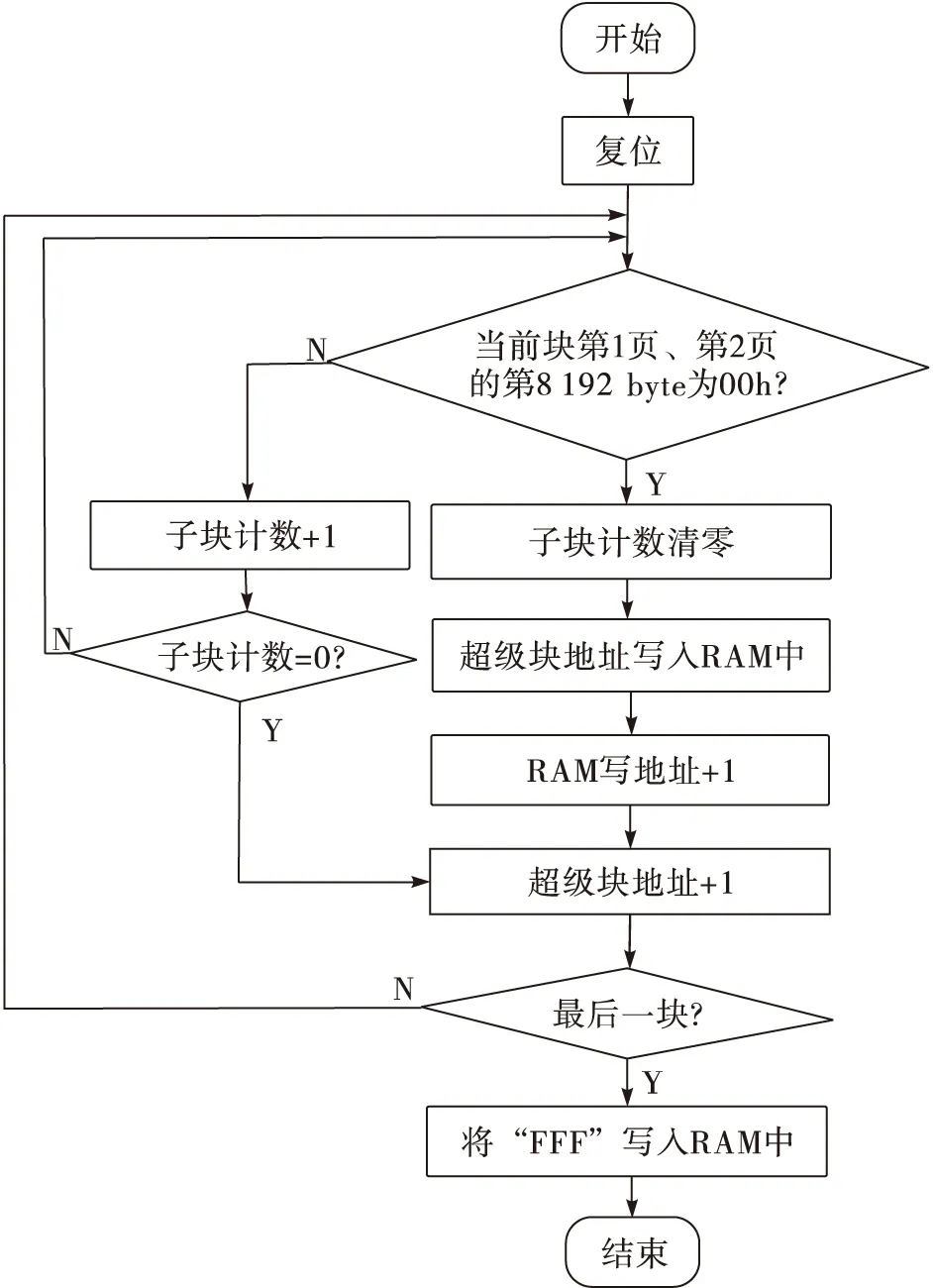

NANDFlash存储阵列中无效块校验流程如图2所示。当系统上电完成复位后,对逻辑控制超级块内的第一个逻辑块进行检测,当检测到当前超级快的第一个子块为非无效块时,将超级块的块地址写到FPGA内部开辟的RAM中,待完成写入操作后,将简单双端口RAM的写地址加一,同时将超级块的块地址加一,并再次对下一个超级块进行检测,直至所有的超级块都检测完成。需要注意的是,为了便于后续的无效块地址的匹配,在生成无效块列表的时候,将“FFF”写入无效块列表的最后,即将芯片的最后一个超级块看成是无效块[4]。

图2 Micron公司NAND Flash无效块校验流程

基于超级块地址映射的无效块校验会造成一定的存储容量的损失,其损失大小与实际的选用的芯片的无效块的个数与位置相关。如果存储通道阵列中的存储芯片的无效块的位置均在同一个超级块内,其容量损失将达到最小,当然,由于无效块的位置在芯片内部具有随机性,其出现这种可能性很小。一般都是在一个超级块的内部存在一个或者多个子块是无效块。

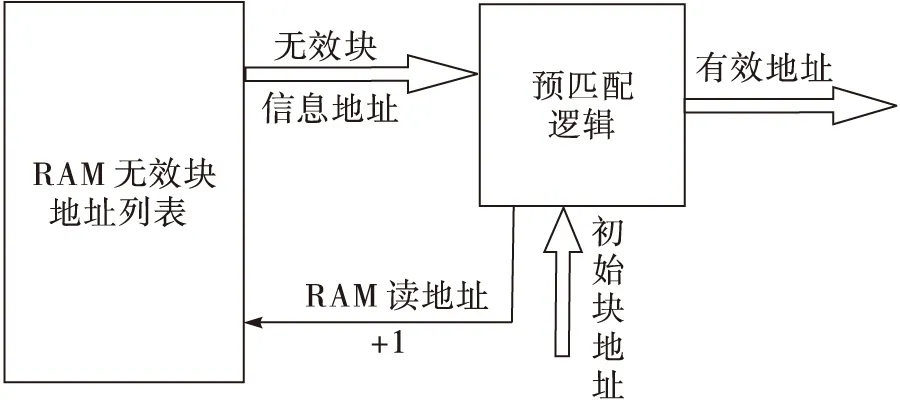

表1所示为MT29F128G08AJAAA芯片内部的块信息。单个MT29F128G08AJAAA芯片内部至多含有4×80=320个无效块,损失的容量为320Mbyte。当采用超级块地址映射时则最大将损失320Mbyte×4=1 280Mbyte的容量。存储通道中Flash器件阵列的个数与损失的最大的容量直接的关系如图3 所示,单个存储通道使用的芯片数量越多,其理论上损失的存储容量就越大。

表1 MT29F128G08AJAAA芯片内部块信息

图3 超级块映射方式下造成的容量损失最大的情况

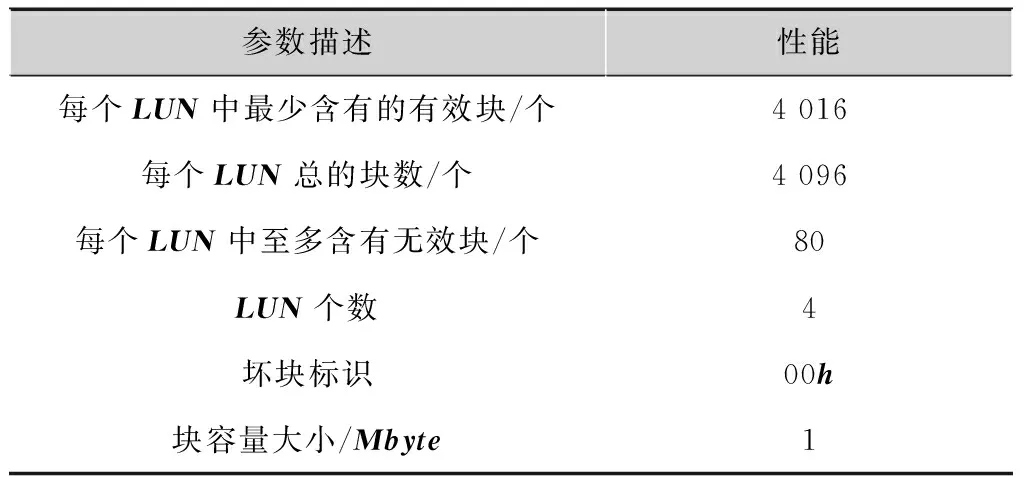

建立相应的无效块列表以后,在对存储通道阵列进行控制时,需要实时完成无效块列表中的无效块地址信息与实际操作的块地址进行匹配工作。图4所示为高效的无效块块地址预匹配原理框图。

图4 无效块块地址预匹配机制实现框图

在对某个块操作的初始阶段,从无效块列表中读出一个无效块的地址信息,该地址信息与初始块操作地址进行预匹配,当读出的无效块的地址大于初始的块地址信息时,则认为该操作块为有效块,可以进行后续的读、写或者擦除操作。待操作完成以后,将初始的块地址进行更新后再与无效块的地址信息进行比较,若仍然要小于无效块的地址,则认为该块也是有效的块。若操作块地址与当前读出的RAM输出的地址相同,则表示该块为无效块,不能对该块进行操作。控制逻辑此时需要将待操作的块地址加1,同时重新从RAM中读出下一条无效块的地址的信息,按照上述流程循环操作,直至所有的块都操作完成。图5为预匹配逻辑的实现流程,其中A表示从无效块列表中读出的无效块的地址信息,B表示的是需要操作的块地址的信息。

图5 无效块预匹配逻辑流程图

2.2基于位索引的快速无效块识别方法与预匹配机制

高速存储通道中基于超级块地址映射的无效块识别与预匹配方法,将完整的无效块地址信息保存在无效块列表中,在匹配过程中需要将所保存的无效块地址信息读出,并与当前的操作地址信息进行比较,使得Flash存储阵列读写操作存在一定的时间延时,不能极大地发挥多通道构架的并发读写和资源的整合与优化设计的优势,此外,造成了大量的存储容量损失也是该无效块识别存在的一个缺陷[5]。为了解决上述不足,实现多芯片存储阵列中的无效块的快速检索与高效识别,提出了一种基于位索引的快速无效块识别和实时的预匹配机制。

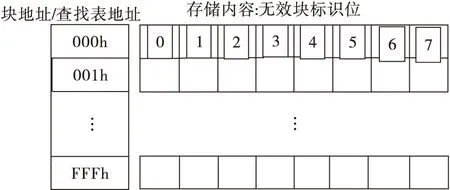

以2芯片阵列结构为例,该结构中包含2片MT29F128G08AJAAA芯片,共存在8个LUN模块,即1个超级块由8个LUN中相同位置的子块组成,也就是说1个超级块地址对应有8位的无效块标识符。因每片上述芯片的每个LUN模块被划分为4 096个存储块,故本例程中的超级块地址的深度为4 096,转换成16进制表示就是000h~FFFh。假设用二进制数据“1”表示的是无效块,“0”为有效块标识。这样就可通过存储列表的地址来表示超级块的块地址,根据其保存的数据来识别该地址所对应的物理块是否是无效块。图6所示为改进的基于位索引的无效块列表结构。无效块列表的地址也就是超级块对应的地址,其多存储的信息则表示为各LUN模块的无效块标识位。这样能够遍历存储空间中的所有的块,避免了额外的存储容量损失。

图6 基于位索引的无效块列表结构

图7所示为基于位索引的无效块列表生成流程。首先开辟一个存储深度为4 096,数据位宽为8bit存储模块,并将其所保存的内容置“0”。当开始无效块检测后,若检测到超级块内的某个子块为无效块,将其在无效块识别字的相应位置给置成“1”。待该超级块内的所有子块均检测完毕后,将无效块识别字写入到当前超级块地址所对应的存储空间中,直至所有的超级块都完成了检测。

图7 基于位索引的无效块列表生成流程图

位索引式快速无效块识别方法在Flash存储阵列进行读写操作中,读写有效块与识别无效块是并行执行的,换言之,当主控芯片对阵列中的Flash有效块进行读写操作的同时,也对无效块列表检索,并在当前有效块读写操作完毕前,能够及时准确地将下一个有效块的地址提前给出。从另一种角度讲,这样就大大削减了无效块的识别过程,可以认为读写操作是不间断性的,从而大大提高了Flash存储阵列操作速率。其匹配流程图如图8所示。

图8 基于位索引的无效块预匹配流程图

3 性能对比分析

为测试实际的NANDFlash器件的无效块的分布情况,利用ChipScope软件获取无效块列表中的无效块地址信息。随机抽取了10片某同一批次的Micron公司的MT29F128G08AJAAA大容量芯片进行了无效块测试。采用了上超级块映射结构,即根据芯片内的4个LUN结构,使每个超级块含有4个子块,其超级块地址的范围为:000h~FFFh,共4 096个超级块。

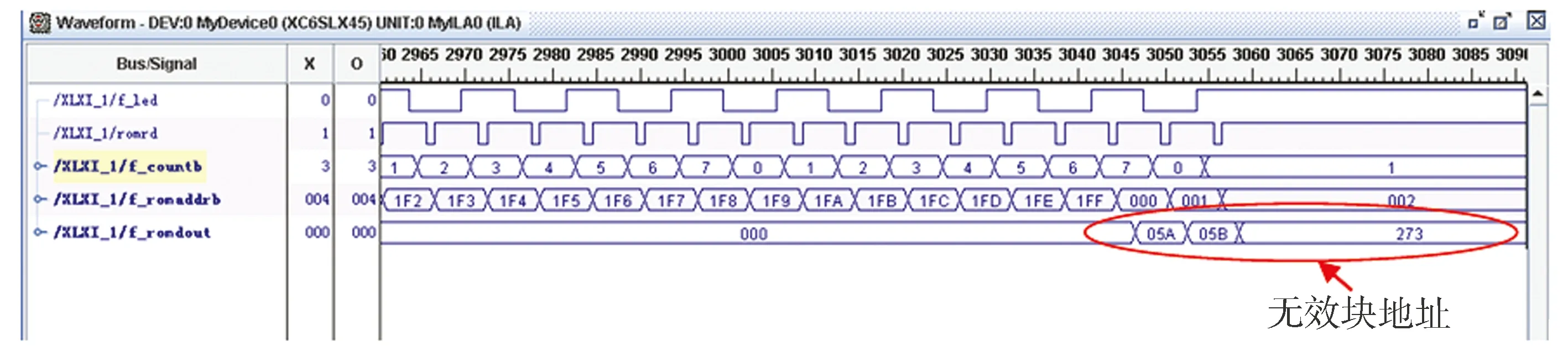

图9所示为某一个芯片的无效块测试的FPGA的采样时序图,存在有3个无效块,其块地址分别为05Ah、05Bh以及273h。表2所示为随机抽取的10片芯片的无效块测试的结果统计。

图9 某一芯片无效块测试FPGA采样时序图(截图)

表2 无效块测试结果统计

从两个方面对上述统计结果的无效块识别与匹配机制的性能进行对比分析,即无效块列表占用的存储资源的容量大小以及整体的存储容量的损耗情况(1#:基于超级块地址的无效块识别与匹配;2#:基于位索引的无效块识别与匹配)。

1)无效块列表占用存储资源

无效块列表是利用的是FPGA内部的存储资源实现,对于1#方案,无效块列表的容量的大小受所选用的器件的中单个LUN中所含有的最多的无效块数量所决定,如单个芯片MT29F128G08AJAAA中的每个LUN中最多含有的无效块的数量是80个,采用超级块映射的方式下,其最坏的情况下会有80×4=320个无效块,无效块的地址为12位二进制数,故其无效块列表最大将达到:(320×12bit=480byte)。N个芯片在最坏的情况下的无效块列表的大小为480byte×N。2#方案中,超级块地址的深度就是无效块列表的深度,即无效块列表的深度为4 096,而无效块的标识位宽与总的LUN个数有关,对于有着M个Flash芯片的存储通道,无效块列表的容量大小为:(4 096×4×M)/8=2k×M字节。由此可以看出,1#方案所需要的FPGA内部的存储资源要比2#方案所需的资源要小,且不到其大小的1/4。

2)存储容量的损耗

1#方案是利用超级块的地址作为无效块地址识别的最小单位,只要在超级块内部的任何一个小块中存在一个是无效块,则会认为整个的这个超级块都是无效块。2#方案中将超级块中的小块作为识别的最小单位,其内部的所有的小块都将被标记,避免了1#方案中的有效块被当成无效块的情况。2#方案的容量损失只于芯片中存在的总的无效块的个数有关,即其最大的容量损失与芯片的个数N的关系为:(80×4)×NMbyte。而1#方案中的造成的容量损失与芯片个数N的关系为:(80×4)×N×4Mbyte即1#方案的存储容量损失是2#方案损失的4倍关系。

4小结

针对不同的应用环境基于超级块地址映射的无效块识别和基于位索引的无效块识别方法均具有一定的应用价值。在高速大容量存储环境中,这两种无效块识别方法对Flash存储阵列的读写操作均有绝对的优势,基于超级块的地址映射的无效块识别,占用主控芯片RAM资源较少,对主控芯片性能要求不高,但其在读写操作中存在一定的时间延时,而且资源利用率也不高,更适用于超大容量的数据存储阵列环境;基于位索引的无效块识别方法读写操作较快,资源利用率也较高,但其占用主控芯片RAM资源较多,更适合持续超高速、高密度的数据存储环境。

致谢:

论文成果要感谢任勇峰老师、储成群老师和刘东海师兄的指导,以及李杰同学和闫安斌同学在设计中进行的大量试验和测试。

参考文献:[1]杨立宏, 毛亚杰, 行长印. 基于Flash的CCD相机数据高速存储系统设计[J].长春理工大学学报(自然科学版),2009,32(1):31-34.

[2]王芳, 李恪, 苏林,等. 空间太阳望远镜的星载固态存储器研制[J].电子学报,2004, 32(3): 472-475.

[3]张科, 郝智泉, 王贞松. 一种基于新体系结构的空间固态记录器原型系统[J].电子学报,2008, 36(2): 285-291.

[4]宋杰, 何友, 唐小明. 基于FPGA的超高速雷达信号实时采集存储系统[J].电子技术应用,2005, 31(11): 18-20.[5]任勇峰, 张文栋. 高精度、高速雷达图像记录设备的研究[J].弹箭与制导学报,2004 (2): 71-74.

任勇峰(1968— ),博士生导师,主要研究方向为电路与系统,信号采集及存储;

薄仕(1989— ),硕士生,主研电路与系统、信号采集及存储;

储成群(1987— ),博士,主研电路与系统、测试计量技术;

李杰(1989— ),硕士生,主研电路与系统、信号采集及存储;

闫安斌(1989— ),硕士生,主研电路与系统、信号采集及存储。责任编辑:闫雯雯

Invalidblockmanagementbasedonhigh-speedmassimagedataflashstoragearray

RENYongfeng,BOShi,CHUChengqun,LIJie,YANAnbin

(National Key Laboratory for Electronic Measurement Technology, North University of China Taiyuan,Taiyuan 030051,China)

Abstract:According to the need of the high-speed mass image data storage base on FPGA,it is proposed that two kinds of invalid fast management strategy of the structure based on high-speed parallel Flash high-capacity data storage, and compares the advantages and disadvantages of the invalid block management based on the super block address mapping and based on an index of invalid block management in different application environment, lists the two ways of invalid data block list resource utilization and storage capacity loss. Through multiple validation of the project, the two kinds of invalid fast management strategy strengths and meet the high-speed parallel Flash storage array of different applications.

Key words:memory array;invalid block management;super block address mapping;bit index

中图分类号:TP391

文献标志码:A

DOI:10.16280/j.videoe.2016.04.008

作者简介:

收稿日期:2015-11-16

文献引用格式:任勇峰,薄仕,储成群,等. 基于高速图像数据Flash存储阵列无效块管理[J].电视技术,2016,40(4):38-42.

RENYF,BOS,CHUCQ,etal.Invalidblockmanagementbasedonhigh-speedmassimagedataflashstoragearray[J].Videoengineering,2016,40(4):38-42.