三维集成电路硅通孔热特性的COMSOL模型

赵 朋,林洁馨,傅兴华

(贵州大学 大数据与信息工程学院,贵阳 550025)

三维集成电路硅通孔热特性的COMSOL模型

赵朋,林洁馨,傅兴华

(贵州大学 大数据与信息工程学院,贵阳 550025)

摘要:利用COMSOL软件建立了三维集成电路散热模型并进行仿真。仿真结果显示,在元胞块之间插入TSV网络可以有效将三维集成电路温度控制在一个安全范围之内,而且随着TSV半径的增大,三维集成电路散热效果更好。

关键词:三维集成电路;硅通孔;散热问题;COMSOL模型

在过去的几十年微电子器件的尺寸一直按照摩尔定律下降,但目前制作这些电子器件的工艺技术开始达到物理极限[1],同时人们对微电子设备尺寸和集成度的要求不断提高,三维集成电路(3D IC)已经超过了二维集成电路受到越来越多的重视。三维集成电路内部包含着多个叠层芯片,通过硅通孔(Through-Silicon Via,TSV)实现芯片之间的互连[2],区别于传统的二维集成电路在水平方向的集成,三维集成电路是在垂直方向以多个有源层进行堆叠[3]。

TSV技术是通过在芯片与芯片之间、晶圆与晶圆之间制作垂直方向的导通,实现芯片间互连的最新技术,它使3D封装在一定尺寸的芯片中并实现更多功能,同时避免了高密度下的2D封装长程互连导致的RC延迟现象[4]。TSV可由铜、钨、多晶硅或者碳纳米管束组成;环绕TSV加一层绝缘层,以防止TSV与硅衬底间漏电流的产生,绝缘层通常选用SiO2;为防止铜原子向硅衬底的扩散,还需在铜与绝缘层间加一层阻挡层,阻挡层可选用Ti,TiN或Ta等材料[5]。

因TSV通常用高导热率材料制备,所以TSV除了用作互连线外,还可用作传热通道,提高三维集成电路的热可靠性。目前对TSV的研究,主要集中在其电气性能、寄生参数以及热力学方面。本文针对TSV的散热特性,提出了一种在大功率晶体管元胞块之间插入TSV散热网络的方案,研究在加入TSV前后以及改变TSV半径时三维集成电路温度变化的情况,利用COMSOL Multiphysics软件对其进行仿真。

1模型的选择

1.1三维集成电路结构模型

三维集成电路结构由N个有源层按照Face-to-Back方式键合,热流按照芯片的垂直方向传输。本研究采用两个有源层,并且不考虑封装,上层芯片上部连接SiO2键合层,下层芯片上部通过SiO2键合层与上层芯片键合,下部则通过SiO2键合层与热沉连接,结构如图1所示。两个有源层尺寸均为5 mm×5 mm,厚度均为0.2 mm[6],SiO2键合层厚度均为10 μm[7],选用铜作热沉材料,厚度为1 mm[8]。

图1 含有两层芯片的3D IC结构

不考虑封装的两个有源层三维集成电路的一维近似热传导模型如图2所示。

图2 热传导模型

图2中,Rglue_3,Rglue_2和Rglue_1分别表示顶层键合层、上下层芯片之间的键合层和下层芯片与热沉之间的键合层的热阻;Rsi_2和Rsi_1分别代表上下层芯片硅衬底的热阻;Rhs代表热沉的热阻。芯片产生的热量沿着垂直于芯片的方向传输,从热沉消散。

1.2VDMOS的结构

芯片由有源区和终端区组成,有源区是由结构相同的成千上万个元胞并联起来组成的区域,它是源器件存在的区域,决定着器件的开启与关闭;终端区的作用是减小局部电场与提高表面击穿电压,使器件实际击穿电压更加接近平行平面击穿电压[9-10]。本研究中设定芯片的功率器件均为VDMOS,VDMOS元胞则设定为方形元胞,尺寸为0.026 mm×0.026 mm,厚度为0.05 mm[11],功耗设定为14 W,元胞总数为2 300个,则单个元胞功耗为14/2 300≈0.006 W。

1.3TSV结构

TSV填充材料选用Cu,环绕TSV的绝缘层选用SiO2。TSV结构的纵向切面图和横向切面图如图3所示。

(a)TSV的纵向切面图 (b)TSV的横向切面图 图3 TSV结构图

2仿真方案选择

本研究的仿真方案分为3种,分别是在未加入TSV、加入TSV和改变TSV半径的情况下,截取大小相同且所处环境条件也相同的局部三维集成电路在COMSOL中进行仿真。

2.1未加TSV情况下局部芯片的仿真

2.1.1局部芯片结构

因TSV数目太多,全部仿真不仅会浪费资源,而且会发生因网格太密、网格数过多计算机无法计算的情况[12],故截取三维集成电路中非边缘部分中的0.9 mm×0.9 mm局部芯片来进行仿真,局部芯片的俯视图如图4所示。晶体管芯片中每一个元胞都是一个小的晶体管,我们把这些元胞看成元胞阵列,然后将多个单位元胞组成较大的元胞块进行分析[13]。本次仿真将5×5个单位元胞组成一个元胞块,设定元胞块间的间距为50 μm,则每个元胞块尺寸为130 μm×130 μm。

图4 局部芯片的俯视图

截取的0.9 mm×0.9 mm局部芯片具有代表性,可以作为芯片中非边缘部分的最小单元。图4中含有5×5个元胞块,每个元胞块又含有5×5个元胞,因此0.9 mm×0.9 mm最小单元局部芯片的功耗为0.006 W×25×25=3.75 W。

2.1.2仿真方程

使用COMSOL软件的传热模块进行仿真。热量传递分传导传热、对流传热和辐射传热3种方式。设定芯片内部散热为传导传热,外部散热为与空气对流传热,换热系数与风速有密切的关系,因此设定外部环境为无风状态,换热系数为5 W/m2K,对流传热设定在上层芯片上部键合层的上表面,环境温度设定为293.15 K,芯片初始值为293.15 K[14-15]。热沉下表面温度设定为313.15 K。其他边界设定为绝缘状态。

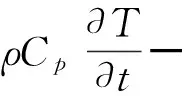

用热传导定律研究传热现象,同时考虑热对流过程,传热方程表示为

(1)

因系统在传热过程中与外界有热交换,故传热的边界条件方程为

(2)

式(2)中Text代表环境温度;h代表传热系数[16]。

2.1.3芯片组成材料及属性

芯片的组成材料为硅、铜和二氧化硅,其属性见表1[17]。

表1 芯片组成材料及其属性

2.1.4仿真结果

未加TSV时局部芯片的仿真温度如图5所示。

图5中最高温度为457 K,明显超出了芯片的最大可承受温度398.15 K[18],造成三维集成电路不能在安全的温度范围内工作。而且图5显示,三维集成电路内部的温度是从顶部的二氧化硅层到底部的铜层逐渐下降,说明底部铜层对整个三维集成电路起了强大的散热作用。

图5 未加TSV时局部芯片的仿真温度

2.2加入TSV情况下局部芯片的仿真

TSV选用铜材料,绝缘层选用二氧化硅,不考虑阻挡层。TSV半径为20 μm,二氧化硅层的宽度为1 μm[19]。加入TSV以后,局部芯片中TSV与元胞块的结构俯视图如图6所示。

图6 局部芯片中TSV与元胞块的结构

图6中TSV插入到相邻的四个元胞块之间[20],并且下层芯片中TSV内部的铜会生长到键合层内部,到达热沉为止,而上层TSV内部的铜会向上下各生长出10 μm,以此达到更好的散热效果。建模中在元胞块边缘处的每个TSV均为一半,在四个角处则为1/4,这样0.9 mm×0.9 mm单元局部芯片更加具有代表性。仿真得到局部芯片的温度如图7所示。

在图7中,可看到温度仍旧从上至下逐渐降低。因加入TSV以后,局部芯片的温度比不加TSV时小很多,最高温度为394 K,低于芯片可承受的最大温度398.15 K,局部芯片处在安全温度范围内,因此加入TSV可明显改善三维集成电路的传热问题。

图7 加入TSV情况下局部芯片的仿真温度

2.3改变TSV半径局部芯片温度的变化情况

依据2.2中的仿真方案,进一步改变TSV的半径,考察TSV半径的变化对三维集成电路温度的影响。TSV半径分别选取20 μm,25 μm,30 μm,组成三个组件,在同一个模型开发器中进行建模仿真。只改变TSV半径,其他条件不变。

改变TSV半径以后,局部芯片的仿真温度如图8所示。因TSV半径20 μm时的局部芯片仿真温度图上文已给出(见图7),故此处只给出TSV半径为25 μm和30 μm情况下的仿真温度图。

(a)TSV半径为25 μm

(b)TSV半径为30 μm图8 改变TSV半径后局部芯片仿真温度

由图8可以看出,TSV半径为25 μm时,局部芯片最高温度约为383 K;TSV半径为30 μm时,局部芯片最高温度约为376 K,结合TSV半径为20 μm时最高温度,可得出随着TSV半径的增大,三维集成电路温度不断降低,散热效果变得更好。

3对仿真结果的分析

3.1加入TSV前后三维集成电路的温度变化

为了更加清晰地看到三维集成电路温度的变化,对仿真图形进行后处理操作,由图5,图7可以看出顶层芯片的上表面温度最高,选取顶层芯片上表面的两点,点1(0,0,420 μm)和点2(900 μm,900 μm,420 μm),连接两点,作为三维截线,然后绘制这条线的温度曲线,结果如图9所示。

图9 顶层芯片上表面对角线的温度曲线

未加入TSV时,计算得出整个局部芯片结构中的最大温度为456.616 8 K;加入TSV以后,计算得出整个局部芯片结构中的最大温度为393.700 8 K。

3.2加入TSV后三维集成电路不同截线的温度对比

选取3条三维截线,分析位置分别为TSV内部、非TSV与非热源内部、热源内部,所选取的截线段均为竖直贯通整个三维集成电路,三维截线2的坐标为点1(180 μm,360 μm,-1 000 μm)和点2(180 μm,360 μm,430 μm),这条线段在一个TSV内部;三维截线3的坐标为点1(270 μm,360 μm,-1 000 μm)和点2(270 μm,360 μm,430 μm),这条线段在既非TSV内部也非热源内部的位置;三维截线4的坐标为点1(270 μm,270 μm,-1 000 μm)和点2(270 μm,270 μm,430 μm),这条线段在与三维截线2贯通的TSV相近位置处的热源内。此时增添一维绘图组,对这3条三维截线进行分析,温度曲线如图10所示。

图10 3条截线的温度曲线对比

图10中,三维截线2较另外两条曲线平滑,这是因为在TSV内部温度变化是渐变过程;三维截线3比三维截线4温度稍低,这是因为在热源内部温度要比热源外部温度高,而这两条曲线在弧度大于1 000 μm时比三维截线2温度要高,这是因为在热沉中,三者温度相同,而在热沉以外的其他地方的温度大都比TSV内部温度要高。在1 000 μm处和1 210 μm处,三维截线3和三维截线4出现急剧的攀升,这是由二氧化硅键合层的导热系数远低于硅的导热系数造成的结果。

3.3改变TSV半径后三维集成电路的温度变化

在3个组件中均选择同一个三维截线,坐标为点1(180 μm,180 μm,-1 000 μm)和点2(180 μm,180 μm,430 μm),此时三维截线穿过其中一个TSV的中心贯通整个三维集成电路,对此时的三维截线绘制一维绘图组,如图11所示。

图11 贯通三维集成电路的截线温度图

从图11可看到,在弧长0~1 000 μm时,3条温度曲线基本相同,这是因为此时的截线处在热沉内部,热沉强大的散热功能使不同半径的三维集成电路在热沉中温度基本相同。

为了更清晰地观察非典型区域的温度变化,对非TSV且非热源区域进行仿真分析(不仿真热沉部分)。选取三维截线的坐标为点1(270 μm,360 μm,0)和点2(270 μm,360 μm,430 μm),这条线段既没有穿过元胞块,也没有穿过TSV。仿真结果如图12所示。

图12 非TSV且非热源区域的仿真

从图12可以得出结论:随着TSV半径的增加,三维集成电路散热效果更好。

4结论

应用COMSOL Multiphysics有限元仿真软件对局部三维集成电路建模,该软件中的传热模块可以准确地仿真三维集成电路的传热过程。分别对未加入TSV、加入TSV和改变TSV半径三种情况下的局部三维集成电路进行仿真,结果表明,TSV插入到芯片内部元胞块之间可以有效将三维集成电路温度控制在一个安全范围之内,起到很好的散热效果,而且随着TSV半径的增大,三维集成电路散热效果更好。

参考文献:

[1]王凤娟,朱樟明,杨银堂,等.考虑硅通孔的三维集成电路最高层温度模型[J].计算物理,2014,29(4):580-583.

[2]张岩,董刚,杨银堂,等.考虑通孔横向热传输效应的三维集成电路热分析[J].计算物理,2013,30(5):753-758.

[3]王高峰,赵文生.三维集成电路中的关键技术问题综述[J].杭州电子科技大学学报,2014,34(2):1-7.

[4]黄琼琼,尚玉玲,张明,等.TSV的电磁-热-结构耦合分析研究[J].电子元件与材料,2015,34(4):74-78.

[5]王凤娟.基于硅通孔(TSV)的三维集成电路(3D IC)关键特性分析[D].西安:西安电子科技大学,2014.

[6]Lau J H, Yue T G. Thermal management of 3D IC integration with TSV(through siliconvia)[C]. Electronic Components and Technology Conference,San Diego, IEEE,2009:635-640.

[7]钱利波.基于硅通孔技术的三维集成电路设计与分析[D].西安:西安电子科技大学,2013.

[8]张雪粉.大功率LED散热研究及散热器设计[D].天津:天津大学,2007.

[9]张超.一种高可靠性的1200V IGBT的设计[D].成都:电子科技大学,2012.

[10]薛华虎.一种IGBT芯片的剖析[D].哈尔滨:哈尔滨工业大学,2009.

[11]马奎,杨发顺,林洁馨,等.一种DMOS漏极背面引出的BCD工艺[J].微电子学与计算机,2013,30(10):93-96.

[12]王宏明.应用于三维叠层封装的硅通孔(TSV)建模及传热和加载分析[D].西安:西安电子科技大学,2013.

[13]谢文华.基于FLOTHERM软件的双极功率晶体管热分布研究[D].成都:电子科技大学,2010.

[14]易建政,梁波.封套的光热环境与表面热流影响因素分析[J].河北工业科技,2008,25(6):346-352.

[15]Lu Tianjian, Jin Jianming. Thermal-aware high-frequency characterization of large-scale through-silicon-via structures[J].IEEE Transactions On Components, Packaging and Manufacturing Technology,2014,4(6):1015-1025.

[16]贺鸿鹏.基于COMSOL的OCT传感单元的多物理场研究与设计[D].保定:华北电力大学,2014.

[17]杜秀云.三维集成电路热问题的不确定性分析方法研究[D].大连:大连理工大学,2014.

[18]何成.典型封装芯片的热阻网络模型研究[D].西安:西安电子科技大学,2014.

[19]袁琰红,高立明,吴昊,等.硅通孔尺寸与材料对热应力的影响[J].半导体光电,2013,34(2):255-258.

[20]赵起越.1200V TRENCH-FS型IGBT的设计[D].成都:电子科技大学,2013.

(责任编校:李秀荣)

The COMSOL Model for Through-Silicon Via Thermal Characteristics of Three-Dimensional Integrated Circuit

ZHAO Peng,LIN Jie-xin,FU Xing-hua

(College of Big Data and Information Engineering, Guizhou University,Guiyang 550025, China)

Abstract:The COMSOL model for the 3D IC heat dissipation is established to simulate. The simulation results show that TSV network can effectively control the temperature of the 3D IC within a safe range, and when increasing the radius of TSV, three-dimensional integrated circuit may have a better cooling effect.

Key Words:three-dimensional integrated circuit; through-silicon via; cooling problem; the COMSOL model

基金项目:国家自然科学基金地区科学基金项目(61464002);贵州省科技合作项目(黔科合LH字[2015]7636)

作者简介:赵朋(1985-),男,河北安国人,硕士研究生,主要从事微电子科学与工程研究。

中图分类号:TN407

文献标志码:A

文章编号:1672-349X(2016)03-0041-06

DOI:10.16160/j.cnki.tsxyxb.2016.03.013