基于FPGA的电子密码锁设计

戴 彦

(唐山学院 智能与信息工程学院,河北 唐山 063020)

基于FPGA的电子密码锁设计

戴彦

(唐山学院 智能与信息工程学院,河北 唐山 063020)

摘要:基于FPGA设计的电子密码锁,运用EDA技术自顶向下的方法,采用硬件描述语言VHDL实现了密码锁的解锁、密码修改、报警提示及液晶显示功能。硬件测试结果表明,密码锁功能丰富、操作简单、安全性高、易于维护和升级。

关键词:密码锁;FPGA;VHDL;EDA技术

当前,传统机械锁的安全性能已经不能满足用户需求,电子密码锁由于其保密性好、安全系数高,受到广大用户的青睐[1]。

笔者基于FPGA设计的电子密码锁,用FPGA构造系统,所有算法完全由硬件电路来实现,使得系统的工作可靠性大为提高。由于FPGA具有现场可编程功能,当设计需要更改时,只需更改FPGA中的控制电路和接口电路,利用EDA工具将更新后的设计下载到FPGA中即可,无需更改外部电路的设计,大大提高了设计的效率,同时使电子密码锁具有更高的安全性和可靠性[2]。

1电子密码锁的系统设计

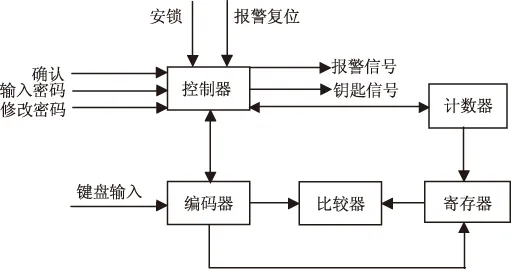

本系统设计主要包括硬件设计和软件设计两部分。基于QuartusII软件开发平台,使用VHDL语言,运用自顶向下的设计方法,根据整个系统性能的描述和要求,密码锁主控模块包含5个模块设计:控制器模块、计数器模块、寄存器模块、比较器模块、编码器模块。其结构框图如图1所示。

图1 电子密码锁结构框图

2电子密码锁的模块设计

2.1控制器模块设计

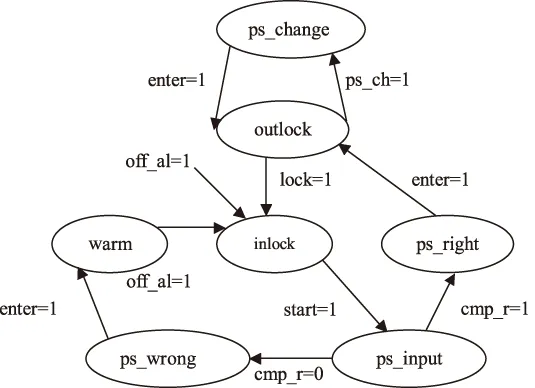

控制器模块采用有限状态机设计[3-5],将系统分为7个状态,即开锁状态(outlock)、安锁状态(inlock)、输入密码状态(ps_input)、密码初验正确状态(ps_right)、密码初验错误状态(ps_wrong)、报警状态(alarm)及修改密码状态(ps_change)。状态转换图如图2所示。

图2 控制器模块状态转换图

系统初始状态是安锁状态。当系统复位有效时,进入安锁状态。当系统处于开锁状态,输入ps_ch信号时,系统进入修改密码状态;若输入lock信号,进入安锁状态,锁闭合;在安锁状态,输入start信号,进入输入密码状态;在输入密码状态,由ps_i密码脉冲作为计数时钟,计数值输出作为寄存器地址,当计数器记到3时,返回计数满信号cin,如果密码内容和长度均正确,进入密码初验正确状态,如果密码错误,进入密码初验错误状态;在密码初验正确状态,输入确认信号enter时,进入开锁状态;在密码初验错误状态,输入确认信号enter时,进入报警状态;在报警状态,warn信号等于1,如果输入清除报警信号off_al,则进入安锁状态。

2.2计数器模块设计

本系统所设计的计数器是一个单向计数器,带有异步清零端和计数满指示端,模值为4。此模块作用有两个:计数值输出作为寄存器的地址输入;计数满指示送入控制模块,表示密码长度是否满足。

2.3寄存器模块设计

寄存器模块的功能是存储密码。寄存器模块中有4个寄存器,可存储4个BCD码形式的密码数据。如果要扩展密码的长度,先要增加寄存器的个数,此外,计数器模块的模值也要相应地增加。

2.4比较器模块设计

在数字密码中,比较器模块的功能是对编码器模块的输出和寄存器模块的输出进行比较,然后将比较的结果送入到控制器模块。比较的具体工作原理是:当比较结果相等时,cmp_r的输出为1;当比较结果不相等时,cmp_r的输出为0。

2.5编码器模块设计

在数字密码器中,有0-9共10个键,可以用10位二进制数表示,而寄存器中数据存储格式为BCD码,所以需要转换。编码器模块的主要功能是将10位二进制数编码为BCD码,然后将编码结果送入到比较器模块和寄存器模块。此外,编码器还需要将输入的跳变检测出来,将密码脉冲ps_i送入到控制模块。

3电子密码锁功能仿真与分析

3.1仿真波形

EDA仿真软件的使用可有效地验证系统功能,发现并纠正存在的错误,识别数据冲突等设计缺陷,从而帮助设计者完善设计方案,消除组合逻辑电路中的竞争和冒险,并优化系统速度[6-7]。

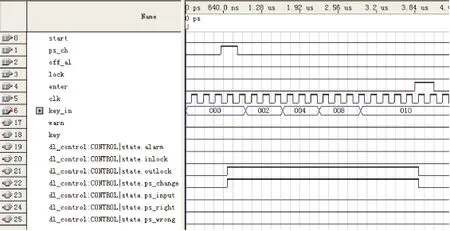

密码锁顶层模块修改密码状态仿真如图3所示。当按下“ps_ch”键,进入修改密码状态(ps_chang状态变为高电平),由“key_in”输入4位密码,按确认“enter”键。密码被修改,新密码即为刚输入的密码。

图3 密码修改功能仿真波形

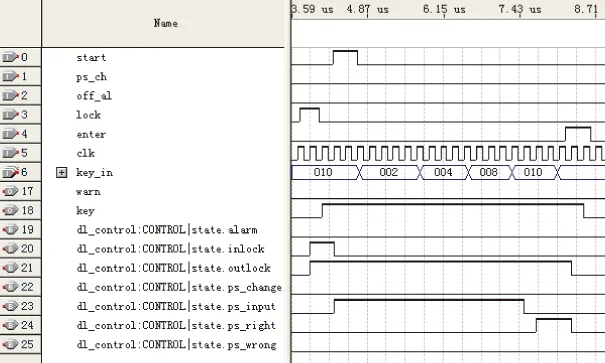

密码锁顶层模块报警状态仿真如图4所示。当按下“lock”键,进入上锁状态(inlock状态变为高电平,key变为高电平),按下“start”键进入输入密码状态(ps_input状态变为高电平),由“key_in”输入4位密码,输入的密码与锁的密码不相同,进入密码错误状态(ps_wrong变为高电平),按确认“enter”键,进入报警状态(alarm变为高电平)。

图4 报警功能仿真波形

密码锁顶层模块开锁状态仿真如图5所示。当按下“lock”键,进入上锁状态(inlock状态变为高电平,key变为高电平),按下“start”键进入输入密码状态(ps_input状态变为高电平),由“key_in”输入4位密码,输入的密码与锁的密码相同,进入密码正确状态(ps_right变为高电平),按确认“enter”键,进入开锁状态(outlock变为低电平,key由高电平变为低电平)。

图5 密码锁开锁仿真波形

3.2结果分析

通过仿真后,进行硬件测试。在闭锁时,若输入密码正确,密码锁打开,此时可以重置或修改密码;

若输入错误,显示密码错误信息,蜂鸣器报警,此时可以通过键盘按键来关闭警报,系统运行正常。硬件测试结果表明,密码锁达到设计要求,且为设计升级留下了空间。

4结论

本文基于FPGA的电子密码锁的设计方案和实现方法,可以实现密码锁4位密码的修改、重置、开锁、报警功能,满足日常生活的需要,且系统体积小,结构简单,安全性高,保密性强,成本低,便于维护和升级,有良好的应用前景。

参考文献:

[1]颉洪睿,孙丹丹,魏学军.基于CPLD的智能密码锁设计与实现[J].实验室研究与探索,2015,34(11):99-102.[2]杨彪,韩升,孙硕,等.基于FPGA的数字密码锁[J].电子技术与软件工程,2015(2):217-218.

[3]宋泽明,陈文楷.基于VHDL的有限状态机设计[J].北京工业大学学报,2005,31(1):21-24.

[4]单长虹.用VHDL设计有限状态机的方法.[J].电子技术应用,2001,27(7):11-13.

[5]董秀洁,杨艳,周游.FPGA/CPLD选型与设计优化[J].化工自动化及仪表,2009,36(3):60-63.

[6]秦磊华,王小兰.EDA仿真在组成原理设计性实验中的应用[J].实验室研究与探索,2009,28(4):79-82.

[7]董秀洁,杨艳,周游.FPGA/CPLD选型与设计优化[J].化工自动化仪表,2009,36(3):60-63.

(责任编校:夏玉玲)

The FPGA-Based Design of Electronic Combination Locks

DAI Yan

(College of Intelligence and Information Engineering, Tangshan University, Tangshan 063020, China)

Abstract:Based on FPGA, the author of this paper has designed a kind of digital combination lock with the top-down design EDA method and VHDL to unlock the combination lock,sett the password,warn failures and display with LCD. The results show that the combination lock has the advantages of rich functions, easy operation, high security, great reliability, and effortless maintenance and upgrade.

Key Words:password lock; FPGA; VHDL; EDA

中图分类号:TP271+.5

文献标志码:A

文章编号:1672-349X(2016)03-0038-03

DOI:10.16160/j.cnki.tsxyxb.2016.03.012

戴彦(1982-),女,河北唐山人,讲师,硕士,主要从事计算机控制研究。