VDMOS器件动态特性研究

郑 莹,姜立娟(中国电子科技集团公司第四十七研究所,沈阳 110032)

VDMOS器件动态特性研究

郑 莹,姜立娟

(中国电子科技集团公司第四十七研究所,沈阳110032)

摘 要:VDMOS器件具有开关速度快、开关损耗小、频率特性好等优点,被广泛应用于高频开关器件领域。利用TCAD软件对VDMOS器件进行建模仿真,研究了元胞P阱间氧化层厚度对器件静态参数和动态参数的影响。结果表明,器件的阈值电压不变,器件的导通电阻随着元胞P阱间氧化层厚度的增加而增加,器件的栅电荷随着元胞P阱间氧化层厚度的增加而减小,二者相互矛盾,但器件功耗优值明显提高。同时采取JFET注入技术降低导通电阻,使得器件的动态性能进一步改善,对高频VDMOS器件的应用具有一定的指导意义。

关键词:VDMOS器件;动态特性;氧化层;阈值电压;导通电阻;栅电荷

1 引 言

功率VDMOS具有开关速度高、频率特性好的优点,特别值得指出的是,它具有负温度系数,没有双极功率管的二次击穿问题,安全工作区大。因此,不论是开关应用还是线性应用,VDMOS都是理想的功率器件。尤其VDMOS作为开关器件提高了开关电源的工作频率,有效减小了电源的体积和重量。但是在高频下,VDMOS开关转换过程中的功率损耗是值得重视的问题。若开关时间不能满足要求,那么器件在开关过程中的功率损耗会严重影响开关电源的转换效率。因此,高频高效电源要求VDMOS有短的开关时间,在其他一些领域则要求VDMOS有高的截止频率。限制VDMOS开关时间和截止频率的主要因素是器件本征电容和寄生电容的充放电过程,尤其是器件元胞P阱间的栅漏电容对器件开关时间和截止频率有较大影响[1-3]。为此,研究者们先后采用了改变电极间介质层介电常数、减小电极面积、增加电极间介质层厚度等方法减小寄生栅漏电容[4-7],提高器件的动态性能。其中,增加电极间介质层厚度对器件动态特性的影响究竟有多大,还会对哪些器件参数产生明显改变,需要进一步定量研究才能确定,这对于分析该结构对器件动态性能改善的效果是至关重要的。

2 建模与仿真

TCAD软件提供了一个基于用户界面的模拟环境,可进行2D/3D工艺模拟、2D/3D器件模拟以及大型实验设计和统计学分析,在光电、CMOS、射频、存储等领域得到有效应用[8]。这里利用TCAD软件对VDMOS器件进行模拟仿真,如图1所示。在常规VDMOS器件结构基础上,增加器件元胞P阱间的氧化层厚度,由于增加了极板间介质层的厚度,减小了栅漏电容,从而降低了栅电荷。

图1 利用TCAD软件对VDMOS器件结构建模

3 模拟结果与讨论

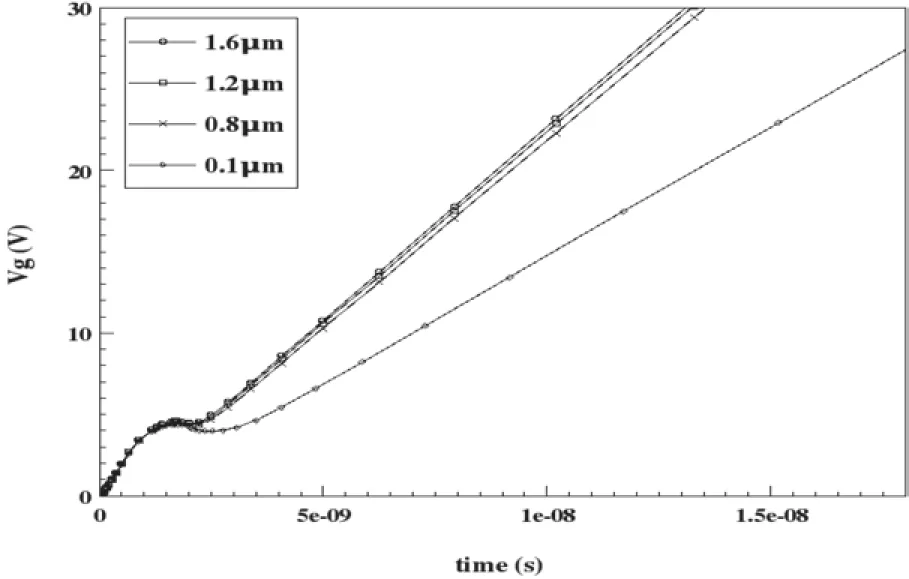

为了研究器件元胞P阱间氧化层厚度增加的多少对器件性能的影响,进行了如下四种结构参数的模拟,多晶硅宽度为6.75μm,沟道上方的栅氧化层厚度是不变量,按照P阱间氧化层厚度的多少分为四种情况,分别为0.1μm,0.8μm,1.2μm,1.6μm,其中,0.1μm对应常规VDMOS器件的栅氧厚度。

图2是VDMOS器件的ID-Vg转移特性曲线,可以看出四种结构的阈值电压曲线完全重合,这是显而易见的,这是因为模拟过程中所有结构沟道上方的栅氧化层并未发生改变。

图2 ID-Vg转移特性曲线

图3是VDMOS器件栅电荷随栅压Vg变化情况曲线,栅电荷的定义是在Vg=12V时所需的电荷值。显然地,增加器件元胞P阱间氧化层厚度能够减小栅电荷。然而,VDMOS器件导通电阻RON随着P阱间氧化层厚度的增加而增大,如表1所示,这是由于漂移区下积累层电流产生的电阻增大导致的。导通电阻的增大意味着增加了器件的导通损耗,降低栅电荷是降低关断损耗,两者是互相矛盾的,为了衡量器件的功率损耗,国际上采用优值函数FOM = RON×Qg来表征。

表1是四种结构的优值函数FOM值,可以看出,器件元胞P阱间氧化层厚度越大,VDMOS器件的功耗优值越小,与常规VDMOS器件相比,功耗优值减小了27.8%,如果再增加氧化层厚度,功耗优值减小的百分比将更大。

图3 VDMOS器件栅电荷随栅压Vg变化情况曲线

表1 优值函数值(FOM = RON×Qg)

4 改进措施

由模拟结果可知,导通电阻和栅电荷是两个矛盾的优化参数,在已增加器件P阱间氧化层厚度的基础上,通过JFET注入技术减小导通电阻。表2是在JFET注入后得到的优值函数FOM值。

表2 改进后的优值函数值(FOM = RON×Qg)

与表1相比,在器件P阱间氧化层厚度改变量一致的情况下,导通电阻减小,尽管栅电荷略有增大,但改进后的优值函数值FOM仍然低于常规VDMOS器件,且当氧化层厚度改变量较大时,JFET注入对器件导通电阻的影响更为显著,使得优值函数值FOM进一步提高。

5 结束语

对VDMOS器件元胞P阱间氧化层厚度对器件动态特性的改善情况进行了模拟仿真,结果表明,VDMOS器件的阈值电压没有发生变化,导通电阻和栅电荷会随着元胞P阱间氧化层厚度的增加而变化,功耗优值函数得到明显降低,改善了器件的动态性能。同时发现二者也是相互矛盾的,通过JFET注入技术,可以减小导通电阻,使得器件的功耗优值函数进一步改善,对于高频下VDMOS的应用具有一定的指导意义。

参考文献:

[1]B Jayant Baliga.Foudamentals of Power Semiconductor Device[M].Carolina:Power Semiconductor Research Center,North Carolina State University,2008.

[2]Tatsuo Sakai.A New VDMOSFET Structure with Reduced Reverse Transfer Capacirance[J].IEEE TRANSACTIONS ON ELECTRON DEVICES,1989,36(7):1381-1386.

[3]戴显英,张鹤鸣,李跃进,等.功率VDMOS开关特性与结构关系[J].西安电子科技大学学报,1998,25(1):98-101.DAI Xianying,ZHANG Heming,LI Yuejin,et al.Study of the relation between the switching performance and the structure of power VDMOS[J].Journal of Xidian University,1998,25(1):98-101.

[4]郭丽莎,夏洋.一种减少VDMOS寄生电容的新结构[J].现代电子技术,2009,20(307):200-202.GUO Lisha,XIA Yang.New VDMOS Structure with Reduced Parasitic Capacitance[J].Modern Electronics Technique,2009,20(307):200-202.

[5]Jacky C.W.Ng.A Novel Planar Power MOSFET With Laterally Uniform Body and Ion-Implanted JFET Region [J].IEEE ELECTRON DEVICE LETTER,2008,29(4):375-377.

[6]Ueda D,Tskgi H,Kano G.A New Vertical Double Diffused MOSFET-The Self-Aligned Terraced-Gate MOSFET[J].IEEE Trans Electron Device,1984,ED-31 (4):416-420.

[7]宋文斌,蔡小五.多晶硅部分剥离技术对抗辐照VDMOS动态特性的研究[J].电子世界,2012(2):20-22.SONG Wenbin,CAI Xiaowu.The Affect of Polysilicon lift-off Technic on Dynamic Performance of Anti-radiation VDMOS[J].Electronics World,2012(2):20-22.

[8]郑守国.高压VDMOS的设计与工艺仿真[D].哈尔滨:哈尔滨工业大学,2010.ZHENG Shouguo.Design and process simulation on high voltage VDMOS[D].Harbin:Harbin Institute of Technology,2010.

Study on Dynamic Performance of VDMOS Device

Zheng Ying,Jiang Lijuan

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

Abstract:The VDMOS device has advantages of high switching speed,small switching loss and high working frequency,etc.,which is widely applied in high frequency switching devices.In this paper,VDMOS device is simulated by TCAD software and the effect on static and dynamic parameters of oxide thickness between P well in VDMOS cell is studied.The results show that threshold voltage is constant and on-state resistance changes with oxide thickness and Gate electric charge of VDMOS is being in diametrical opposition,but the figure of merit is obviously increased.At the same time,JFET technology is used to reduce on-state resistance to improve dynamic performance of VDMOS device which can perform guidance for high frequency VDMOS device.

Key words:VDMOS device;Dynamic performance;Oxide layer;Threshold voltage;On-state resistance;Gate electric charge

DOI:10.3969/j.issn.1002-2279.2016.02.005

中图分类号:TN4

文献标识码:A

文章编号:1002-2279(2016)02-0014-03

作者简介:郑莹(1986-),女,吉林省公主岭市人,博士,工程师,主研方向:半导体分立器件。

收稿日期:2015-09-17