一种低信噪比跟踪接收机技术研究

杜要锋

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

一种低信噪比跟踪接收机技术研究

杜要锋

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

天线口径较小时,接收到卫星信标信号的信噪比较低,跟踪余量较小。为满足小口径动中通天线的跟踪需求,研究了一种适用于低信噪比条件下的跟踪接收机。介绍了其工作原理,并对算法进行了MATLAB仿真,最后进行了FPGA实现。

低信噪比;动中通天线;MATLAB仿真;FPGA实现

0 引言

跟踪接收机是卫星通信移动地球站的一个重要组成部分。它接收来自卫星的信标信号或通信信号,接收到的信号经下变频、放大和解调后向伺服系统提供所需的角误差电压,控制天线的俯仰轴和方位轴向角误差减小的方向移动,从而实现对卫星目标的自跟踪。传统的动中通天线所用的跟踪接收机解调门限相对较高,当天线接收口径较小时,接收到的信号相对较弱,天线可能无法实时跟踪,在应用到小型化动中通天线上时比较困难。所以,为满足小口径天线的跟踪需求,研究低信噪比下的跟踪接收机技术很有必要。

1 传统单载波跟踪接收机工作原理

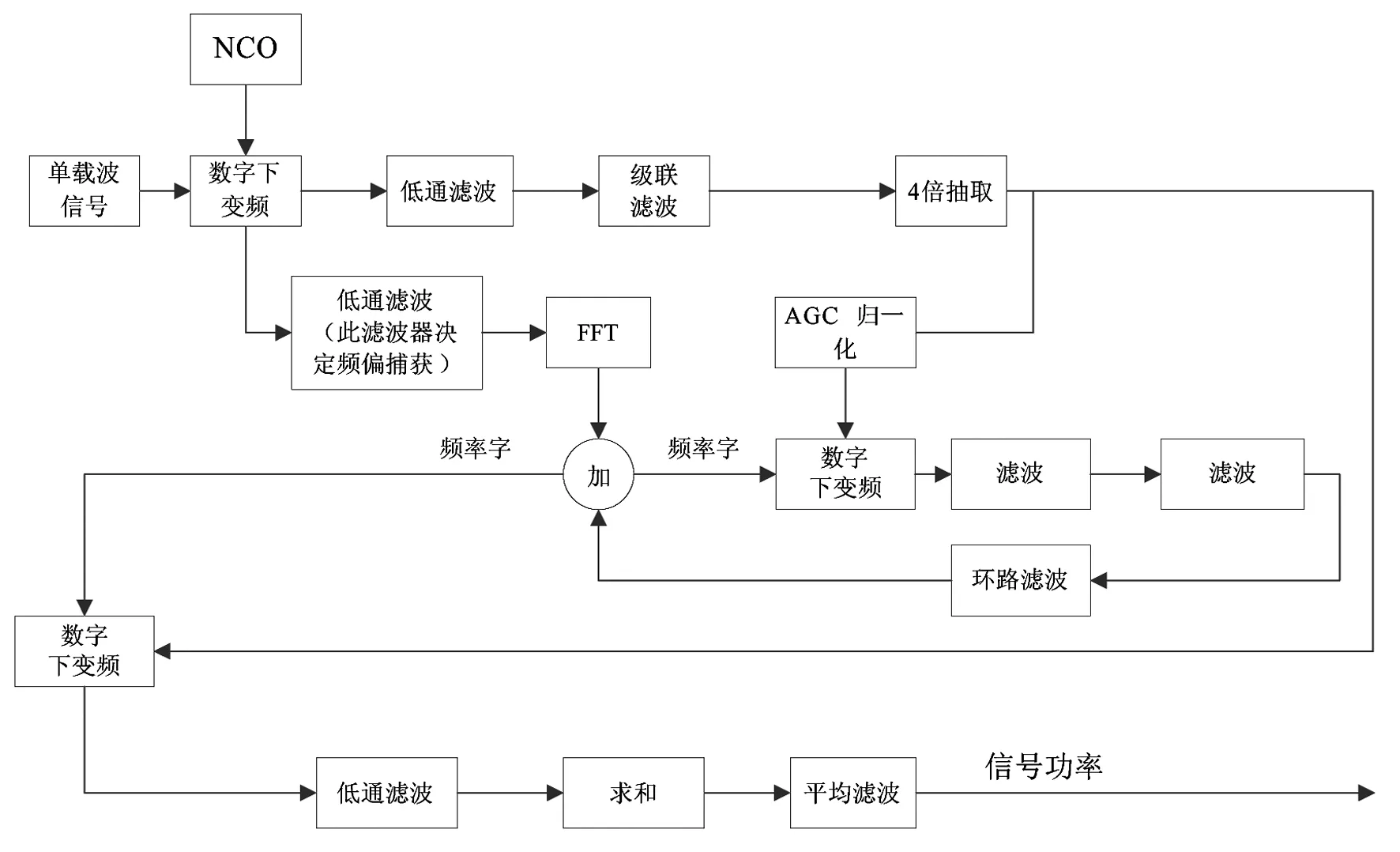

如图1所示,为传统单载波信号解算仿真框图。单载波信号解调的理论推导过程如下:

图1 传统单载波跟踪接收机工作原理

输入为70MHz的中频信号,设采样频率为fs,经过采样并低通滤波之后的信号频率为fc,信号的表达式可以表示为

S=Asin[2πfcn+φ(n)]+N(n)=Asin[(ωc+Δω)n]+N(n)

第一级下变频NCO产生本振信号为cos(ωcn)和sin(ωcn),与输入信号相乘,可得I路和Q路信号分别为

两路信号经过低通滤波之后,滤除混频产生的二倍频分量,可得

I′(n)=A′sin(Δωn)=A′sin(ω0+Δω′n)

Q′(n)=A′cos(Δωn)=A′cos(ω0+Δω′n)

式中,设ω0为锁频环路出来的频率字,进入NCO产生本振信号为cos(ω0n)和sin(ω0n),与I′(n)和Q′(n)相乘进行混频,得

[I′(n)+Q′(n)][cos(ω0n)+jsin(ω0n)]=A′[cos(Δω′n)+jsin(Δω′n)]

再经过低通滤波,进入鉴频器进行大频偏捕获,鉴频器的输出为

可见鉴频器的输出为常数,1代表一个采样点。这样鉴频器的输出经过环路滤波器滤除其中的高频分量及噪声来进行大频偏捕获,之后再经过更窄的锁相环进行相位跟踪,从而能不断的校正锁相环路NCO的振荡频率和相位,使NCO的输出信号能实时的跟踪输入载波。实际FPGA实现时,可用高精度的FFT代替锁频环进行大频偏捕获,实现比较简单。

2 低信噪比下单载波跟踪接收机设计框图

低信噪比下单载波跟踪接收机仿真设计原理如图2所示。70MHz单载波信号首先通过AD采样,采样后的信号与NCO产生的信号进行数字混频,经过低通滤波滤去2倍频分量,分为两路,一路经多级抽取进行降采样滤波,另一路经FFT变换进行频偏捕获计算,计算出来的频率字与第一路经抽取的信号进行混频,混频后的信号经低通滤波后,再进行2倍降采样处理缩小带宽,经AGC归一化后进入锁相环。由于前面进行了大量的信号抽取滤波处理,采用逐级级联滤波器,降低旁瓣,环路带宽大大降低。

图2 低信噪比单载波信号解算框图

单载波信号可用下列公式表示:

S(n)=Acos[(ωc+Δω)n]+N(n)

经第一级下变频之后,去除载波分量,同乘e-jωcn,这样经过第一级下变频之后信号的实部和虚部分别为:

数字变频之后,经低通滤波,滤除二倍频分量之后

与之前传统单载波模式不同的是,低通滤波之后的信号再经过四级2倍抽取信号之后,也就是采样速率降低16倍,滤波器带宽也相应地降低。级联抽取滤波之后的信号可以用下式来表示:

进行大频偏计算时用FFT实现,计算出相应的频率字。与上述信号进行混频之后,再经过2倍抽取,较锁相环之前采样速率降低了16倍。级联滤波之后进入锁相环进行载波相位同步。相对传统的单载波模式,环路带宽缩小8倍。传统模式由于前端滤波器较宽和锁相环带宽较宽,解调门限相对较高。

3 低信噪比下MATLAB仿真

根据上述设计原理对算法进行MATLAB仿真设计验证。仿真过程中,构造低信噪比信号为

s(t)=cos[2π(fc+Δf)t]+N(t)

式中,设信号幅度为1,fc为载波频率,Δf为频偏,N(t)为高斯白噪声。

模拟信号载噪比C/N0为35dB,仿真时间为100ms,采样频率为fs/32,采样点数为3039个点。如图3所示仿真结果,信号载噪比C/N0=35dB,频偏为1kHz情况下,锁相环锁定时间在50ms左右。图4为锁定后,仿真计算的信号幅度和载噪比。仿真结果证明了算法的正确性。

图3 锁定状态与频偏收敛曲线 图4 幅度与载噪比收敛曲线

4 算法的FPGA实现

对算法的MATLAB仿真验证后,开始在硬件平台上编写程序并进行算法在线仿真实现,主要处理器采用FPGA芯片XC5VSX95T。最后,通过采集信号源与噪声源构造出的模拟信号进行在线仿真验证。

构造信号的信噪比分别为40dB/Hz和35dB/Hz,设定信号源的频率有一定的频偏。图5和图6给出了频率为70.04MHz时用ChioScope Pro在线仿真工具调试锁相环的一组结果。由图中可以出,锁相环在信噪比分别为40dB/Hz和35dB/Hz时都能收敛稳定。图中FreData_pll锁相环环路稳定收敛后的频率字,amp_s表示环路稳定后计算的相应信号功率,QDout1_pll_out为环路稳定并经过数字下变频后的Q路信号,用于锁定检测判断。实际工程应用时,随着信噪比的降低,锁频带宽相应降低,须折衷考虑实现精度与硬件资源。

图5 载噪比为40dB/Hz时FPGA实现结果,频率70.04MHz

图6 载噪比为35dB/Hz时FPGA实现结果,频率70.040MHz

5 结束语

跟踪接收机作为天线伺服系统不可或缺的重要组成部分,和伺服环路息息相关,决定着跟踪系统的跟踪精度、跟踪带宽等重要指标。本文提出了一种低信噪比解调的跟踪接收机技术,通过前级降采样并降低环路滤波器带宽,可以降低信号的解调门限,最后进行了算法的FPGA实现。在小型化动中通天线中具有较高的工程应用价值。

[1] 韩孟飞,王永庆,吴嗣亮,等. 极低信噪比高动态信号的载波跟踪锁频环鉴别器[J].北京理工大学学报,2009,29(3): 245-249.

[2] 陈永东. 基于FPGA 的数字锁相环的设计[J].电子技术应用,2007,28(5): 49-52.

Research on a low SNR tracking receiver technology

DU Yao-feng

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

When the antenna diameter is small, the carrier-to-noise of receive satellite beacon signal is low, and the tracking margin is small. In order to meet the tracking requirements of small aperture antennas of “Sat-com on the Move”, a tracking receiver technology for low SNR conditions is studied. The working principle of the algorithm is introduced, and the MATLAB simulation and FPGA implementation is carried out.

Low SNR; Sat-com on the Move; MATLAB simulation; FPGA implementation

2016-11-15

杜要锋(1984-),男,工程师,主要研究方向:信号与信息处理.

1001-9383(2016)04-0047-06

TN911.7

A