集成电路版图设计技巧

苏州工业园区职业技术学院 孙丽莉 史小波

集成电路版图设计技巧

苏州工业园区职业技术学院 孙丽莉 史小波

【摘要】笔者根据多年在设计公司的从业经历,总结出了在集成电路版图设计工作中提高工作效率和符合团队合作的一些经验。建立良好的设计习惯和工作风格可以提高版图设计员工作效率,避免一些不必要的修改,还可以很大程度上保证电路设计性能的实现提高产品良率,缩短出货周期。

【关键词】版图设计;规范命名;优化跳线;合理走线;操作习惯

集成电路版图设计是把设计变成现实的桥梁,它是半导体产业中的重要一环。建立良好的设计习惯和工作风格不仅可以让版图设计员工作效率提高,避免一些不必要的修改,而且还可以很大程度上保证电路设计性能的实现提高产品良率,缩短出货周期。

一个优秀的版图设计工程师不仅要具有扎实的专业基础知识积累设计技巧,还要具备良好的设计习惯。规范的工作习惯不仅可以在团队合作中无障碍沟通,也能更多地节省不必要的电路验证时纠错修改的时间。鉴于多年在设计公司从业经验,总结出在设计工作中要在如下几方面要建立规范和形成习惯。

1 规范Cell命名

一般来说电路中Cell叫什么名字,相应的Layout中命名也叫该名字,但需要用大小写来区分电路图和版图,这似乎没什么疑问。但有时Layout也需要做一些自己的Cell,这时取名字应当有意义,方便看到名字就大概知道可能是什么,而不是随意起名叫“AAA”、“123”这样的名字。比如把“DECODE”中的走线做成一个Cell,如果叫“A”就是一个错误的范例,因为它容易混淆而与另一个缺乏条理的合作者冲突,但是此时用“DECODE_ROUTE”命名此cell,则是一个合格的名字。

实际上这是一条可以推广的规范,Layout Library、GDS等等一切文件、目录的名字都不要随意。具有一定意义和识别度比较高的命名习惯,会让工作变得顺利,团队合作中也会减少不必要的麻烦。

2 相似单元做成Cell

简单来说,就是相同的版图内容不要画两遍。比如图中的电路,其中几块长得一样,大概没有人会把它画8遍,但是有人会先画一份,然后把画好的那份再复制7遍,这看似是一个很好的办法。问题关键在于画好的那一份是否一定没有任何问题,不需要再有任何修改。要知道一个小改动,你都要把所用时间乘8。所以合理的做法是把相同内容做成Cell再调用,这样要有任何修改,改一次就可以了。所以要学会灵活运用“调用”的功能,可以在设计中事半功倍。

3 勤做标识

一般工艺里都会有用来打标识的Layer,它不会出Mask,也不参与DRC、LVS检查,单纯为了做记号,如0.6µm Singal Poly Double Metal Mixed Signal Technology中M1TEXT和M2TEXT就是单纯用来打标识的层次不会出Mask也不会在DRC或LVS检查中被识别。所以在Layout设计过程中除了电路图中的power线、输入/输出信号线等必须打字外,器件的名字、关键节点的名字,都应该要用标识层打字。这样做一方面可以方便其他人看图,另一方面如果过了一段时间需要改图,也方便查找。

4 避免小折角

细碎而不规则的多边形除了在审美层面上的恶劣以外,也具有现实意义的坏处。由于过多折角而形成的复杂多边形,会大大增加后期物理验证、寄生提取以及OPC的时间。所以在不影响面积的情况下,尽量避免不必要的小折角。

同样出于为后期各种图形处理效率考虑, 把一堆交错的图形Merge成一个除了视觉上的清爽,实际并无好处,所以让它们留在那里就好。

5 统一走线方向

要相信在Layout设计中无论多么繁冗庞杂的连线都一定能绕出来。为了保证这点,走线需要遵守一定规范:同层Metal线要保持相同走线方向,相邻层Metal走线方向相互垂直。具体说来就是如果Metal3用作垂直方向连线,那么Metal2、Metal4就应该是水平方向走线,而Metal3不能画水平方向线且Metal2、Metal4不能画竖直方向的线。这样做就能保证Layout中无论多复杂的布线都能绕通。

反过来,如果不事先计划布线方向,而是先用完一层Metal的布线资源,再用上一层Metal,或者干脆随心情而定,你会发现贪图局部的方便将引起一系列后续问题。并且可用的Metal层数越少,连线规模越大,这个问题就越明显。

6 别用Poly走线

Poly的方块电阻阻值要比Metal大很多,在集成电路电路设计中通常要关注信号传输的速度问题,在评估驱动能力与速度时一般是以金属走线来进行评估。如果在版图设计中过多的使用poly走线替代Metal,可能会导致最后生产出来的芯片性能不达标,所以除非万般无奈,Poly都不应该是走线的选择。

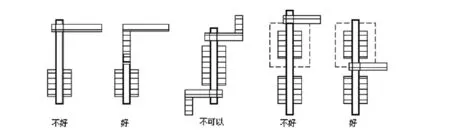

图1 poly的使用

7 避免短跳线

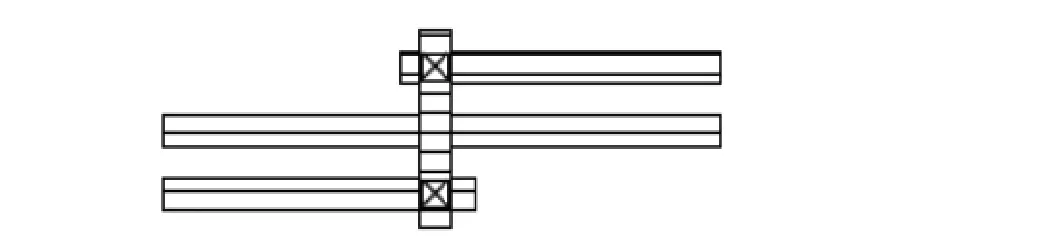

与Metal相比,Via的电阻值较大,允许的电流密度小,所以版图设计中的跳线要能少就少。历史经验告诉我们,像图2中这样的短跳线都是可以通过合理走线布局避免掉的。具体怎么才算合理走线?究竟如何绕线才能避掉这样的跳线?这些需要根据实际情况进行判断以及根据经验的积累。总之,原则就是能不跳线就不跳。

图2 跳线

8 避免重复走长线

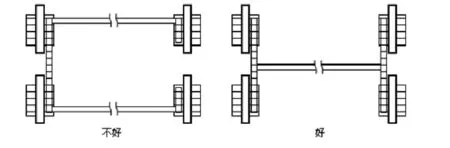

不论是Chip还是模块一个不留神就会出现重复走线的情况发生。重复走线除了浪费布线通道以外,增加信号线的长度也意味会有更大的寄生电容,对上一级的信号驱动能力将是一种考验。图3就是一种典型的重复走线的情况,虽然是看起来很直观的,但如果画完以后不回头检查一下却也很容易疏漏。

图3 走线

9 优化Contact、Via数量

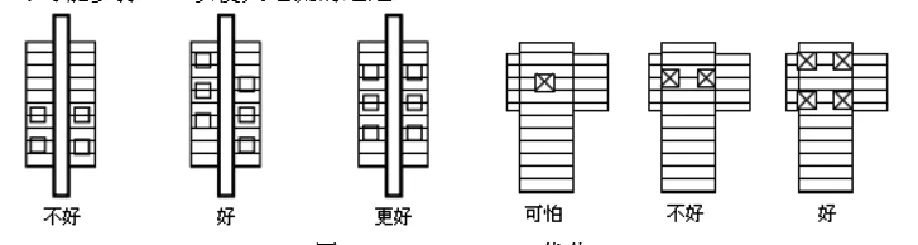

16nm以上工艺的非Standard Cell项目里,Double Contact、Via是标准配置,这样做可以减小电阻并提高连接可靠性,而面积代价很小。

如图4所示,这里列举了几种打Contact和Via的情况。打满Source和Drain端的Contact个数,可以减小MOS导通电阻提高速度。宽线连接处的Via连接一定要充足,尤其是宽线往往要传输较大电流,Via过少会影响电路可靠性,因此尽可能多打Via以便大电流的通过。

图4 Contact、Via优化

10 注意大尺寸MOS连线

对于Width特别大的MOS,首先不要画成很长一根,这样Foundry厂制作效果和器件工作速度都不佳。遇到这种情况时,应当考虑打折成多Finger MOS。打折以后还要特别注意Source、Drain的连接。因为Width大的MOS往往工作电流也大,所以连线汇总的地方一定要宽一些。

11 培养高效操作习惯

优秀的版图工程师在日常工作中会注意积累前面所提到的设计技巧外,还会注重培养高效的操作习惯。高效的操作习惯不仅可以提高绘图速度还能使工作变得轻松。

培养高效的操作习惯,首先要了解你的工具。EDA厂商希望他们不断更新功能的版图工具能最大程度上帮助工程师提高效率,让你认为自己的选择物有所值。工欲善其事必先利其器,花一些时间熟悉所用工具的每个命令、每条选项、每项设定是非常用价值的。

其次发掘不常用命令。每个人都会有自己的操作习惯,因而也会有一些明明知道用了会更有效率但就是不喜欢用的命令,像Yank、Align、Replace这样学习曲线稍长的或者Layer Tap、Size这样有点生僻的命令,合理使用都可以提高效率。

重要的是熟悉快捷键。这就不多解释了,没有哪个layout工程师是通过窗口菜单和按钮来工作的。总之为了更高的效率,有快捷键的操作都别用鼠标点。合理的快捷设置,可以减少手指和手腕的动作。

版图设计作为半导体产业中重要一环,不同的版图工程师设计的图纸会有差异,它的设计好坏直接影响到产品的良率和出货周期。所以要想成为一名优秀的版图设计师,经验的积累和高效的工作习惯培养必不可少。

参考文献

[1]Christopher Saint,Judy Saint.IC Layout Basic﹕A Practical Guide(影印版),北京,清华大学出版社,2004.

作者简介:

孙丽莉(1976—),女,辽宁抚顺人,硕士,苏州工业园区职业技术学院电子系讲师。