多级CIC滤波器的FPGA实现

谢海霞,孙志雄

(海南热带海洋学院 电子通信工程学院,海南 三亚 572022)

多级CIC滤波器的FPGA实现

谢海霞,孙志雄

(海南热带海洋学院 电子通信工程学院,海南 三亚 572022)

CIC滤波器是一种高效的滤波器,广泛应用于软件无线电的数字上下变频端。介绍了CIC抽取滤波器基本原理及其滤波器的Hogenauer结构。用Verilog HDL语言编写程序,实现该滤波器,通过MATLAB和Modelsim联合仿真,综合验证了设计的正确性和可行性。

CIC;Hogenauer结构;MATLAB;Modelsim

当前,数字下变频技术是软件无线电的核心技术部分,它在移动通信、数字广播、电视等领域具有非常重要的实际价值。但同时也存在着弊端,随着采样速率的提高,采样后的数据流的速率变得很高,会导致后续的信号处理速度跟不上,因此有必要对A/D后的数据流进行降速处理。显然这需要很大的抽取因子,如果用单级FIR滤波器实现,对滤波器的级数要求很高,在实际应用中会产生不良后果:硬件成本太高以及对数据处理速度要求增大导致性能大大下降。因此如何采用结构简单、处理高效的低通滤波器来满足工程实现的具体要求,就是抽取能否实现的关键所在。CIC滤波器结构简单,没有乘法器,只有加法器、积分器和寄存器,性能较好,已经被证明是在高速抽取或插值系统中非常有效的高分解速率滤波器[1-4]。文中在研究CIC抽取滤波器理论的基础上,给定滤波器参数并在FPGA上实现2级5倍抽取的CIC滤波器,利用MATLAB和Modelsim软件相结合进行联调仿真,并且验证了设计的可行性。

1 CIC抽取滤波器理论

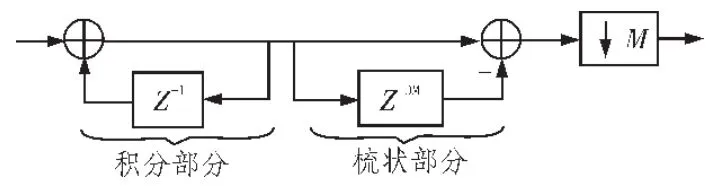

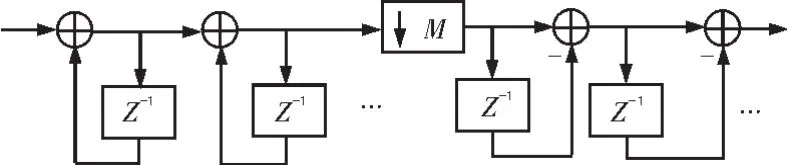

所谓抽取是指将采样率降低的转换。图1为单级CIC抽取滤波器框图。其包括两个基本组成部分:积分部分和梳状部分[5-7]。单级CIC抽取滤波器的冲激响应具有如下的形式:

其中,M为大于1的整数,称为抽取因子。D为为微分延迟,一般取1或2。它的z域表示形式为:

若滤波器的输入序列为x(n),输出序列为y(n),则y(n)是把x(n)每隔DM-1个取一个形成的。

图1 单级CIC抽取滤波器框图

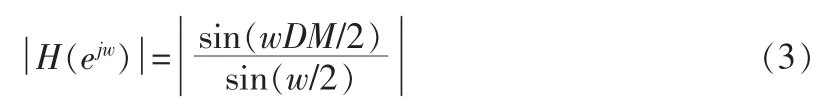

其传输函数的频率响应为[8-9]:

CIC抽取滤波器的幅频特性如图2所示。

图2 单级CIC抽取滤波器的频谱图

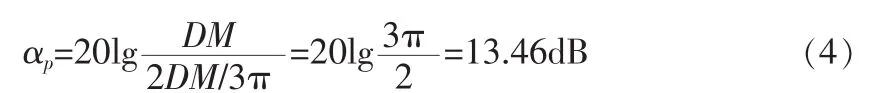

其中[0,2π/DM]为其主瓣,其它的区间为旁瓣。由图可见,随着频率的增大,旁瓣电平不断减小,当 DM>>1时,第一旁瓣的电平为 2DM/3π,则它与主瓣电平的差值为:

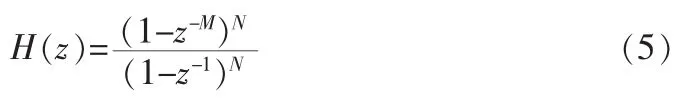

从公式(4)计算可得出单级CIC抽取滤波器的旁瓣抑制与DM无关,旁瓣电平较大,阻带衰减较差。在抽取滤波中频率混叠现象就较为严重,为降低旁瓣电平,可以采用多级CIC滤波器级联的办法来实现。在下面的分析中,D取1。假设有N个单级CIC滤波器级联,其传递函数为:

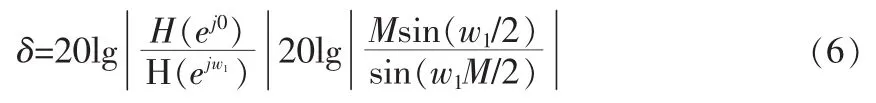

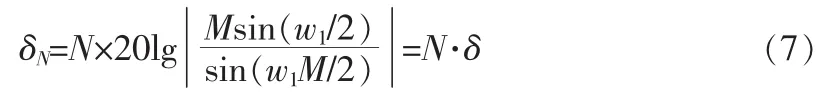

其第一旁瓣抑制为13.46×N(dB),虽然增大级数N可以增大阻带衰减,减小混叠的影响,但并不是N越大越好,还要考虑滤波器的通带内的衰减问题,也就是说在信号通带内信号的幅值容差不能太大。在通带w=w1处,若设容差为δ,则单级CIC滤波器的容差为:

则N级CIC滤波器的带内容差为:

由此可以看出,N级 CIC滤波器的带内容差也是单级的N倍。也就是说, 多级级联虽然能够增大阻带衰减,但是同时也会导致带内平坦度变差。所以CIC滤波器的级数是有限制的,一般而言以5级为限[10-12]。

图3为多级CIC滤波器的原始结构,图4为经过Noble变换后的Hogenauer结构。

图3 多级CIC滤波器的原始结构图

以上的两个图比较可以知道:经过 Noble变换后的Hogenauer结构把CIC滤波器用于多抽样率信号滤波时,积分部分始终在高数据速率端,梳状部分置低数据速率端,而抽取位于它们中间,最容易实现且占用的资源也最少,大大提高抽取滤波运算的效率。

图4 多级CIC滤波器的Hogenauer结构图

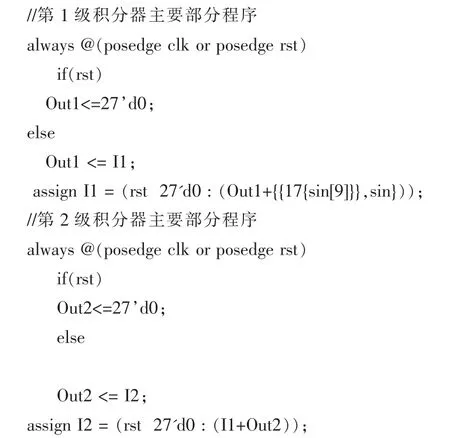

2 多级CIC滤波器的FPGA实现

设实现一个5阶2级CIC抽取滤波器,实现M=5倍下采样抽取。信号采样频率为200 kHz,FPGA的系统时钟为200 kHz,输入数据为8 bit,输出数据为16 bit。根据Hogenauer结构图,将Verilog HDL程序分成3个模块来写,积分模块、抽取模块以及梳状模块。

2.1 积分器的FPGA实现

每一级积分器只需要一个寄存器及一级加法运算可实现。对于一个10位输入的5阶CIC滤波器,为了保证运行时中间不会产生溢出,需要的内部字长为W=Bin+Bgrow=10+5log2(5×2)=10+17=27位。下面是采用Verilog HDL代码编写积分模块的程序。

2.2 抽取器的FPGA实现

实现抽取器的最简单的一种方法是从输入序列中每5个采样点抽取一个,重新组成一个新的输出序列。因此只需要根据计数器对输入数据每5个抽取一个输出即可。

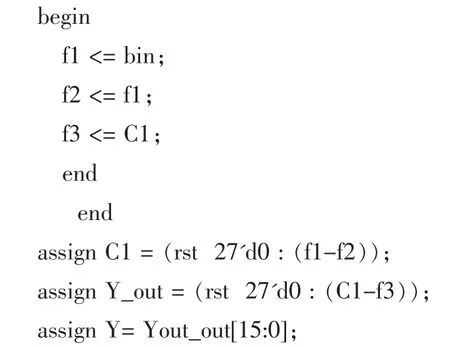

2.3 梳状器的FPGA实现

梳状部分只需要3个寄存器和2个减法器即可实现 。

3 多级CIC滤波器的仿真

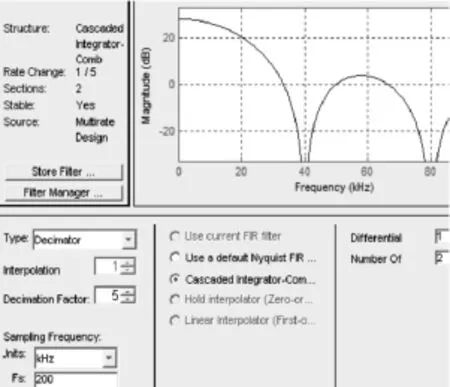

编写完滤波器实现程序后,编译成功后,即可进行FPGA仿真。首先打开MATLAB中的滤波器设计工具箱FDATool界面[13-14],按照要求填写好参数好,出现下面的200 kHz采样频率,5倍抽取,2级CIC滤波器的频谱图。

图5 FDATool设计抽取滤波器的界面

由图5可见,主瓣宽度是40 kHz,通带只有20 kHz。这说明该抽取滤波器只能允许20 kHz以下的信号通过,并且数据速率降低1/5倍。

MATLAB进行仿真,产生FPGA程序中需要使用到1 kHz和50 kHz两个正弦波叠加采样数据,生成的In.txt文件存放在仿真目录下,供FPGA程序使用,同时用于验证整个FPGA电路的工作过程及输出结果是否满足要求。

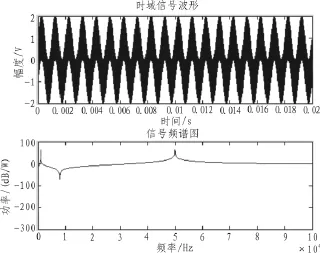

图6是1 kHz和50 kHz两个正弦波采样数据叠加的时域图和频谱图。

图6 1 kHz和50 kHz叠加的时域和频谱图

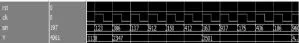

为了更好地测试滤波前后的信号波形变化,编写测试激励文件,用Modelsim进行仿真,读取In.txt文件输入测试激励信号,文件中将输出仿真结果数据写入外部的文本文件Out. txt,以方便使用MATLAB软件读取数据,并进一步分析仿真结果。从Modelsim的仿真波形界面图中可以看出1 kHz和50 kHz两个正弦波数据叠加信号经过200 kHz采样后经过2级5阶CIC抽取滤波器后,Y为每5个时钟输出一个数据,数据速率是输入数据速率的1/5倍,实现了5倍下采样。

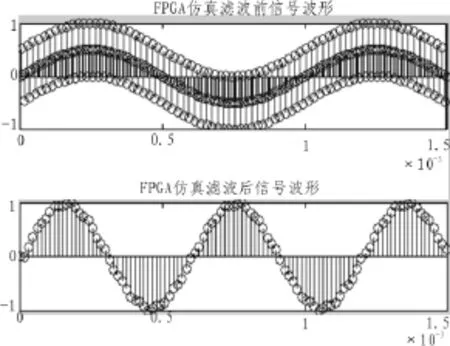

为了更直观地观看仿真结果,图 8是将 Out.txt导入MATLAB环境进行分析的波形图。

图7 Modelsim仿真波形图

图8 FPGA实现CIC滤波器的仿真波形图

从图8可以看出,FPGA仿真滤波前的信号波形图是由1 kHz和50 kHz两个正弦波数据叠加的信号,经2级5阶CIC抽取滤波后,形成FPGA仿真滤波后的信号波形图,抽取滤波后,50 kHz频率信号被滤除去,保留频率为1 kHz的正弦波信号,且数据速率降为40 kHz,仿真结果与期望结果一致,证明设计是正确性的和可行性的。

4 结束语

CIC抽取滤波器主要是完成降速处理,和传统滤波器的结构中相比,CIC滤波器设计不需要乘法运算,而乘法累加器是非常耗费系统资源的,尤其是当在进行处理信号频率比较高的时候,需要得到信号的实时处理的效果时,只能在不需要太多乘法累加器特殊结构的滤波器中来进行选择,恰好CIC滤波器刚好符合这个标准。设计多级 CIC滤波器的时候,经过Noble变换后的Hogenauer结构,在高速率状态下进行积分,在低速率状态下进行梳状滤波,因而降低了中间存储,资源占用最少,因此很适合采用FPGA和专用ASIC来实现。文中介绍的多级CIC抽取滤波器的实现、验证方法都是可行的,而且在实际使用的时候,人们可以根据应用不同的场所在程序里可以很方便地改变滤波器的参数,以简便的操作来达到降低系统的计算复杂性的功能!设计不仅对抽取滤波系统适用,而且对内插系统实现也有一定的参考作用[15]。本文所介绍的设计、验证的方法都是可行的,具有很高的应用价值。

[1]姜岩峰,张东,于明.数字接收机中的CIC滤波器的设计[J].电子测量与仪器学报,2011,25(8):671-675.

[2]雷能芳.基于FPGA的CIC抽取滤波器设计与实现[J].计算机与数字工程,2012,40(1):137-139.

[3]Losada R A,Lylons R.Reducing CIC filter complexity[J].

IEEE Signal Processing Magazine,2006(23):124-126.

[4]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[5]田耘,徐文波,张延伟.无线通信FPGA设计[M].北京:电子工业出版社,2006.

[6]杨小牛,邹少丞,楼才义.软件无线电原理与应用[M].北京:电子工业出版社,2004.

[7]纽习忻,杨义先.软件无线电技术与应用[M].北京:邮电大学出版社,2000.

[8]宗孔德.多抽样率信号处理[M].北京:清华大学出版社,1996.

[9]杜勇.数字滤波器的MATLAB与FPGA实现:Altera/Verilog版[M].北京:电子工业出版社,2015.

[10]万婷婷,孙丽华.级联梳状积分滤波器的原理及FPGA实现[J].微计算机信息,2009(17):243-244.

[11]徐艳,田克纯.基于FPGA的CIC滤波器的设计与实现[J].电声技术,2013,37(2):66-68.

[12]盖鹏翱,赵笛.CIC滤波器的原理及FPGA实现[J].无线通信技术,2005(4):52-55.

[13]王旭东,潘广祯.MATLAB及其在FPGA中的应用[M].北京:中国人民大学出版社,2005.

[14]刘芳.数字信号处理与MATLAB实现[M].计算机仿真,2009,26(1):335-338.

[15]谢海霞,孙志雄.多相抽取滤波器的FPGA实现 [J].电子器件,2012,35(3):331-333.

The realization of multistage CIC filter on FPGA

XIE Hai-xia,SUN Zhi-xiong

(School of Electronic Communication Engineering,Tropical Ocean University of Hainan,Sanya 572022,China)

CIC filter was a high efficiency filter,widely used in digital down conversion end software radio.It introduces the basic principles of CIC decimation filter and filter Hogenauer structure.Using Verilog HDL language programming to achieve this filter through MATLAB and Modelsim co-simulation,synthesis verify the correctness of the design and feasibility.

CIC;hogenauer structure;MATLAB;modelsim

TN911.72

A

1674-6236(2016)23-0183-03

2016-04-01稿件编号:201604001

海南省自然基金资助(20166224);琼州学院实践教改项目(QYSJ2013-001)

谢海霞(1978—),女,海南文昌人,硕士。研究方向:EDA技术在信号处理中的应用。