集成电路边界扫描测试中的电路网表结构分析

陈翎 潘中良

摘要:边界扫描测试能够对电路芯片间的互连和每个芯片内部的逻辑功能等进行检测,可以检测出电路中多种类型的故障,以确保电路具有较高的可靠性和电路功能的正确性。本文首先说明了边界扫描测试的结构;其次,给出了边界扫描测试软件的设计方法,对它的如下的主要模块即电路描述的输入、电路网表结构分析、完备性测试、互连测试、芯片内部功能的测试、测试结果输出等的功能进行了说明,重点对电路网表结构分析这个模块的实现进行了详细阐述。

关键词:集成电路 边界扫描 测试方法 软件程序 网表结构分析

中图分类号:TN407 文献标识码:A 文章编号:1007-9416(2016)07-0070-04

Abstract:The boundary scan testing can detect the interconnections among chips and the logic functions of each chip, it is able to detect the faults in the circuits, and can ensure the high reliability and the correctness of circuit functions. First of all, the structure of boundary scan testing is demonstrated in this paper. Secondly, the design method of boundary scan testing software is given, the functions of its main modules are shown, the modules include the circuit description input, circuit netlist structure analysis, interconnection testing, chip internal logic testing and test results output, etc. The implementation of circuit netlist structure analysis is described in detail.

Key Words:Integrated circuits, boundary scan, testing method, software program,netlist structure analysis

1 引言

在集成电路(IC)的生产过程中,涉及氧化、光刻、掺杂、淀积等多种工艺步骤,每种步骤都会对电路的质量与可靠性产生影响。为了保证电路具有较高的可靠性,必需对电路进行多种类型的测试。通过进行测试,可以检测出电路中的多种类型故障,例如,一条信号线的时延故障[1,2]、多条信号线之间的串扰故障[3,4]等,从而保证电路功能的正确性以及电路的可靠性。

对集成电路或印制电路板进行测试的传统方法是使用针床或测试探针,但随着电路集成度的不断提高,使得布线密度不断增加,信号线之间的间距越来越小,从而使得测试探针难以接触到引线,因此这种电路集成度的提高给传统的测试方法提出了严峻的挑战。特别是近年来出现的片上系统,它是在一块芯片上集成了整个系统的功能,在硬件结构上包括微处理器、存储器、信号处理器、数模转换器等[5,6],此时信号线之间的间距远小于测试探针之间的间距,采用这种物理的测试探针可能对系统的线路连接造成损坏,同时对系统内部的一些节点或信号线,就不能通过测试探针进行接触和访问。

为了解决电路芯片和印制电路板的测试问题,人们提出了边界扫描(Boundary Scan)测试技术,它是通过在芯片管脚和芯片内部的逻辑电路之间增加由移位寄存器所构成的边界扫描单元,来实现对测试矢量的施加以及对测试响应的捕获[7,8]。可以使用边界扫描测试对电路芯片间的连通性和每个芯片内部的逻辑功能等进行检测。本文对边界扫描测试的软件程序设计中的电路网表结构分析进行了详细说明,给出了对电路中的边界扫描结构进行提取的方法以及程序设计。

2 边界扫描测试的结构

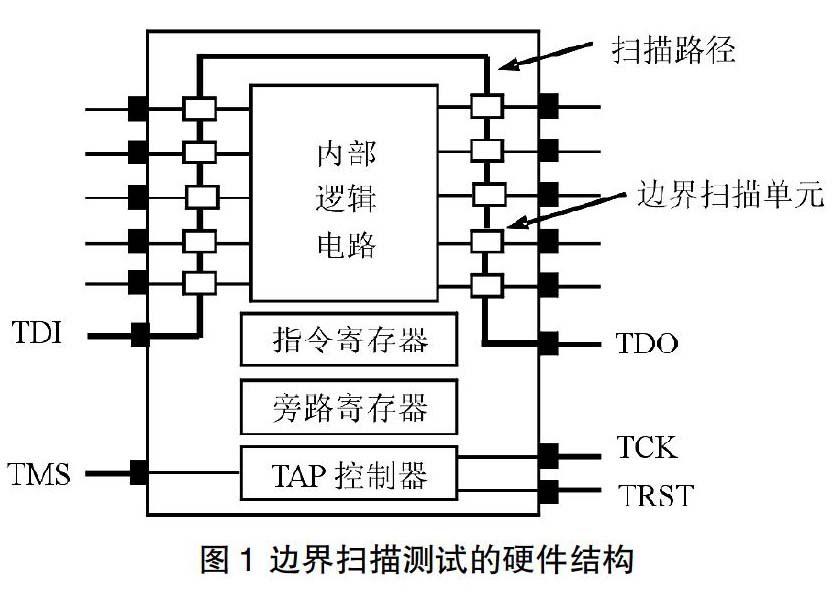

边界扫描测试的硬件结构主要由如下四个部分组成:(1)测试存取通道(TAP);(2)TAP控制器;(3)指令寄存器;(4)测试数据寄存器。在硬件上是在IC芯片的每个I/O引脚处添加一个边界扫描单元,以及添加一些测试控制逻辑。这种边界扫描单元是由一些边界扫描寄存器所组成,通过将这些寄存器连成扫描路径,构成扫描链[9,10]。这些边界扫描寄存器位于IC的外部引脚和IC的内部逻辑之间,可以在状态控制器(即TAP控制器)的控制下,对外部引脚和内部逻辑进行信号的采集或施加信号。如图1所示。

测试存取通道TAP(Test Access Port)是边界扫描测试电路与外部电路的接口,它包括以下五种控制信号:测试时钟

TCK、测试方式选择

TMS、测试数据输入

TDI、测试数据输出TDO、测试复位TRST。

(1)测试时钟。

TCK(Test Clock):它是用于控制边界扫描寄存器和TAP控制器的时钟。

(2)测试方式选择。

TMS(Test Mode Select):当该信号有效时,IC芯片处于测试模式,否则是处于正常工作模式。

(3)测试数据输入。

TDI(Test Data Input):用于边界扫描测试数据的输入,边界扫描指令和测试数据均由此进行输入。

(4)测试数据输出TDO(Test Data Output):用于边界扫描测试数据的输出,由TAP控制器的状态和指令寄存器的内容来决定哪些寄存器用于数据的输出。

(5)测试复位TRST(Test Reset):用于边界扫描测试的逻辑复位,低电平时有效,即当TRST的输入为低电平时,IC芯片进入正常工作状态,边界扫描测试的控制逻辑无效。这种测试复位TRST信号为可选信号。

TAP控制器是边界扫描测试的核心,它的输入信号为TCK、TMS和TRST(可选)。TAP控制器产生扫描数据寄存器和指令寄存器等所需的时钟信号,并在指令寄存器的配合下产生复位、执行测试、输出数据到缓冲器等信号。对测试数据的捕获、移位、更新等都必须在TAP控制器进入到相应的状态时才能进行。

以上对边界扫描测试的硬件结构进行了说明,在它的实际应用过程中,边界扫描测试需要与测试软件程序相结合,才能实现对IC芯片的自身功能和芯片间互连的测试。下面对边界扫描测试的软件程序设计进行阐述。

3 边界扫描测试的软件程序设计

3.1 边界扫描测试软件的功能与实现过程

边界扫描测试软件是通过使用边界扫描测试技术,完成对电路芯片的内部逻辑功能的测试,以及对芯片间的互连线的测试。能够检测芯片的内部逻辑功能是否正常,以及检测芯片间的互连线的多种类型的故障(例如,开路故障、短路故障、固定型故障s-a-0和s-a-1等),并指出故障的位置,以及故障的个数。具有电路描述的输入、电路网表结构分析、完备性测试、互连测试、芯片内部功能的测试、测试结果输出等多个模块。

对边界扫描测试软件的实现过程如下:通过对输入的电路芯片的结构描述文件进行预处理,提取出相关的边界扫描测试的信息,并采用链表等数据结构来说明电路中的所有信号线与各个模块之间的连接关系;针对多种类型的故障,例如,开路、短路、s-a-0和s-a-1故障等,设计测试矢量生成方法,以产生用于检测这些故障的测试矢量;对边界扫描测试的整个过程进行设计,包括测试矢量的施加、测试响应的捕获、测试链路上的数据移位、以及多种测试指令的操作与执行,以方便地进行对电路芯片内部逻辑功能的测试和对芯片间互连线的测试。

边界扫描测试软件由如下的多个模块组成:电路描述的输入、电路网表结构分析、完备性测试、互连测试、芯片内部功能的测试等。完备性测试是对边界扫描结构自身的功能正确性的测试;互连测试是对具有边界扫描功能的多个芯片间的互连线的测试;芯片内部功能的测试是使用边界扫描的链路完成对各个芯片的逻辑功能的测试。软件的主界面如图2所示,在主界面的菜单栏中有“文件”、“电路网表结构分析”、“完备性测试”、“互连测试”、“芯片内部功能的测试”、“测试结果输出”、“帮助”等菜单项。

3.2 电路网表结构分析

首先,在菜单项“文件”中有“新建”、“打开”、“保存”、“另存为”、“打印”、 “电路描述的输入”、“退出”等菜单命令。

菜单命令“新建”的功能是用于建立描述电路结构的文本文件,并在主界面的窗口中对文件的内容进行添加与修改等;菜单命令“保存”的功能是对在主界面的窗口中显示的文本文件进行存储(保存);菜单命令“另存为”的功能是对在主界面的窗口中显示的文本文件用另一个文件名进行存储;菜单命令“打印”的功能是在打印机上对在主界面的窗口中显示的文本文件进行打印输出。

菜单项“电路网表结构分析”的功能是对主界面的窗口中显示的电路结构描述文件进行分析与处理,获得电路的输入和输出信号线的名称、电路中的所有信号线与各个模块之间的连接关系、电路的边界扫描结构等信息;通过建立链表等数据结构,来保存这些电路结构信息,以供后续的操作步骤所使用。

对输入的描述电路结构的文本文件(也称为网表文件),需要从中提取出有关的边界扫描结构的信息,以在后续的测试过程中使用。可以把网表文件中的内容大致分为两部分:前一部分是对各个组件的描述,后一部分是互连结构的描述。

例如,可以直接使用采用 BSDL描述的电路结构,从中提取出电路的互连结构信息,这里,BSDL(Boundary-ScanDescription Language)它是超高速集成电路硬件描述语言(VHDL)的一个子集。从一个BSDL文件中可以获取如下三部分的信息:TAP通道、测试指令码、边界扫描单元。下面以Altera公司所生产的器件EPM7064AET44的BSDL文件为例,对这三部分信息进行说明。下面分别是从该器件的BSDL文件中截取的与这三部分有关的信息。

3.2.1 TAP通道的信息

attribute TAP_SCAN_IN of TDI: signal is true;

attribute TAP_SCAN_MODE of TMS: signal is true;

attribute TAP_SCAN_OUT of TDO: signal is true;

attribute TAP_SCAN_CLOCK of TCK : signal is (10.00e6, BOTH);

这里在进行测试时TCK的最大频率不能超过10M。

3.2.2 测试指令的操作码

attribute INSTRUCTION_LENGTH of EPM7064AET44: entity is 10;

attribute INSTRUCTION_OPCODE of EPM7064AET44: entity is "BYPASS (1111111111), "

& "EXTEST (0000000000)," & "SAMPLE (0001010101)," & "IDCODE (0001011001),"

& "USERCODE (0000000111)";

这里说明了指令长度为10位,以及“BYPASS”、“EXTEST”、“SAMPLE”、“IDCODE”、“USERCODE”等指令各自所对应的操作码,例如,指令“BYPASS”所对应的操作码为“1111111111”。

3.2.3 边界扫描单元的信息

attribute BOUNDARY_LENGTH of EPM7064AET44: entity is 192; // 说明共有192个边界扫描单元

attribute BOUNDARY_REGISTER of EPM7064AET44 : entity is

--BSC group 0 for dedicated input pin 38 //管脚38的边界扫描单元的信息

"0 (BC_4,IN38,input, X)," & "1 (BC_4,*,internal, X)," & "2 (BC_4,*,internal, X)," &

--BSC group 1 for dedicated input pin 37 //管脚37的边界扫描单元的信息

"3(BC_4, IN37,input, X)," & "4 (BC_4,*,internal, X)," & "5(BC_4,*,internal, X)," &

…… ……

--BSC group 63 for dedicated input pin 39 //管脚39的边界扫描单元的信息

"189 (BC_4, IN39,input, X)," & "190 (BC_4,*,internal, X)," & "191 (BC_4,*,internal,X)";

这里,每个管脚所对应的边界扫描单元的描述格式为:num(cell,port,function,safe[ccell,disval,rslt])。该格式中每个部分的含义如下。

num为边界扫描单元的标号,它的值为0是表示该单元是最靠近TDO。

cell为所使用的单元类型,例如,cell为BC_1时表示使用一个通用单元,可用作输入和输出;cell为BC_2时表示使用一个具有并行输出锁存器的输入单元;cell为BC_3时表示使用一个没有并行输出锁存器的输入单元;cell为BC_4时表示使用一个只允许作为信号捕获的输入单元;cell为BC_5时表示使用一个三态管脚单元,并且是由一个系统管脚来控制三态输出;cell为BC_6时表示用于双向管脚中的输入/输出单元。

port说明该单元是用于驱动还是用于接收数据;若该单元是被用于对数据输出的控制单元或作为一个内部单元使用,则用“*”表示。

function说明单元的功能。例如,当function为“clock”时,则是时钟输入端的单元;当为“control”时,则是控制三态方向的单元;当为“internal”时,则是捕获内部数据;当为“input”时,则是简单的输入管脚接收器;当为“output2”时,则是为二态输出提供数据;当为“output3”时,则为三态输出提供数据;当为“bidir”时,则是用于双向管脚的双向单元。

safe是受控单元不作用时的安全值。使用该参数可以减少不确定数据对电路的影响;其中ccell为受控单元;disval为用于控制使ccell所指单元不作用的值;rslt为该单元没有被驱动时的状态。

4 实验结果

我们用C++语言编制了边界扫描测试的软件,其主界面如图2所示。该软件在微型计算机上运行,通过与硬件边界扫描控制器的结合,实现了对被测电路的整个测试过程。

在该软件的主界面的菜单项“文件”中的菜单命令“打开”的功能是直接从计算机中找到并选中描述电路结构的文本文件。从出现的对话框中点击“打开”按钮,之后在主界面的窗口中显示该文本文件。例如,图3是选取D盘目录D:\BST\Circuitdes中的文件Circuit10.vhd的例子。

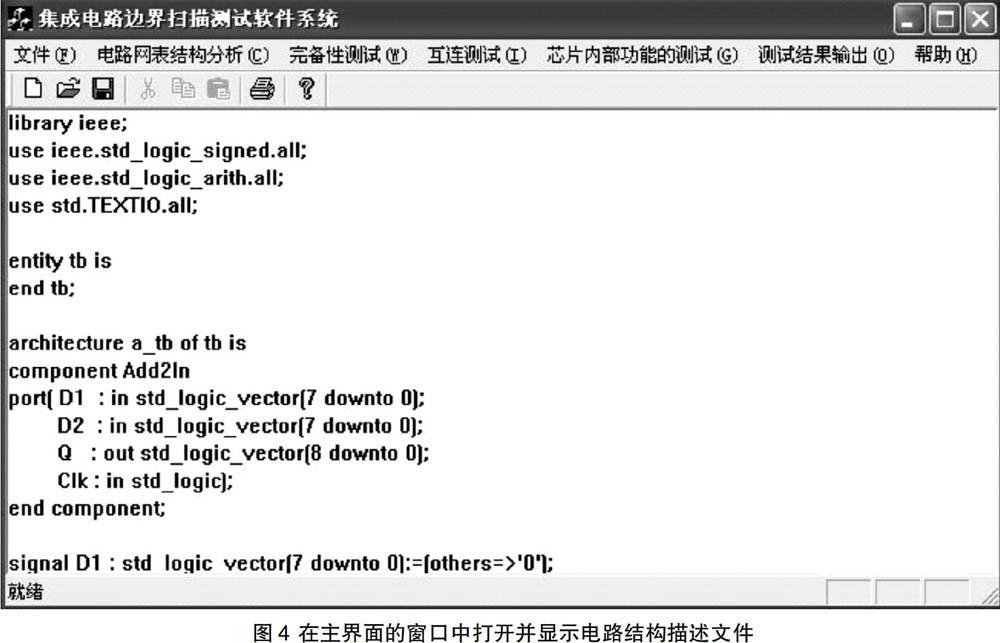

图4是从出现的对话框中点击“打开”按钮之后,在主界面的窗口中显示该文件Circuit10.vhd的内容。

对软件主界面中的菜单项“电路网表结构分析”,点击该菜单项,若从出现的对话框(如图5所示)中选取“进行网表结构分析”,并按“确定”按钮,则软件系统是对输入的电路描述文件(例如Circuit10.std)所描述的电路进行网表结构分析,并将获得的互连结构信息保存在默认的文件中(例如Circuit10.bst)。

若从出现的对话框(如图5所示)中选中“选取待处理的电路描述文件,然后进行网表结构分析”,并按“确定”按钮,则软件系统是直接对选取的电路结构描述的VHDL 文件或BSDL文件进行网表结构分析,并将获得的互连结构信息保存在默认的文件中。

这种操作的结果文件是供软件系统的后续操作“完备性测试”、“互连测试”、“芯片内部功能的测试”等使用,并直接作为这些操作的输入。例如,对电路结构描述文件Circuit10.vhd,经过“电路网表结构分析”这一步的操作之后的结果被保存在文件Circuit10.std中。

为验证边界扫描测试的软件系统的性能,我们设计了一个被测电路板,在该板上主要有如下六个芯片:EP1C3T144、EPM7064AET44、四个SN74LVTH182512。把这六个芯片通过边界扫描测试总线中的TCK、TMS、TDI和TDO等进行连接。同时,在它们的互连线上设置了固定型s-a-0和s-a-1、开路、短路等故障。

通过使用前面的方法对输入的电路芯片的结构描述文件进行处理,提取出每个芯片的边界扫描测试的信息,进行电路网表结构分析,并采用链表等数据结构来说明电路中的所有信号线与各个模块之间的连接关系。实验结果表明,所设计的软件程序能准确地提取出每种芯片的边界扫描信息,为后续的测试提供了方便,使整个测试系统能检测芯片的内部逻辑功能是否正常,以及能够检测芯片间互连线的固定型故障、开路、短路等多种类型故障。

5 结语

边界扫描测试能够对具有高集成度的电路芯片和印制电路板等进行互连测试与内部的逻辑功能测试。通过编制测试软件并与硬件上的边界扫描控制器的结合,能实现对被测电路的整个边界扫描测试的过程。本文对边界扫描测试的软件程序设计中的电路网表结构分析这个模块的实现进行了详细阐述,给出了对电路中的边界扫描结构信息进行提取的步骤。

参考文献

[1]L.Bao, W.Lu. Dynamic statistical-timing-analysis-based VLSI path delay test pattern generation[J]. IEEE Trans. on VLSI, 2015, 23(9):1577-1590.

[2]B.Arslan, A.Orailoglu. Power-aware delay test quality optimization for multiple frequency domains[J]. IEEE Trans. on CAD, 2016, 35(1):141-154.

[3]K.Peng, M.Yilmaz, K.Chakrabarty. Crosstalk- and process variations-aware high-quality tests for small-delay defects[J]. IEEE Trans. on VLSI, 2013, 21(6):1129-1142.

[4]D.Sourav, E.N.Dmitri, M.Sasikanth. Compact physical model for crosstalk in spin-wave interconnects[J]. IEEE Trans. on Electron Devices, 2015, 62(11):3863-3869.

[5]潘中良.系统芯片SoC的设计与测试[M].科学出版社,2009.

[6]陈光禹,潘中良.可测性设计与技术[M].电子工业出版社,1997.

[7]IEEE Std1149.1-2001. IEEE standard test access port and boundary-scan architecture[S]. 2001.

[8]Y.Hiroyuki, M.Hiroyuki, N.Takanobu. On detecting delay faults using time-to-digital converter embedded in boundary scan[J]. IEICE Trans. on Information and Systems,2013,96(9):986-1993.

[9]S.Stephen,R.Aubin.Contact less test of IC pads,pins, and TSVs via standard boundary scan[J]. IEEE Design & Test of Computers,2012,29(5):55-62.

[10]F.Farnaz,N.Bahareh,T.Fatemeh. A new approach to model the effect of topology on testing using boundary scan[J].Journal of Electronic Testing,2015,31(3):301-310.