基于USB2.0的LVDS数据采集系统设计

张瑞生

【摘要】 利用USB总线通用和即插即用的特点,研制了基于USB2.0接口的LVDS数据采集系统,该系统利用USB总线来接收被测对象的LVDS数据,使其采集、处理更加方便快捷。文中详细介绍了系统结构,给出了硬件系统设计思想,并对各子模块的详细设计进行了阐述。

【关键词】 LVDS USB总线 便携式 数据采集

前言

LVDS数据传输和接口技术,具有高速度、低功耗、低成本、低误码率、低辐射等优点,其核心是采用低电压摆幅(350mV)高速差动传输数据,实现点对点或者一点对多点的连接,在对信号完整性、低抖动及共模特性要求较高的互联系统中得到广泛应用,已成为高速数字信号传输的国际通用接口标准。

LVDS对传输介质要求不高,更有利于恶劣环境下图像数据传输。为方便LVDS数据在便携及特殊情况下的测试,文中设计了基于USB2.0的LVDS数据采集系统,通过USB总线连接测试计算机,组成不需外接电源的移动测试系统,避免了常规测试设备庞大、笨重的缺点,满足便携测试需求。

一、数据采集系统结构

系统分为5个模块:LVDS接口模块、存储器模块、USB接口模块、FPGA处理模块、电源管理模块,如图1所示,主要实现如下功能:

1、LVDS输入信号缓冲与数据转换;

2、采集数据的存储;

3、与上位机的通信接口控制;

4、数据采集处理、存储管理和接口通讯协议解析;

5、转换产生系统需要的各种电源。

二、接口模块

LVDS输入信号经缓冲器后直接进入FPGA,在FPGA内进行解码和存储工作。选用TI公司的SN65LVDS048A,该芯片为400Mbps LVDS信号接收器,输出标准3V CMOS信号,可直接给FPGA的IO端口。

三、FPGA处理模块

处理模块是整个数据采集系统的控制核心,选用FPGA实现,具有灵活、可靠、实时性和稳定性高等特点。主要包括对LVDS信号的采集和存储,与各接口之间的数据通信,对存储芯片的控制和数据存储。FPGA直接将采集的数据按帧结构存储到非易失存储器,以供在空闲时通过USB读取数据;在进行数据存储的同时,将最新一帧数据放到缓冲区中,以供外部接口读取实时帧的数据。

3.1 LVDS采集存储

LVDS信号经过LVDS缓冲器转换为LVTTL信号,直接进入FPGA中,实现信号的解码和数据存储。FPGA选用Xilinx公司的XC3S200AN。输入信号在场同步VSYN(高)有效时,根据时钟Vclk对数据VD进行锁存和移位,由高到低。在字完成VBYT-SYN的上升沿将移位后的数据锁存到lvdsdata,同时产生写同步信号。数据解码如图2所示。利用与数据同步的写信号,在Vclk下将数据写入缓冲FIFO,在VSYN有效后数据有效。

3.2与USB及存储器接口

FPGA与USB总线芯片连接,USB接口的FIFO在非满状态下写有效,根据控制信号,在FPGA中获取命令译码,当发出采集指令时,读有效,从而将数据通过芯片输出。

FPGA上挂接了两种存储器:SDRAM和NAND FLASH,分别用于当前帧实时数据和连续数据帧的存储。SDRAM选用MT48LC16M16A2,具有16M存储空间,16位数据宽度,读写速度快。Flash选用两片8位数据宽度,组合成16位数据宽度。

四、存储器模块

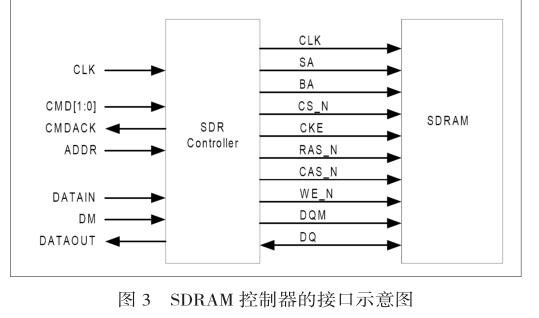

在LVDS数据采集系统中,对SDRAM的读写控制主要是通过编写SDRAM读写控制器,将SDRAM的读写简化成SRAM的形式,对于连续存储区的存储和读取,在进行编码后通过FPGA内建立的异步存储FIFO-A写入FLASH。图3为SDRAM控制器与外部的接口示意图,右端为与SDRAM对应信号,左端为与FPGA对应系统控制信号。时序仿真如图4所示。

五、USB接口模块

采用Cypress公司的CY7C68013A作为USB接口芯片,完成系统维护和数据下载等功能,包含驱动程序、接口单片机程序和与FPGA接口设计。

六、电源管理模块

采用NS公司的LP3997MM-3.3芯片通过DC-DC转换为整个系统提供+3.3V,再通过LDO转换出所需的1.5V。

七、结束语

本文在充分研究LVDS传输特性和USB总线的基础上,

详细阐述了USB-LVDS数据采集系统总体结构和硬件设计。

经过在多型产品的使用和试验,以其灵巧、便携、可热插拔、可靠性高等特点,较原有PCI总线测试系统具明显优势。

参 考 文 献

[1] 赵传猛,一种简单的SDRAM控制器实现,计算机与数字工程,Vol.38 No.8,197~200

[2]林刚勇, 马善农,许邦莲.CY7C68013在数据传输中的应用[J]微计算机信息, 2007(10 ):76一75

[3]盛大鹏,基于FLASH的高速大容量存储器的研究,中国科学院研究生院硕士论文,2008

[4]NS,LVDS用户手册(第四版),2008

[5]杨维,高速低压差分信号传输接收电路设计,哈尔滨工业大学硕士学位论文,2010