基于硅衬底静电感应晶体管器件仿真与研究

王富强,瞿宜斌,马行空

(中国人民解放军第93856部队,甘肃 兰州 730070)

基于硅衬底静电感应晶体管器件仿真与研究

王富强,瞿宜斌,马行空

(中国人民解放军第93856部队,甘肃 兰州730070)

摘要针对静电感应晶体管理论研究迟滞于实践过程,文中利用软件Silvaco Tcad,从器件仿真入手,对影响硅基表面栅静电感应晶体管器件电学性能进行了理论研究。仿真得到了反偏栅压约为0 V、漏电压<20 V时,器件表现类五极管饱和特性曲线,器件电流约为10(-5) A,此时沟道状态为预夹断。当反偏栅压为-1.5 V、漏电压逐渐增大到300 V时,器件表现为类三极管不饱和特性曲线,器件电流约为10(-6) A,此时沟道状态为完全夹断,研究结果静电感应晶体管工艺实践提供了参考。

关键词静电感应晶体管;沟道势垒;器件仿真

静电感应晶体管是一种结构灵敏器件,因其集高电压、大电流、高频率和栅可关断能力等优异性能于一身,而得到广泛应用[1]。但静电感应晶体管作为新型半导体器件的一种,理论研究滞后于实践过程,具有经验性和唯象性,且利用计算机辅助研究也不多见。因此,本文通过半导体仿真软件Silvaco Tcad对器件进行仿真模拟,达到对器件的理论研究和直观剖析其工作的物理机理的目的。

静电感应晶体管器件结构和材料参数直接影响着相应的电学参数,且各参数间有着密切关系[2-3]。本文研究的表面栅型静电感应晶体管是垂直场效应晶体管,沟道两侧的栅压严格控制着沟道势垒的高低,随着栅源偏置电压的变化以及器件结构参数的不同,该器件能呈现出以下3种不同特性[4]:(1)类五极管特性;(2)类三极管特性;(3)双极特性[5]。因双极模式下静电感应晶体管属于另一种新型的功率器件,所以在本文中不做讨论。

1器件结构设计

静电感应晶体管器件典型结构包括表面栅型、沟槽栅型和隐埋栅型。无论何种结构,现有研究成果表明,沟道载流子分布、I-V特性以及影响器件电学特性的关键参数都有类似性,但表面栅结构可制作出功率小、电流容量大和频率较高的静电感应晶体管,且易在实验中制作得到,同时通过软件容易实现结构和工艺仿真。所以,为实现对静电感应晶体管工作机理解释和电学特性模拟,本文在仿真研究中采用表面栅结构静电感应晶体管,其仿真研究采用的元胞结构参数如表1所示。

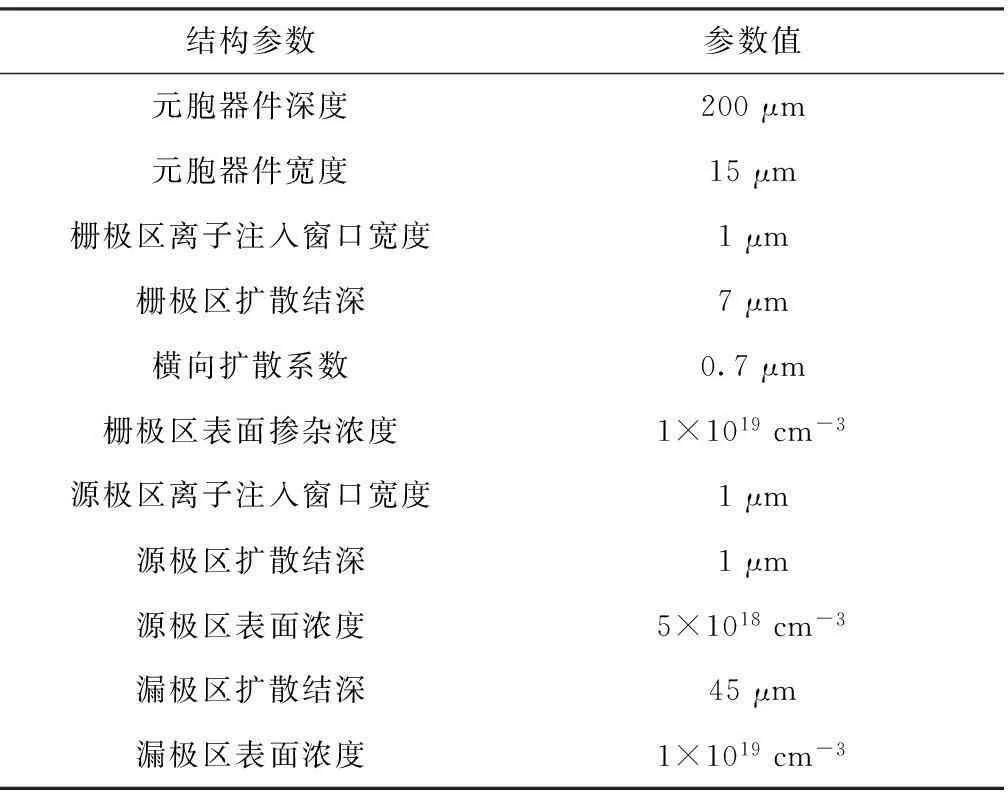

表1 仿真研究中采用的表面栅SIT元胞结构参数

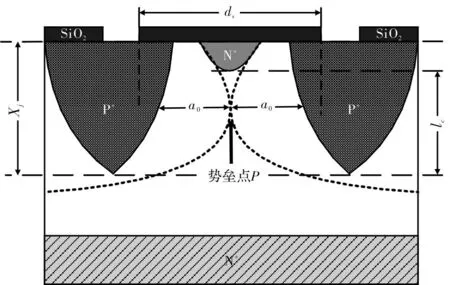

器件结构如图1所示。结构从上往下,从左往右,源极区为重掺杂的n+区,栅极区为重掺杂p+区,中间沟道区以及往下区域均为漂移区,为轻掺杂的n-区,漏极区为重掺杂的n+区。

图1 器件内部相关参量示意图

2类五极管特性

2.1沟道电势分布

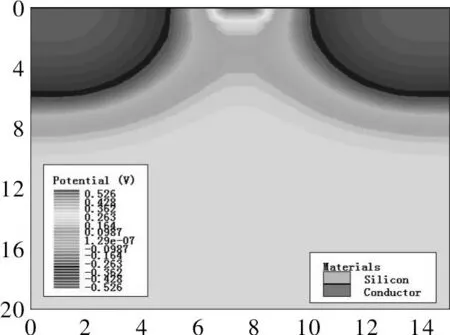

取VG=VS=0 V,利用Silvaco Tcad软件模拟器件沟道电势分布,结果如图2所示,沟道处于预夹断状态。按照设计要求,栅压为零时,沟道应为打开状态。之所以在实际器件工艺生产中,栅极区耗尽层向沟道中心线扩展至恰好相交,这是因为实际栅极区掺杂工艺中,横向扩散比较大,导致栅源之间已不是简单的平面结,而是存在曲率的柱面结。

图2 VG=0 V时,基于硅的SIT沟道电势Contour图

沟道完全夹断前为预夹断状态,对比真空管和静电感应晶体管,后者更容易发现近似平面场效应管的类五极管模式,这是由于在半导体器件中,全部固态半导体材料的电子饱和速率约为107cm/s,而真空管电子饱和速率约为1010cm/s,这个速度和光在真空中传播速度非常贴近,是固态器件电子饱和速度的约1 000倍,所以固态器件的相应饱和电流也更低,在类五极管特性时静电感应晶体管更容易出现饱和限制。

2.2V-I特性

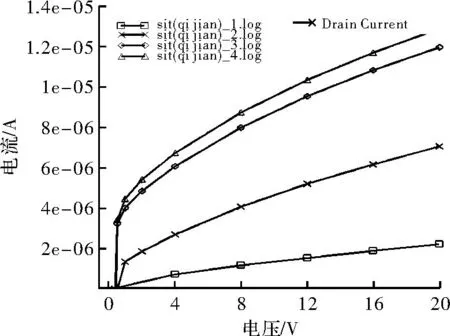

在栅电压微小(VGS≈0 V),且漏电压<20 V时,利用Silvaco Tcad软件模拟静电感应晶体管的I-V特性曲线,如图3所示。器件拥有相对偏高的器件电流(约为10-5A级),其曲线簇近似于平面半导体场效应晶体管[6],均类似于真空五极管。

图3 基于硅的SIT在类五极管特性下的伏安曲线

图3中显示,栅压不变时,当漏电压较小,器件电流曲线几乎为一条直线;当漏电压继续增大到一定值(大于或等于膝点电压)时,I-V曲线变得平缓,器件电流逐渐趋于饱和。同时,不同的栅偏压对应不同的电流曲线、不同的膝点电压和漏电流,在图3中,从上往下,栅极反偏电压依次增大,漏电流相应减小。

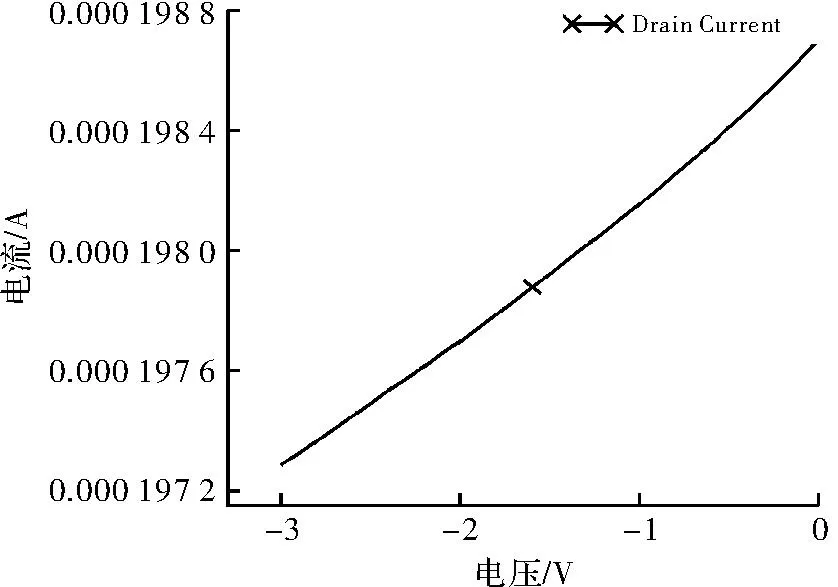

图4 基于硅的SIT转移特性曲线图

在类五极管特性曲线图3中可看出,当栅压反偏VGS<0 V,且持续增大时,漏电流将快速减小,取VDS=10 V,得到的相应漏电压条件下的转移特性曲线。如图4所示,曲线随栅偏压变化呈近似线性趋势。

3类三极管特性

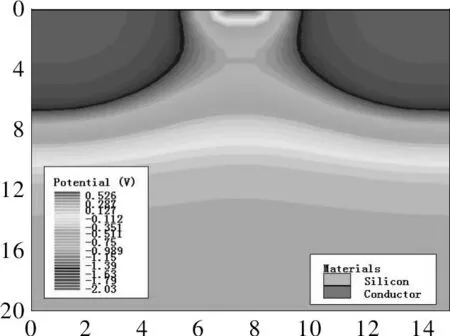

3.1沟道电势分布

在类五极管特性分析的基础上,若漏极加正偏压且保持不变,继续减小负栅压VGS直到某一值时,沟道彻底耗尽,此时静电感应晶体管处于夹断状态,定义此刻的临界负栅压为相应漏偏压条件下的截止电压。当负栅压VGS=-1.5 V时,仿真器件的沟道电势Contour图,如图5所示,易见此时沟道中,栅极区自建电势区宽度向沟道中心扩展并交错,沟道已全部耗尽。

图5 VG=-1.5 V时,基于硅的SIT沟道耗尽图

当持续增大漏偏电压,直到大于类五极管特性中所能体现的边界值,静电感应晶体管的电流-电压特性曲线将相似于PN结,和真空三极管相类似。将静电感应晶体管这种工作特征称为类三极管特性。

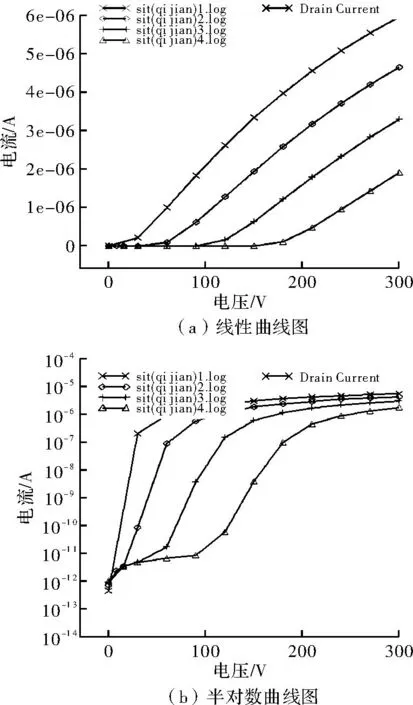

3.2V-I特性

图6为静电感应晶体管的类三极管伏安曲线图。可以看到,当反偏栅压一定时,随着漏偏压的大幅增加,沟道势垒相应降低,漏极区电子越过沟道势垒进入沟道区,沟道导通将再次形成电流。当漏偏电压增大到一定数值时,漏电流增大明显且呈指数趋势。特性曲线表明,随着漏偏电压均匀变化,曲线之间的间距基本相同,器件的放大倍数比较稳定。另外,在该模式下器件电流相对于类五极管特性时变小。图6(a)中,静电感应晶体管明显表现出不饱和的类三极管特征[7-8],但将纵坐标变为对数值后,可明显看出曲线表现为不同的特征,按照漏电流变化趋势依次将曲线分为预夹断零区、指数增长区和线性平缓区,如图6(b)所示。

图6 基于硅的SIT在类三极管特性下的I-V曲线图

其中,预夹断零区[9]为图6(b)中曲线簇最下端部分,在栅偏压很低(VDS<50 V)时,器件漏电流较小,约等于10-12A,所以可认为在这个漏偏压范围内曲线为死区,或是电流产生区。对常开型静电感应晶体管结构,栅区的耗尽层没有相互连接在一起,沟道呈打开状态,所以也就没有预夹断区。对于常关型静电感应晶体管,栅极区的沟道耗尽层相互连接,沟道呈夹断状态,当VDS的逐渐增加,栅极区耗尽层相应向漏区扩展,此时形成预夹断状态。继续增大VDS,漏极电子在电场的作用下进入沟道区并向栅极移动,从而产生电流。其器件电流大小为

(1)

指数增长区,随着漏电压继续增大,漏极电流以近乎指数形式迅速增加,这种增长形式是由漏电场与势垒高度的变化关系决定的,其主要原因是在该区域沟道势垒随着漏偏压的增大而迅速下降。在这个区域,栅极偏压直接影响着预夹断区向指数区过度的转折电压,同时影响着指数区曲线的斜率大小。就整体曲线而言,这个区域SIT的电流对漏极偏压非常敏感,因此被用作放大器是个不错的选择。

线性平缓区,针对同一栅极反偏电压,随着静电感应晶体管的漏极偏压VDS的增大,伏安特性曲线变平坦,器件电流呈线性趋势,步入线性变化区。在图6(b)中,从下往上往右,随着VGS的增大,漏电流的横向增量明显加大。

在静电感应晶体管工作时,可看到静电感应晶体管的电流按变化趋势分为三个区段,其中源极电流IS等于漏极电流ID,而沟道势垒的高低直接控制其大小

(2)

在式(2)中,Dn代表电子的扩散系数;Nsub代表沟道漂移区的掺杂浓度;Aeff代表沟道实际有效的沟道宽度;φC代表沟道势垒的高度。分析式(2),势垒高度是变量,其余均为常量,则对于一个结构确定的静电感应晶体管器件,器件电流仅受控于沟道势垒高度。另外,和类五极管电流-电压特性曲线相似,所选择的栅压直接影响着每一条类三极管电流-电压特性曲线的变化。若再增大反偏的栅压,关断电压也就是膝点电压将会变得更高,当反向VGS足够大时,栅源间将发生击穿,此时,即为关断电压的最大值。所以,静电感应晶体管通过较小的反偏栅压匹配相当大的漏源电压,且可以阻滞沟道电子流动。

4结束语

利用软件SilvacoTcad中器件仿真Atlas模块对静电感应晶体管沟道电势分布和伏安特性进行了仿真模拟。得到了静电感应晶体管在不同条件下表现为类五极管饱和特性和类三极管不饱和特性,并对其沟道状态分布原因和器件工作机理进行了理论研究,仿真结果和器件实际特性完全吻合。本文所取得的结果可在较大程度上避免当前器件结构设计的盲目性,给工艺实际起到了理论指导作用,并增强了制造过程中技术措施的针对性。

参考文献

[1]李思渊.静电感应器件作用理论[M].兰州:兰州大学出版社,2006.

[2]NishizawaJ,YamamotoK.Highfrequencyhighpowerstaticinductiontransistor[J].IEEETransactionsonElectronDevices,1978,25(3):314-322.

[3]NishizawaJ,TerasakiT,ShibataJ.Field-effecttransistorversusanalogtransistor(staticinductiontransistor)[J].IEEETransactionsonElectronDevices,1975,22(4):185-197.

[4]张万荣,罗晋生.SITI-V特性模型[J].西安交通大学学报,1996,30(2):20-27.

[5]NishizawaJ,OhmiT,MochidaY,etal.Bipolarmodestaticinductiontransistor[J].JapaneseJournalofAppliedPhysics,1980,19(S1):289.

[6]BaligaBJ.Breakoverphenomenainfield-controlledthyristors[J].IEEETransactionsonElectronDevices,1982,29(10):1579-1587.

[7]WangYS,LuoXL,LiHR,etal.Improvementsonradiation-hardenedperformanceofstaticinductiontransistor[J].ScienceChinaInformationSciences,2010,53(5):1089-1096.

[8]LiuCJ,WangZX,WangYS.Physicaleffectofcarrierdistributioninthechannelofstaticinductionthyristor[J].JournalofSemiconductors,2014(8):014-019.

[9]朱延超.小功率音频静电感应晶体管的特性研究[D].兰州:兰州大学,2014.

Research on and Simulation of Static Induction Transistor Based on Silicon Substrate

WANG Fuqiang,QU Yibin,MA Xingkong

(Troop 93856,PLA,Lanzhou 730070,China)

AbstractThe practice process of static induction transistor (SIT) stays ahead of theoretical research.A theoretical research on the electrical performance of the SIT based on Silicon by is performed from the point of device simulation using the Silvaco Tcad software.The results show that the I-V performance of the device is the class pentode saturation characteristic,with a device current of about 10(-5) A and pre-pinch off channel state at about 0 V reverse bias gate voltage and 0~20 V drain voltage.Secondly,under the condition of -1.5 V reverse bias gate voltage and 0~300 V drain voltage,the I-V performance of the device shows the class triode unsaturated characteristic curve,with a device current of approximately 10(-6) A and completely pinched off channel.

Keywordsstatic induction transistor;channel barrier;device simulation

中图分类号TN32

文献标识码A

文章编号1007-7820(2016)04-012-04

doi:10.16180/j.cnki.issn1007-7820.2016.04.004

作者简介:王富强(1988—),男,硕士。研究方向:器件和集成电路设计。

收稿日期:2015- 08- 25