高性能画质处理算法通用FPGA验证平台

杨 强

(四川长虹电器股份有限公司,绵阳 621000)

高性能画质处理算法通用FPGA验证平台

杨强

(四川长虹电器股份有限公司,绵阳621000)

摘要:本文介绍了一种通用的画质处理算法FPGA硬件验证平台。该FPGA硬件验证平台是为验证画质处理算法而设计的,具有视频功能全面、逻辑容量大、时钟资源丰富、支持显示屏接口种类多和机械结构可靠的优点,是进行视频画质处理算法验证比较理想的FPGA验证平台。

关键词:画质处理算法;FPGA硬件验证平台;大屏幕液晶电视机;HDMI视频输入;LVDS输出接口;Vby1输出接口

1 引言

随着家用电视机向智能化和大屏幕化方向发展,市场对电视机的画质体验提出了更高的要求。目前,4K×2K分辨率的大屏幕电视机已经逐步成为市场的主流,但是电视节目源大部分还是FHD高清电视格式以及分辨率更低的网络视频源。于是,通过高性能的画质处理算法,比如高级图像缩放算法、图像细节增强算法、图像递归降噪算法和网络视频噪声消除算法对输入视频信号进行加工处理,以尽可能高的品质在大屏幕电视机上实现图像显示就显得非常必要。由于视频图像的动态特性,画质处理算法效果的验证除了在计算机上通过软件仿真外,最终的效果验证需要在硬件平台上实际运行检验。硬件平台实现方案一般有两种,一种是制作芯片验证画质处理算法,另一种是通过FPGA平台验证画质处理算法。制作芯片进行验证的方案周期长、灵活性差、成本高昂,而FPGA平台由于其内部丰富的逻辑资源、灵活的可编程性以及高速的性能,成为验证画质处理算法硬件验证平台的首选。

2 FPGA验证平台整体结构

FPGA验证平台采用日本某公司基于Xilinx Kintex-7的TB-7K-325T-IMG开发板作为基板进行二次开发,扩展接口板利用TB-7K-325T-IMG开发板提供的高密度、高速度接口,将所有的外围电路设计成一个整体扩展板和基板相结合,这样大大提高了基板和接口板之间电气连接和机械连接的可靠性,避免了FPGA平台在上电使用过程中因为接口板松动导致接触不良损坏电路板。接口板上包含了画质处理算法验证需要的从视频输入到液晶显示屏驱动的完整的电路单元。其中包括HDMI1.4A输入接口电路、TB-7K-325T-IMG开发板、Vby1输出接口电路、LVDS输出接口电路、液晶显示屏接口电路、微处理器控制电路、RS232接口电路、复位电路和时钟电路、电源产生电路等。FPGA验证平台是一款非常通用的画质处理算法开发平台,在功能上具有非常好的通用性,结构上具有非常高的可靠性。如图1所示。

图1 FPGA验证平台整体框图

3 FPGA验证平台单元电路

3.1TB-7K-325T-IMG开发板

TB-7K-325T-IMG开发板是日本某公司设计的一款基于Xilinx Kintex-7系列FPGA芯片的专门面向视频处理应用的通用开发平台,该开发平台的参考设计套件还提供了LVDS接口实现方案,以及视频处理不可缺少的DDR3控制器实现方案,大大简化了开发平台的使用难度。为方便用户进行二次开发,搭建适合于用户应用的新的开发环境,开发板提供了两个HPC(High Pin Count)和两个LPC (Low Pin Count)外围扩展接口,扩展接口的电压可以在2.5V和3.3V之间选择,接口电平可以是2.5V CMOS电平、3.3V CMOS电平或者高速LVDS差分电平信号。多种接口电平选择和数目庞大的IO为外接扩展接口提供了灵活的选择空间,每个HPC和LPC接口的内部还有专门的时钟输入引脚,这样的引脚安排使得在接收外界扩展板输出信号的时候,能对输入的时钟利用FPGA芯片内部的PLL和DLL资源对时序进行调整,以便更好地满足接口的时序要求。开发板上提供了丰富的时钟资源,能够满足画质处理算法逻辑对外接时钟输入的要求。开发板上提供的XC7K325T-2FFG900CES芯片,内部集成有大量的存储器,方便画质处理算法对行存的大量需求。

3.2HDMI1.4A输入接口电路

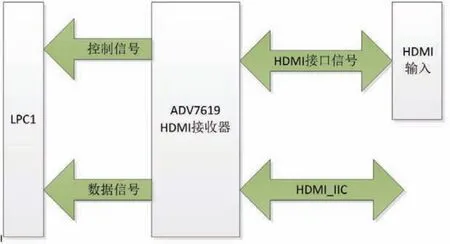

HDMI1.4A输入接口电路是视频信号的输入通路,可以接收480P,576P,720P,1080P,4K×2K等多种格式的视频输入。HDMI1.4A输入接口电路采用ADI公司设计的ADV7619芯片,这款芯片自带硬件HDCP处理功能,大大简化了芯片HDCP控制的软件要求。ADV7619芯片内部还集成有色度空间转换功能,可以实现视频信号在不同色度空间的转换,在不经过内部色度空间转换模块,420格式输入的情况下,ADV7619芯片可以支持输入4K×2K@60Hz信号,这个功能对画质处理芯片算法验证至关重要。ADV7619芯片输出的信号可以设置为DDR输出方式,奇偶点输出方式等,降低输出时钟的频率,降低电磁干扰。如图2所示。

图2 输入接口电路框图

3.3Vby1输出接口电路

Vby1输出接口电路是将TB-7K-325T-IMG开发板输出的LVDS格式的液晶显示屏驱动信号,通过扩展板上的转换芯片变成驱动液晶显示屏的Vby1格式信号。传统的液晶显示屏驱动接口长期以来采用的都是LVDS格式信号,但是随着液晶显示屏分辨率的不断提高和帧频的不断提升,满足显示要求所需的LVDS接口线数目越来越多,增加了生产成本,降低了系统的可靠性。针对市场对液晶显示屏驱动接口的要求,日本某公司制定了Vby1接口标准。Vby1接口标准非常类似于现在以太网使用的物理层传输标准,只是传输方向为单向。Vby1接口标准采用CDR技术,没有单独的时钟信号,而是通过8B/10B编码方式,将时钟信息嵌入到数据流中,然后在接收端通过CDR技术分离出数据和时钟。这样的处理方式消除了数据和时钟之间存在的延时偏差问题,使得数据的传输速率不再受时钟和数据延时偏差的影响。这样的话,数据线的传输长度得到了很大的延伸,最高数据传输率受到的限制只是信号衰减损耗,这可以通过对信号进行预加重的办法来加以改善。Vby1接口的数据传输速率可以达到3Gb/s以上,一对Vby1数据线传输的数据,相当于6 对LVDS信号传输的数据量(包含一对时钟信号)。

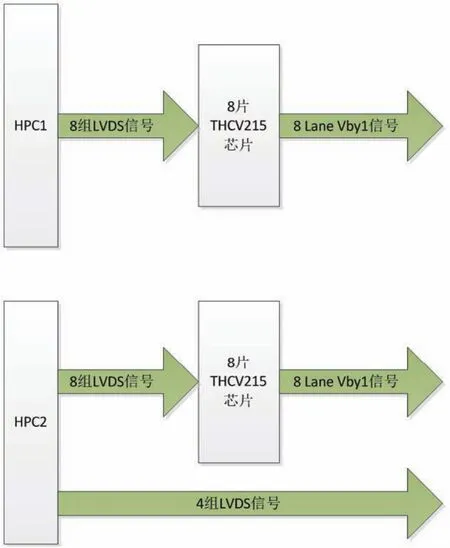

FPGA验证平台的Vby1输出接口电路使用8片THine公司的THCV215芯片,每片芯片将两组LVDS信号转换成两路Vby1输出信号,每组LVDS信号包含一对差分时钟和5对数据信号,这样的话可以支持16路Vby1数据输出信号,基本上可以满足各种常见液晶显示屏的驱动要求。THCV215芯片具有预加重和驱动能力控制输入端,可以根据工作环境要求进行选择,确保Vby1数据信号在比较坏的工作环境下也能保证较高的信号品质。由于数据编码中采用了8B/10B编码方式,使得数据信号中包含的直流成分大致平衡,从而使得Vby1输出信号可以采用电容隔离的交流耦合方式。交流耦合方式克服了接口共模电平不同带来的影响,使得接口之间的连接非常方便。THCV215芯片还提供多种像素位数选择,包括6位、8位、10位和12位,从而满足不同视频应用的要求。如图3所示。

图3 输出接口电路框图

3.4LVDS输出接口电路

为了支持LVDS接口的液晶显示屏,FPGA验证平台提供了LVDS输出接口。LVDS输出接口直接连接到液晶显示屏驱动插座接口,采用100R阻抗差分对进行布线,并按照LVDS标准的要求作等长匹配。TB-7K-325T-IMG开发板的HPC和LPC接口信号都是按照差分对安排的,在TB-7K-325T-IMG开发板上,差分对走线的特性阻抗设计为100R,正好是常用LVDS标准差分走线的特性阻抗。利用TB-7K-325T-IMG开发板参考设计提供的例子可以很方便地生成所需要的LVDS IP,然后利用TB-7K-325TIMG开发板上能支持LVDS信号速率的输出引脚就能非常方便地搭建出所需的LVDS接口。目前,FPGA验证平台的LVDS接口电路最多可以支持4组LVDS信号输出,基本上可以满足大多数LVDS接口液晶显示屏的驱动要求。

3.5TB-7K-325T-IMG开发板接口

TB-7K-325T-IMG开发板扩展接口由4个电路板连接座组成,包括两个HPC连接座和两个LPC连接座。每个连接座上的接口信号都是按照差分对形式组织并在开发板上对走线进行了等长匹配。差分走线的特性阻抗是100R,单端信号线的特性阻抗是50R,符合常用差分线和单端走线的特性阻抗标准。这些接口信号既可以作为差分对使用,也可以作为单端信号使用,接口信号的电平可以设置为LVDS信号电平或者2.5V CMOS、3.3V CMOS接口电平,使用起来非常方便。在使用LVDS输出接口或Vby1输出接口的情况下,TB-7K-325T-IMG开发板输出的是LVDS信号,这时候所用连接座中的信号按照差分方式组织。而在用作接收HDMI1.4A输入接口电路输出的数字视频信号的情况下,所用连接座中的信号电平设置为3.3V CMOS电平,以便跟HDMI1.4A接收芯片ADV7619输出信号的电平相匹配。在有一些应用场合,输入TB-7K-325T-IMG开发板的信号电平有可能是2.5V CMOS电平,可以通过TB-7K-325T-IMG开发板上相应的跳线将连接座的接口电平设置为2.5V,就能轻松实现接口电平的匹配,无需使用非常复杂繁琐的电平转换电路。通常使用的电平转换电路不但连线复杂,而且增加时钟和数据的延时,使得接口逻辑信号的时序恶化。

3.6微处理器控制电路

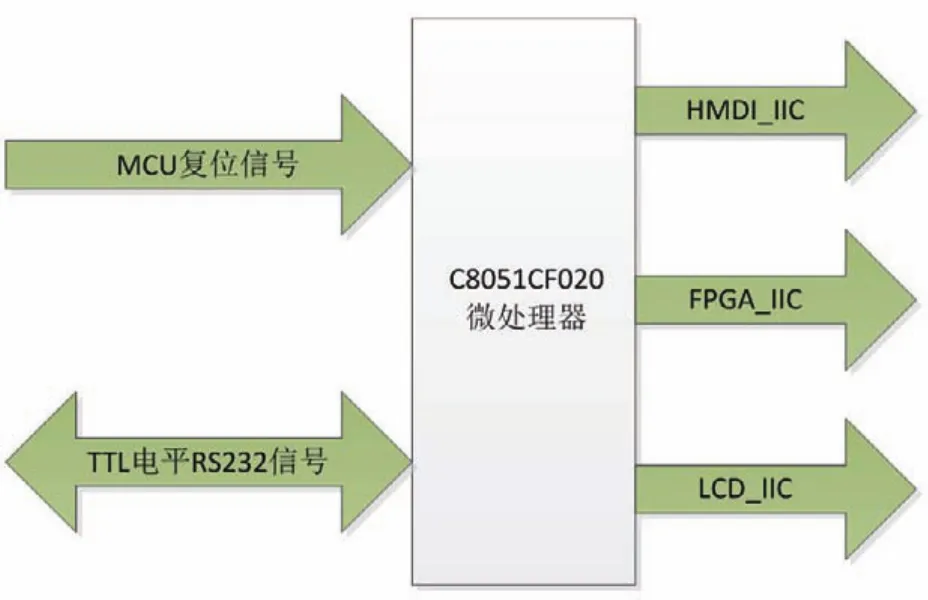

在整个FPGA验证平台中,共需要三组IIC控制信号。第一组IIC控制信号负责控制HDMI1.4A接口芯片ADV7619,完成对芯片内部寄存器的读写控制;第二组IIC控制信号负责控制TB-7K-325TIMG开发板FPGA芯片内部画质处理算法模块控制寄存器的读写;第三组IIC控制信号负责控制液晶显示屏的控制接口,通过液晶显示屏的IIC控制接口对内部的寄存器进行读写。这三组IIC总线的实现都是通过51系列微处理器C8051F020芯片使用软件模拟IIC时序实现的。通过软件模拟实现IIC总线时序的方式比较灵活,调整和修改都比较方便。C8051F020芯片内部集成了程序FLASH,无需外界程序存储器。C8051F020微处理器的调试通过JTAG接口,无需使用专门的硬件仿真器,调试方便工作可靠。C8051F020微处理器芯片只需外接石英晶体产生时钟信号就可以工作,外接电路简单,集成度高。C8051F2020微处理器芯片还具有丰富的端口,可以用来完成其他控制和显示功能,比如驱动外接的LED用作状态显示。如图4所示。

图4 微处理器控制电路框图

3.7RS232串行接口电路

RS2 32串行接口电路用来完成微处理器C8051F020和上位机之间的通信,方便通过外部的上位机向微处理器C8051F020传送控制信号。RS232串行接口逻辑通过微处理器内部的硬件电路实现,在FPGA验证平台电路板上采用MAXIM公司MAX3232E芯片完成RS232电平转换功能。MAX3232E芯片使用单一的3.3V电源,通过内部电荷泵的形式生成RS232接口需要的高电压。此外,MASX3232E芯片具有的非常好的抗静电特性,可以使得RS232接口可以适应非常恶劣的电气工作环境。如图5所示。

图5 RS232串行接口电路框图

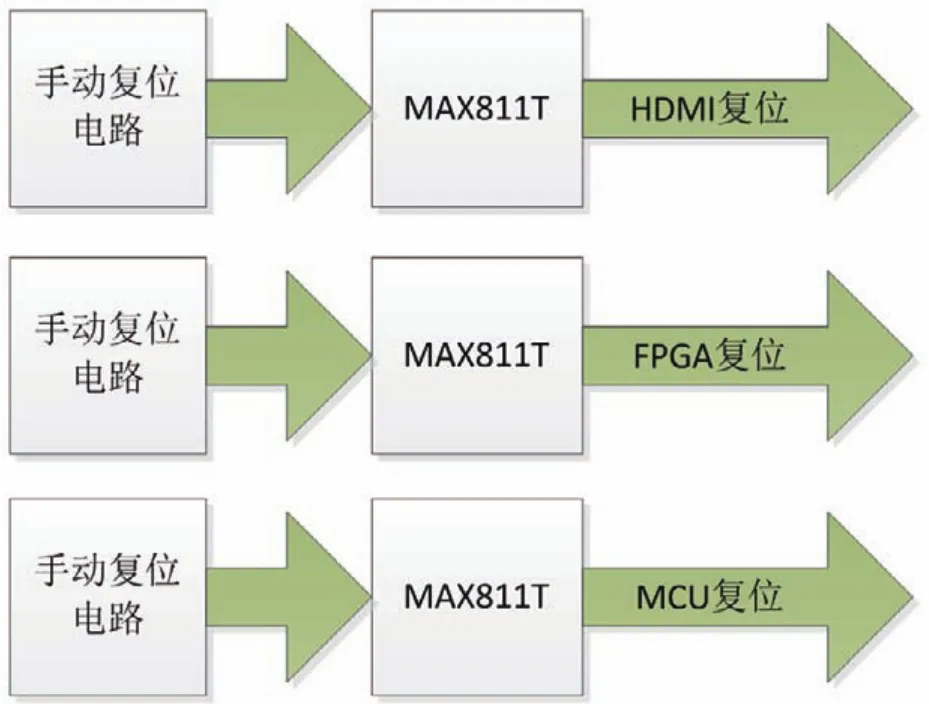

3.8复位电路和时钟电路

FPGA验证平台的时钟全部采用TB-7K-325TIMG开发板上的时钟资源,配合使用FPGA芯片内部的PLL和DLL资源生成所需的全部时钟信号。在FPGA验证平台上,需要三个复位信号,一个用来复位TB-7K-325T-IMG开发板FPGA芯片内部的逻辑;一个用来复位C8051F020微处理器芯片;一个用来复位HDMI1.4A输入信号接收芯片ADV7619。各个复位信号之间没有逻辑上的相关性,在功能上完全独立。为了调试方便,便于在使用过程中隔离问题,三个复位信号都采用专门的硬件电路生成。FPGA验证平台需要的三个复位信号都是低电平有效,复位信号生成电路采用了MAXIM公司设计的适用于3.3V电源环境的MAX811T芯片。MAX811T芯片只有四个引脚,具有上电复位功能和掉电复位功能,并有手动复位按键输入端,可以消除手动复位时的抖动。不论是上电复位还是手动复位输入情况,都能输出非常稳定的复位信号。如图6所示。

图6 MAX811T复位电路框图

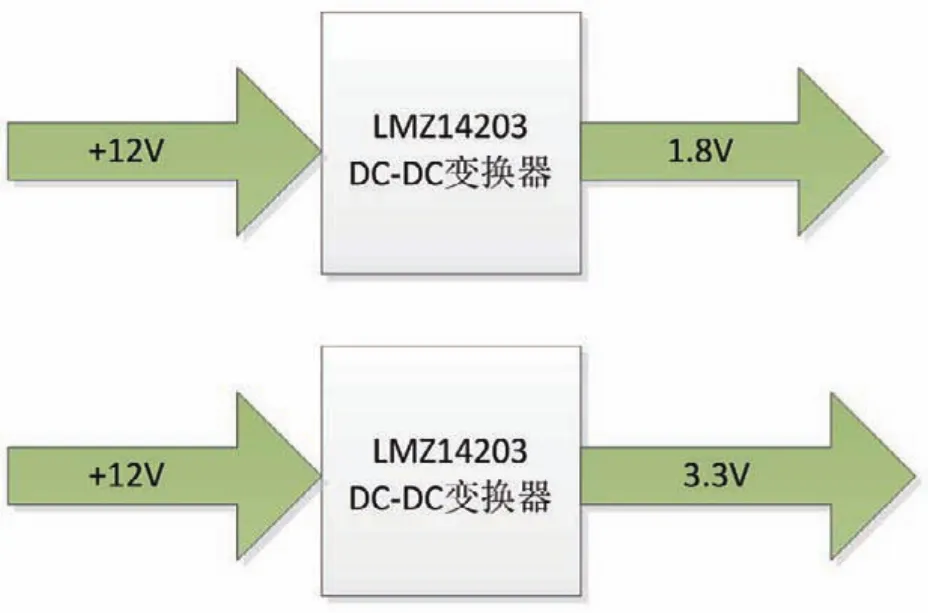

3.9电源产生电路

FPGA验证平台需要三种电源,包括3.3V电源、1.8V电源和12V电源。3.3V电源和1.8V电源主要用作数字逻辑电路部分的供电,12V电源则是显示屏接口的需要。在FPGA验证平台上,12V电源通过TB-7K-325T-IMG开发板的连接座引到扩展板上,而3.3V电源和1.8V电源则是使用两片TI公司的LMZ14203芯片从12V电源降压得到。LMZ14203芯片是内部集成滤波电感的同步整流型DC-DC变换器,具有外接元件少,输入电压范围广,输出电压范围广的优点,输入电压最高可达42V,输出电压最低可以到0.8V,最大可以输出3A电流。LMZ14203芯片还有过流保护功能,可以在很大程度上保护后面的芯片和走线不会因为过流损坏。LMZ14203在输出1.8V和3.3V这样的标准电压的时候,都有非常完整的参考设计电路和反馈环路补偿参考,设计比较方便。如图7所示。

图7 电源产生电路框图

4 结束语

上述的FPGA验证验证平台包含了常用视频算法处理需要的全部电路单元,功能全面、逻辑资源丰富、支持接口多、机械结构可靠,特别是Vby1接口和LVDS接口的支持,使得可以在多种液晶显示屏上验证算法,评估图像效果。基于上述优点,可见这款FPGA验证平台是视频画质处理算法验证非常好的选择,必将大大提高视频画质处理算法的验证品质和效率。

Riverbed SteelFusion延伸至云环境

Riverbed公司日前宣布,其超融合边缘解决方案Riverbed SteelFusion延伸至云环境,通过微软StorSimple为Azure、通过AWS存储网关为亚马逊AWS云服务提供支持。客户现在拥有更多灵活性和更多选择来实现远程办公地点的云数据存储,并且可将云作为二级存储层实现扩容和备份,或者与私有数据中心存储资源相互配合。

High-performance Image Processing Algorithm Generic FPGA Based Verification Platform

Yang Qiang

(Sichuan Changhong Electric Co.,Ltd.,Mianyang,621000)

Abstract:The article introduces a FPGA based universal hardware verification platform,it is designed specially for image processing algorithm verification.The platform has many advantages,such as general video source inputs,large logic capacity,abundant clock resources,abundant LCD screen interface,reliable mechanical structure.It is a fairly ideal FPGA verification platform for image processing algorithm verification application.

Keywords:Image processing algorithm;FPGA based verification platform;HDMI video input;Large screen LCD TV;LVDS output interface;Vby1 output interface

中图分类号:TN94,TN710

文献标识码:A文章编码:1672-7274(2016)03-0009-05

doi:10.3969/J.ISSN.1672-7274.2016.03.003