基于FPGA的电能质量监测装置设计

江 政,周 勇,陈雪美,吕娜伟

(郑州大学 电气工程学院,河南 郑州 450001)

基于FPGA的电能质量监测装置设计

江政,周勇,陈雪美,吕娜伟

(郑州大学 电气工程学院,河南 郑州 450001)

摘要:为了提高电能质量监测的精度和速度,设计了以FPGA为处理控制核心的监测装置.硬件部分主要包括信号采集单元、通信单元、电源单元等.软件方面,在FPGA上定制了NIOS II的嵌入式核心,优化了数据并行处理流程,在FPGA芯片内构建锁相倍频模块和FFT谐波分析算法模块,实现了对电能质量数据的同步采样和分析.测试表明,装置具有响应速度快、测量精度高和实时性能好的特点,符合国家关于电能质量监测的标准.

关键词:电能质量;现场可编程门阵列;快速傅里叶变换

0引言

近年来,电网中各种不对称性负荷、冲击性负荷和非线性负荷不断增加,对电能质量造成不同程度的影响,这些问题已经引起了供电企业和一些敏感用户的关注,实时和连续地监测电能质量指标是发现和整治电能质量相关问题的前提条件[1-3].现场可编程门阵列(field-programmable gate array,FPGA)作为专用集成电路领域中的一种半定制电路,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点[4].

从目前已有的基于FPGA的电能质量监测装置来看,文献[5]采用DSP+FPGA的设计方案,结合了两者的优点,但是结构复杂,不利于装置功能扩展,产品更新换代困难.文献[6]和文献[7]的嵌入式核心分别为uC/OS操作系统和ARM-IP核,两者均能协调装置各个单元的运行,但在FPGA中代码的移植和开发过程繁琐,占用较大片内资源,开发成本高.笔者仅用FPGA来完成了整个电能质量监测和分析过程,在FPGA中定制NIOS II的嵌入式核心,并给出详细检测结果.

1监测装置的硬件设计

监测装置主要由信号采集单元、核心处理单元、通信单元、电源单元及人机交互单元构成.硬件采用模块化设计方案,简化了硬件设计和FPGA的协调控制,整体设计如图1所示.

图1 装置的整体框图

1.1信号采集单元

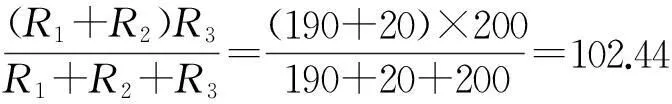

装置的电压电流转换电路如图2所示.设计中采用了两种电压输入范围,分别为100 V和250 V,以适应变电站等的PT二次侧电压和普通市电电压测量,按1 kΩ/V的比例外串限流电阻,调节电位器用来测量校准.

以R1、R2、R3的联接为例,当R2抽头调节至最左端时,Ua_100 V+测量端口串入的电阻为:

(1)

当R2抽头调节至最右端时,Ua_100 V+测量端口串入的电阻为:

(2)

图2 电压电流传感器应用电路图

由此可知,Ua_100V+测量端口串入的电阻调节范围为-2.56%~2.44%.电压电流传感器的跟踪电压输出范围为交流0~5 V.

模数转换器采用了ADI公司推出的新一代16位、8通道、同步采样、双极性输入、单电源供电的模数转换器AD7606[8].AD7606的应用电路如图3所示.

图3 AD7606接线图

在克莱默的眼里看来,河流是地球的血液,漂流木是滋养地球血液的营养,2011年时,当她连续3天看到大量原木源源不断在奴河中漂浮而过时,脑海里就出现了这个十分贴切的比喻。在人类开始清理河道为水上航运开道之前,大量的原木筏子和倒下的树木堵塞河流和河口的景象是很常见的。

1.2核心处理单元

核心处理单元主要由FPGA内的同步采样模块、NIOS II核模块、电能质量指标计算和分析模块和数据存储模块,其中同步采样模块由相位选择电路、过零比较电路和锁相倍频电路组成.

装置核心处理单元采用了Altera公司的EP4CE6E22C8N,锁相倍频电路由锁相环和分频电路构成,其作用是在采样时防止发生频谱泄漏和频率混叠,实现装置同步采样,减小FFT算法中的栅栏效应,提高整体的测量和计算精度.NIOS II核模块协调各个单元和模块之间的配合,完成整个电能质量监测和分析过程.

1.3通信单元

本装置主要通信方式为USB通信,将电能质量指标的分析结果传输到上位机或存储于U盘等大容量的存储器中.笔者选用CYPRESS公司的芯片CY7C68013A,该芯片集成了USB2.0收发器、增强的8051微控制器、SIE(串行接口引擎)和可编程的外围接口,具有12和480 Mb/s两种传输速率,可使用中断传输、控制传输、同步传输和批量传输4种USB传输方式.USB通信模块如图4所示.

图4 USB通信模块

USB 接口芯片采用了同步Slave FIFO方式,即从机方式, CY7C68013A芯片通过FD[15∶0]的16位双向数据总线与FPGA进行连接,FPGA提供的25 MHz外部时钟IFCLK的信号,因此其最大传输速度可达200 Mbps.FIFOADR[1∶0]用于选择FIFO的端点缓冲区,FLAGA、FLAGB、FLAGC分别用作CY7C68013A内FIFO的标志管脚,反映FIFO的当前状态,SLOE能够使FD的输出,SLRD与SLWR分别用作FIFO的读写选通信号.

通信单元还包括RS232模块和GPRS模块,RS232模块完成数据的串行通信,GPRS模块实现监测装置数据的远程传输和监控.RS232模块采用MAXIM公司生产的MAX232芯片,通信比特率设定为115.2 kbps.

2监测装置的软件设计

2.1嵌入式核心设计

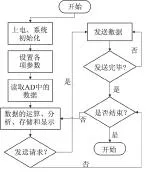

FPGA程序包括同步采样模块、NIOS II核模块、电能质量指标计算与分析模块和数据存储模块.具体流程如图5所示.

图5 主程序流程图

装置上电之后,存储芯片里面的数据会自动加载到FPGA中,然后在NIOS II的控制下对各个部分进行初始化,控制信号采集单元进行电压电流的数据采样,完成电能质量各项指标运算,最后将分析结果进行保存,判断数据是否需要发送和装置是否继续运行.

2.2FFT的算法设计

快速傅里叶变换(FFT)是进行谐波分析的关键[10].单片机和DSP芯片都是通过软件编程的方式编写FFT算法代码,DSP至多也是通过芯片内的MAC单元进行加速运算,实质上都还属于串行运算,它的算法复杂度是O(nlogn).然而FPGA通过并行的乘加单元进行FFT,只需要经过logn级的乘加法运算,运算速度相对提高了n倍.以8个点的FFT运算为例,若采用DSP芯片或单片机完成的话,要进行12次的乘加运算后才能得出计算结果,而通过FPGA的并行FFT电路实现的话,仅需3级乘加法运算,显著地加快了电能质量数据的计算速度.在FPGA中利用Verilog HDL语言编程实现FFT算法,可对输入信号进行快速的谐波分析,给出它们的幅值与相位.硬件上的并行结构和数据的并行处理流程,使监测装置的性能大大提高,克服了软件串行运行的缺点.

3测试结果及分析

3.1频率测量结果

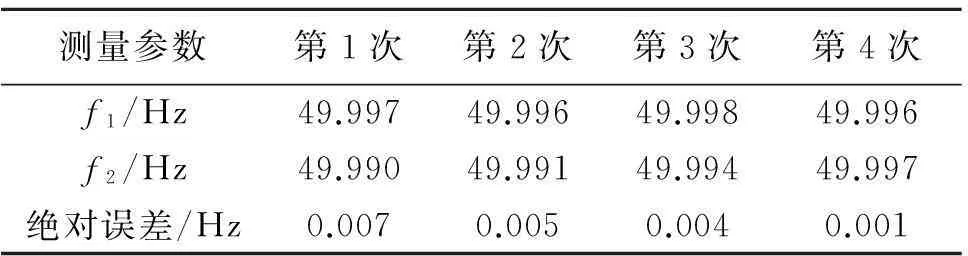

测试数据和绝对误差如表1所示,使用泰克TDS2012C数字示波器比较频率测量值.表中f1和f2分别为示波器测量值和监测装置测量值.

表1 频率测量测试表

由表1可知,监测装置与泰克示波器的频率测量的最大绝对误差为0.007 Hz,测量精度满足国家标准[11]的要求.

3.2电压有效值测量结果

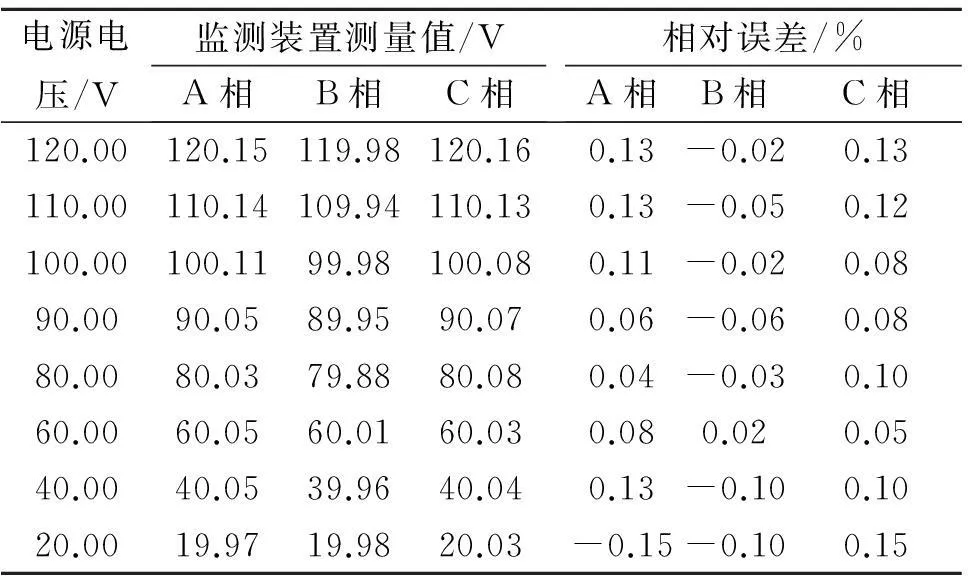

由于JCD4046测试电源的显示精度为三位半,测试以四位半胜利牌VC86E电压表的显示作为电压有效值的测量基准,测量结果如表2所示.

表2 三相电压测量测试表

由表2可以看出,三相电压的相对测量误差分布在-0.15%~0.15%之间,测量精度满足国家标准[12]对A级仪表的要求.

3.3电压谐波测量结果

限于JCD4060测试电源输出电压所含谐波分量的设定范围为2~21次,因此笔者对电压谐波测量的测试只检测电源输出的2~21次谐波分量,基波电压设定为100 V,参考测量仪器为Fluke345.测试结果表明,当Ub(各次谐波电压)≥1%UN(UN为100 V)时,最大误差为4.7%Ub,小于5%Ub;当Ub<1%UN时,最大误差为0.14%UN,小于0.15%UN;测量精度满足国家标准[13]对B级仪表的要求.

3.4电压序分量测量结果

根据JCD4060测试电源设定三相不对称电压,可计算出对应的电压序分量(理论计算结果).检测装置通过FFT计算出各相基波分量的幅值和相角,然后再计算出电压序分量(测试结果).两者相比,计算出电压不平衡度的误差分布在-0.2%~0.2%之间,满足国家标准[14]的要求.

4结论

设计的基于FPGA的电网电能质量监测装置,完成了各部分的硬件设计和软件编程.测试结果证明该装置具有响应速度快、测量精度高、实时性能好和操作简单的特点,不仅能够满足电能质量监测的要求,而且整个装置的集成度高,扩展性强,降低了硬件对设备升级的限制,方便以后采用新的算法和模块进行升级和更新,具有较高的实用价值.

参考文献:

[1]储珺,马建伟.基于小波变换的电能质量扰动信号的检测[J].电力系统保护与控制,2009,37(5):34-36,64.

[2]林海雪.现代电能质量的基本问题[J].电网技术,2001,25(10):5-12.

[3]肖湘宁.电能质量分析与控制[M].北京:中国电力出版社,2004.

[4]赵锋,马迪铭,孙炜,等. FPGA上嵌入式系统设计实例[M].西安:西安电子科技大学出版社,2008:26-28.

[5]王平,高阳,王林泓,等.基于DSP与FPGA的实时电能质量监测终端系统[J].电力系统保护与控制,2012,40(12):125-129.

[6]陈宏.基于FPGA的电能质量监测装置的研究[D]. 东北农业大学工程学院, 2010.

[7]袁斌,朱正伟,孙广辉,等.基于FPGA的电能质量监测系统[J]. 电源技术, 2014,38(12):2436-2437.

[8]周勇,朱明丽,杜霞,等.基于DSP+GPRS的远程在线电能质量监测系统设计[J].郑州大学学报(工学版),2014,35(5):23-26.

[9]Altera Corporation. Nios II世界上最多功能的嵌入式处理器[DB/OL]. 2008.

[10]解蕾,解大,张延迟.新型电能质量表的算法及实现[J].电测与仪表,2008,45(09):1-4,10.

[11]国家质量监督检验检疫总局,国家标准化管理委员会.电能质量.电力系统频率偏差:GB/T 15945—2008[S].北京:中国标准出版社,2008.

[12]国家质量监督检验检疫总局,国家标准化管理委员会.电能质量.供电电压偏差:GB/T 12325—2008[S].北京:中国标准出版社,2008.

[13]国家质量监督检验检疫总局,国家标准化管理委员会.电能质量.公用电网谐波:GB/T 14549—1993[S].北京:中国标准出版社,1993.

[14]国家质量监督检验检疫总局,国家标准化管理委员会.电能质量.三相电压不平衡:GB/T 15543—2008[S].北京:中国标准出版社,2008.

Design of a Power Quality Monitoring Device Based on FPGA

(School of Electrical Engineering, Zhengzhou University, Zhengzhou 450001, China)

Abstract:In order to improve accuracy and speed, a power quality monitoring device is designed with field-programmable gate array (FPGA) as the core of processing and controlling. Hardware of the device includes signal acquisition unit, communication unit, power supply unit, etc.. The software includes an NIOS II embedded core with optimized flow of data parallel processing and built-in phase-locked frequency multiplication module and FFT harmonic analysis module for the synchronous sampling and analysis of power quality data. Test results show that the device has advantages of fast response, high accuracy and satisfactory real-time performance, and conforms to the national standards of power quality monitoring.

Key words:power quality; field-programmable gate array (FPGA); fast Fourier transform (FFT)

中图分类号:TM711

文献标志码:A

doi:10.3969/j.issn.1671-6833.201505040

通讯作者:周勇(195—),男,河南信阳人,郑州大学教授,研究方向为电能质量分析与控制,E-mail:zhouy@zzu.edu.cn.

收稿日期:2015-05-26;

修订日期:2015-00-00

文章编号:1671-6833(2016)02-0029-04

引用本文:江政,周勇,陈雪美,等.基于FPGA的电能质量监测装置设计[J].郑州大学学报(工学版),2016,37(2):29-32.