基于以太网的多功能一体化数据采集系统

朱健军,倪有粮

(浙江工业大学 信息工程学院,浙江 杭州 310023)

基于以太网的多功能一体化数据采集系统

朱健军,倪有粮

(浙江工业大学 信息工程学院,浙江 杭州 310023)

摘要:针对目前机房集中监控系统产生的数据量大,且通用数据采集器功能单一、实时性差的问题,提出一款以京微雅阁SoC系列FPGA为核心设计实现的多功能一体化数据采集系统.通过分析通用数据采集器实时传输的难点,系统采用了软硬协同的设计方法,由Cortex M3实现系统的网络协议及数据调度算法,并利用可编程逻辑对异步串口及以太网接口进行硬件加速.它能够实现同时对多个接口进行数据采集,并通过以太网实时传输.实际系统的运行测试,验证了该平台的可靠性和实时性,并且系统具有较高的数据吞吐能力和灵活的扩展性.

关键词:以太网;数据采集;软硬协同设计;可编程逻辑门阵列

以4G/WiFi为标志的下一代无线网络,主要采用微基站的建设方式,以提升每个用户的接入带宽.微基站数量的成倍增长,需要采集、传输、处理的机房监控信息也呈几何级增长.而传统的机房集中监控系统中,动力环境监控、视频监控、门禁及智能防盗、能耗及节能管理等各成体系,监控信息零散,难以统一管理.随着机房基站运营维护工作的日益精细化,单一功能的数据采集系统已无法满足下一代无线网络机房深度运维的需要.目前,数据采集系统大多采用单片机[1]或DSP[2]作为控制核心.单片机的时钟频率较低,软件运行时间在整个采样时间中占很大的比例,实时性较差;DSP较擅长密集的乘加运算,很难完成复杂的硬件逻辑控制.近年来,国内外对于实时数据采集系统进行了大量研究[3-6],其主要集中于系统架构及数据采集算法的设计.同时,FPGA器件以其并行处理能力强,控制逻辑由硬件实现[7],及在高速、大容量数据采集领域的相关应用[8],也越来越受到了人们的关注.

数据实时采集及传输主要有两个难点:一是如何在有限的软件处理资源上,减小在兼顾实时性和准确性时耗费的大量计算时间;二是如何减小数据传输的延时,以提高系统的网络速度和数据采集的实时性.对于难点一,可以对系统的软硬件结构进行协同设计和优化,在保证准确性的基础上缓解软件的处理压力.对于难点二,可以对系统的网络及数据接口进行硬件加速,简化系统的硬件设计,以减小数据在传输上的延时.鉴于此,提出了一款以京微雅阁SoC系列FPGA为核心的数据采集系统.

1系统架构

该系统是一个数据采集和信息处理的一体化平台,在现有动力环境监控基础上,融合了智能防盗、温湿度、消防等模块,并采用了底层数据采集与上层业务应用分离的创新架构.由各类传感器实现对机房环境中大量数据的采集,并通过AI和DI等接口上传数据,由软件来实现系统复杂的控制和业务,系统结构如图1所示.

图1 系统总体结构图Fig.1 Structure of the global system

该系统采用的核心是京微雅阁高度集成化的SoC系列FPGA CME-M7,内含嵌入式处理器Cortex M3和大量可编程逻辑.设计的主要思想是将采集器的软件实现和硬件设计集中在单芯片中,以大大缩短数据和指令的传输延时.软件上,对数据的协议格式进行了简化设计并合理地定义数据调度方式,减小了协议处理的时间和系统的反应时间;硬件上,利用FPGA的并行处理能力,对主要的业务接口进行了硬件加速,不仅减轻了软件的处理压力,而且大大增强了业务口的并发性和实时性.

2系统软件设计

系统软件结构设计如图2所示,主要包括数据采集模块、控制模块、数据传输模块及告警模块.其中,数据采集模块包含多种类型的数据输入接口,用于采集多种类型的环境和设备状态数据.控制模块用于接收并处理由数据采集模块提供的数据,通过数据传输模块上传处理后的数据,并用于协调和控制多接口采集时其他模块的工作.数据传输模块用于上传控制模块处理后的数据.告警模块用于检测数据采集模块提供的数据是否正常,并且在数据异常时生成并上传告警信号.

图2 系统软件结构示意图Fig.2 Structure of the system software

2.1 控制模块

控制模块是系统软件最重要的组成部分,具体包括采集数据缓存队列、数据集成单元、数据封装单元、数据压缩单元、数据分级单元、高优先级输出队列、低优先级输出队列、实时输出队列、数据输出切换单元及数据传输频率设置单元,如图3所示.

图3 控制模块结构示意图Fig.3 Structure of the control module

数据集成单元,对原始数据进行集成化处理,以生成具有统一数据格式的有效净荷.集成单元分别针对不同来源和类型的原始数据预先设置了相应的描述原型,参数包括:数据采集时间参数,数据采集来源参数,数据类型参数,数据有效时段参数,如某项数据每1 ms采样一次,则该数据的有效时段为自采集时间起的1 ms内.经数据集成单元的整合统一后,弥补了多元化的采集数据在格式上的差异,有利于对采集数据进行识别、分析和处理.

数据分级单元,对经过压缩的数据包按照其重要程度进行分级,分别送入高、低、实时三个输出队列.分级单元根据数据采集来源参数,将特定数据来源的数据包置入特定输出队列,如将数据有效时段比较长的数据包置入低优先级输出队列,将数据有效时段比较短的数据包置入高优先级输出队列,而将数据有效时段即将过期的数据包置入实时数据输出队列.

数据输出切换单元,负责在三个队列之间进行切换,从而选择将哪个输出队列的数据送至数据传输模块进行传输.对于实时输出队列,一般要求在压缩后的数据包进入队列后立即发出,因此一旦该队列内出现有效传输数据,则立即向数据输出切换单元发送中断信号,数据输出切换单元立即将该队列中的数据送至数据传输模块;对于高、低优先级输出队列则采用基于权重的切换策略,即高优先级队列和低优先级队列分别具有不同的传输权重值,用两个输出队列中待传输的有效数据量乘上各自的权重值后,权重计算结果高的队列被切换至数据传输模块进行传输.

3系统硬件设计

3.1 系统硬件

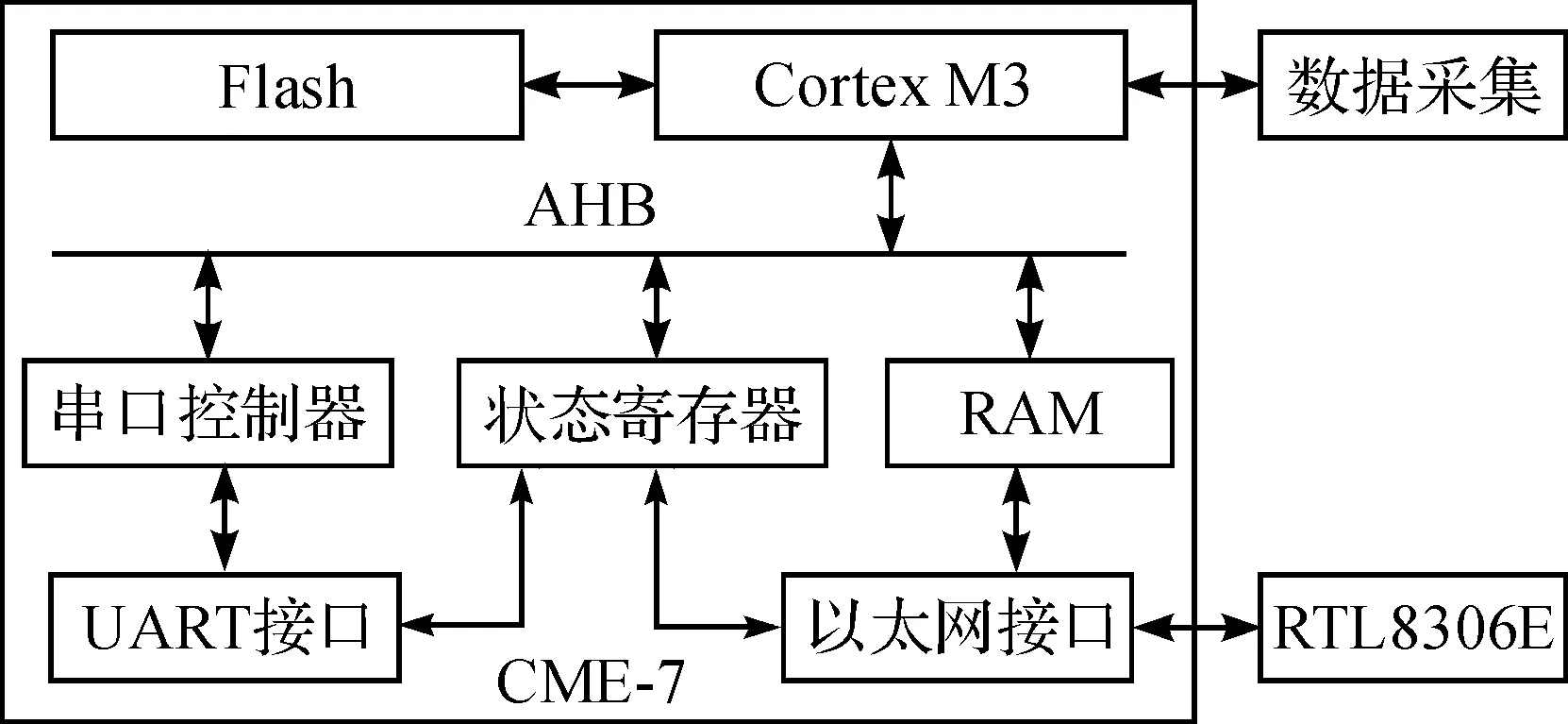

系统硬件结构如图4所示,依靠主控芯片CME-7 FPGA和交换芯片RTL8306E为主要硬件支撑.该CME-7 FPGA内嵌ARM Cortex M3处理器,具备齐全的外设驱动,并含有大量的可编程逻辑资源.系统主要由Cortex M3主控模块和通信接口模块构成.

图4 系统硬件结构图Fig.4 Structure of the system hardware

3.2 主控模块

采用的是京微雅阁M7系列FPGA为系统的核心芯片,支持300 MHz性能的ARM Cortex M3,200 MHz性能的FPGA逻辑,集成DMA控制器、DDR控制器、双12位1 MS/s ADC以及8 KB Cache等,丰富的逻辑资源和标准外设与处理器集成在一起,使系统变得更加稳定可靠.

系统中,Cortex M3与FPGA逻辑采用AHB方式进行通信,并以状态寄存器的方式来进行数据收发状态的告知.所有的寄存器被设在了FPGA侧,Cortex M3通过AHB总线查询或修改状态寄存器的值.由于Cortex M3与以太网、UART接口的通信方式非常类似,下面只讨论了Cortex M3与以太网接口的通信.

当FPGA中有一帧以太网数据被接收时,会将数据直接写入接收数据缓存,置位相应的以太网接收状态寄存器,并输出一中断脉冲至Cortex M3.Cortex M3通过AHB总线读取到相应的接收状态位有效时,立即将接收数据缓存中的数据通过AHB总线读出,并将其状态位清0.

当Cortex M3中有数据需要通过以太网发送时,会将数据通过AHB总线写入发送数据缓存,并置位相应的以太网发送状态寄存器.FPGA以轮询的方式读取各发送状态寄存器中的值,当读取到相应的发送状态位有效时,立即将发送缓存中的数据读出,并将其状态位清0.

3.3 通信模块

该模块主要完成以太网接口时序的设计和4路UART接口的拓展,实现系统的以太网、串口通信功能.对于以太网,硬件层采用RTL8306E,它是一款集成10/100 M交换、PHY功能的以太网交换芯片.FPGA中,以太网接口需要按RMII的时序与交换芯片进行通信,输入时在使能信号rmii_rxdv有效时,以时钟的上升沿对输入数据rmii_rxdi进行采样,具体时序设计如图5所示;输出时置高使能信号rmii_txen,以时钟的下降沿对rmii_txdo进行输出,具体时序设计如图6所示.经实际测试,系统能实现以太网联网功能,并支持Web服务;在多传感器并行采集数据且大数据量上传时,系统仍能保证不丢数据,且采样周期最小控制在2 s内.

由于串口的控制简单,目前大多数的数据采集设备都带UART通信接口.系统中,FPGA实现了4路串口,提高了系统集成度,并节省硬件成本.多路串口的数据采集,是在FPGA中设计一个串口控制器[9]去采集多路串口.系统充分利用了FPGA的并行处理能力,将串口控制器设计为4路串口的并行收发及相应RAM读写的硬件电路,即每路串口都有独立的RAM及串口收发模块[10],这样大大提高了串口通信的实时性.经实际测试,4路串口以最大波特率115 200 bps并行通信时,系统稳定可靠,且串口环回时间均小于8 ms.

图5 以太网接收接口时序设计Fig.5 Timing design of the Ethernet receive interface

图6 以太网发送接口时序设计Fig.6 Timing design of the Ethernet send interface

4结论

系统采用京微雅阁SoC系列FPGA作为该嵌入式数据采集系统的控制核心,以最简单的硬件结构实现目标应用,大大提升系统的稳定性;同时充分利用片内的可编程逻辑进行并行加速,增强了系统的实时性.经验证,系统能很好地满足实时监控和远程管理的设计需求,并已得到了现场应用.除基站机房外,该系统也可广泛应用于水利、金融、交通、煤炭、公安、监狱等部门的中心机房环境数据的监测.

参考文献:

[1]徐丹阳,童建平,隋成华,等.光栅光谱仪中的高速数据采集系统[J].浙江工业大学学报,2014,42(6):690-693.

[2]郭德亮,郭淑琴,鲍卫兵.基于突发光信号的高速数据采集系统的设计与研究[J].浙江工业大学学报,2010,38(1):46-48.

[3]FERRERO M F J, VALLEDOR L M, CAMPO R J C, et al. Low-cost open-source multi-function data acquisition system for accurate measurements[J]. Measurement,2014,55:265-271.

[4]NIETO J, DE A G, RUIZ M, et al. A high throughput data acquisition and processing model for applications based on GPUs[J]. Fusion engineering and design,2015,96/97:895-898.

[5]WANG Z L, ZHANG S S, CHANG J, et al. Adaptive data acquisition algorithm in Raman distributed temperature measurement system[J].Optik,2014,125:1821-1824.

[6]游雪峰,文玉梅,李平.以太网分布式数据采集同步和实时传输研究[J].仪器仪表学报,2006,27(4):384-388.

[7]王敬美,杨春玲.基于FPGA和UART的数据采集器设计[J].电子器件,2009,32(2):386-390.

[8]ZHENG W, LIU R, ZHANG M, et al. Design of FPGA based high-speed data acquisition and real-time data processing system on J-TEXT tokamak[J]. Fusion engineering and design,2014,89:698-701.

[9]韩德红,张显才,李向东.基于FPGA的串口控制器设计与实现[J].空军雷达学院学报,2008,22(2):113-116.

[10]刘凤新,赵坚固.基于FPGA的多路并行独立串口的实现[J].仪表技术与传感器,2010(11):44-47.

(责任编辑:刘岩)

An integrated multi-function data acquisition system based on the Ethernet

ZHU Jianjun, NI Youliang

(College of Information Engineering, Zhejiang University of Technology, Hangzhou 310023, China)

Abstract:In current data acquisition system, data produced by the concentrated monitor system is huge, the function of general data acquisition equipment is single, and the real-time performance is bad. In this paper, an integrated multi-function data acquisition system is proposed based on Capital Microelectronics SoC series FPGA. By analyzing the difficulties of real-time transmission in general data acquisition equipment, a methodology of hardware-software co-design method is applied in the whole system, in which the network protocol and data scheduling algorithm are implemented in Cortex M3,and the programmable logic is used to accelerate the asynchronous serial interfaces and Ethernet interface. The system is used to collect data from multiple interfaces,and implement real-time transmission in the Ethernet. The running test in the real system shows that the platform is reliable and has high real-time performance. It also has a high data throughput and flexible expansibility.

Keywords:Ethernet; data acquisition; hardware-software co-design; FPGA

中图分类号:TP274.2

文献标志码:A

文章编号:1006-4303(2016)01-0058-04

作者简介:朱健军(1974—),男,浙江义乌人,高级工程师,研究方向为物联网,E-mail:zjj@zjut.edu.cn.

基金项目:国家火炬计划项目(2013GH010615)

收稿日期:2015-05-18