可编程器件Microblaze的应用与实现

刘军伟(中航工业西安航空计算技术研究所,西安,710065)

可编程器件Microblaze的应用与实现

刘军伟

(中航工业西安航空计算技术研究所,西安,710065)

摘要:MicroBlaze是基于Xilinx公司FPGA 的微处理器IP核,可以利用其便捷性优化嵌入式系统设计,同时简化硬件电路,提高系统性能。

关键词:MicroBlaze;FPGA;IP核

Application and Realization of Microblaze Programmable Devices

Liu Junwei

(AVIC Computing Technique Research Institute,Xi’an,710065)

Abstract:MicroBlaze is based on the microprocessor IP core of Xilinx company,it can utilize the convenient optimization design of embedded system,and simplify the circuit and improve the performance of the system. Keywords:MicroBlaze;FPGA;IP core

0 引言

随着可编程逻辑器件FPGA在信号数据处理领域日益广泛的应用,以FPGA为核心的架构,诸如FPGA+PowerPC、FPGA+DSP等架构被广泛采用,如何有效的利用FPGA自带的内部资源完成简单的控制功能,从而减轻处理器的负担,提高系统性能成为设计者设计时需要考虑的问题。

本文介绍了Xilinx公司FPGA的Microblaze IP核的体系结构和性能,同时基于Microblaze IP核的基础上,介绍了其在实际应用上的实现事例。

1 Microblaze的体系结构

MicroBlaze是基于Xilinx公司FPGA 的微处理器IP 核,和其它外设IP 核一起,可以完成可编程系统芯片(SOPC) 的设计。MicroBlaze 是Xilinx 的32 位RISC 软核嵌入处理器,在ISE/XPS(EDK+SDK)开发环境中进行设计,广泛适用于Spartan 和Virtex 系列的FPGA。一个FPGA 芯片内部可以使用主从两个或多个MicroBlaze处理器,而FPGA 最大的特点就是能够缩短产品开发的周期,它的可编程配置特性可以将系统开发的风险降到最低。而Xilinx 公司的MicroBlaze 软核处理器的优点在于,不像ARM是由固定的硬芯片来实现,用户可以根据实际系统的需求添加必要的外设来实现基于MicroBlaze 的嵌入式可编程片上系统,从而提高了设计的灵活性。MicroBlaze微处理器采用RISC 架构和哈佛结构的32位指令和数据总线,内部有32个32位通用寄存器,2个特殊寄存器:PC指针和MSR状态标志寄存器,可以按照字节、半字和字三种方式访问寄存器。其中独立的32位OPB指令总线和数据总线,可以访问片外存储器及其他外设,独立的32位LMB指令总线和数据总线,直接连接到FPGA内部的RAM上进行高速的读写操作。简单来说,通过MicroBlaze可以访问可以全速执行存储在片上存储器和外部存储器中的程序,并访问其中的数据。MicroBlaze的IP核结构框图如图1所示。

图1 MicroBlaze的IP核结构框图

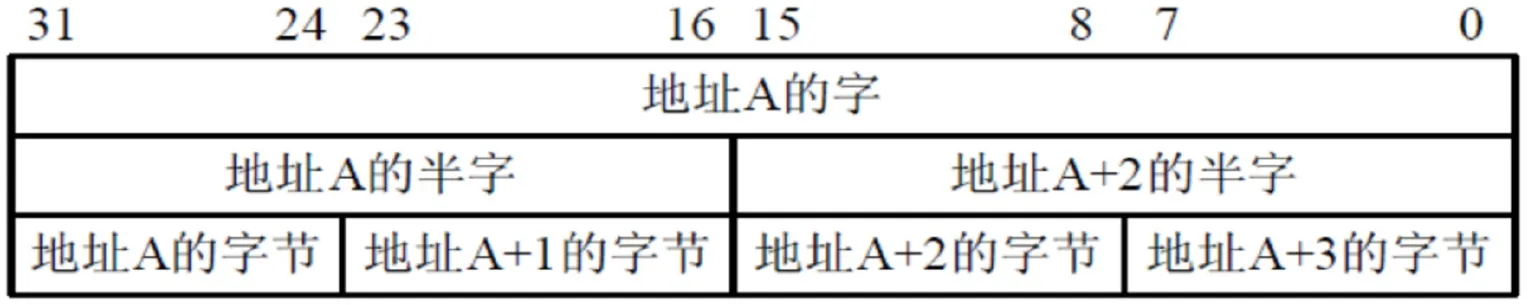

MicroBlaze处理器同时具有8个输入和8个输出快速单一链路接口(FSL)。FSL通道是专用于单一方向的点到点的数据流传输接口。FLS和MicroBlaze 的接口宽度都是是32位。每一个FSL通道都可以发送和接收控制或数据字。MicroBlaze是一种大端存储系统处理器,使用大端的格式来访问存储器,具体详格式见图2。同时MicroBlaze 可以响应软件和硬件中断,进行异常处理,通过外加控制逻辑,可以扩展外部中断,可通过FPGA的JTAG接口来调试处理器系统。

2 Microblaze微处理器的OPB总线与PLB总线

图2 MicroBlaze的大端数据格式框图

Microblaze微处理器构建系统时,需要一些必要的IP核,其中比较重要的就是OPB和PLB总线接口。

2.1片上外设总线(OPB)

内核通过片上外设总线(OPB)来访问低速和低性能的系统资源。OPB是一种完全同步总线,它的功能处于一个单独的总线层级。它不是直接连接到处理器内核的。OPB接口提供分离的32位地址总线和32位数据总线。处理器内核可以借助“PLB to OPB”桥,通过OPB访问从外设。作为OPB总线控制器的外设可以借助“OPB to PLB”桥,通过PLB访问存储器。

2.2处理器本机总线(PLB)

PLB接口为指令和数据一侧提供独立的32位地址和64位数据总线。PLB支持具有PLB总线接口的主机和从机通过PLB信号连接来进行读写数据的传输。总线架构支持多主从设备。每一个PLB主机通过独立的地址总线、读数据总线和写数据总线与PLB连接。PLB从机通过共享但分离的地址总线、读数据总线和写数据总线与PLB连接,对于每一个数据总线都有一个复杂的传输控制和状态信号。为了允许主机通过竞争来获得总线的所有权,有一个中央判决机构来授权对PLB的访问。

3 Microblaze的开发工具

Xilinx公司提供了EDK嵌入式开发套件可以进行MicroBlaze IP核的开发。EDK中还带有一些外设接口的IP核,如LMB、OPB总线接口、外部存储控制器、SDRAM控制器、UART、中断控制器、定时器等。利用这些资源,可以构建一个较为完善的嵌入式微处理器系统。在FPGA上设计的嵌入式系统层次结构为5级。可在最低层硬件资源上开发IP核,或利用已开发的IP核搭建嵌入式系统。软件方面需开发IP核的设备驱动、应用接口(API)和应用层(算法)。通过标准总线接口(LMB总线和OPB总线的IP核),MicroBlaze就可以和各种外设IP核相连。EDK中提供的IP核均有相应的设备驱动和应用接口,设计者只需利用相应的函数库,就可以编写自己的应用软件和算法程序。对于用户自己开发的IP 核,需要自己编写相应的驱动和接口函数。

4 Microblaze的实际应用事例

4.1设计思路

使用硬件开发测试逻辑,将作为测试设备激励源的模块的发送接口和模块的接收用户主机接口连接,同时使用线缆将两端的接口连接。在Microblaze的基础上开发外部激励源中测试逻辑,功能如下:

(1)外部激励源母板集成模块连接器和MAX3232ESE驱动器,驱动器实现作为测试设备的UART串口引出;

(2)逻辑布随机码并按照约定格式并发送,单次发送启动均由逻辑集成的MicroBlaze处理器控制;

(3)之后逻辑等待FC接收数据,接收到数据后,由逻辑进行比对,将正确和错误结果使用不同的中断上报给MicroBlaze处理器,处理器响应中断,并进行统计技术,并通过UART接口现实输出。

具体逻辑架构图如图3所示:

图3 逻辑开发框图

4.2测试流程

具体测试流程如下:

(1)模块上电后,处理器运行,并置软件计数变量为0,之后读取链路状态(如果用户链路状态为闭环模式,则也需要读取用户链路状态);

(2)在告诉链路状态均正常的情况下,发送第一次测试命令

到测试逻辑,测试逻辑启动伪随机码布码逻辑,并在发送的同时填入到比较缓冲中;

(3)等待接收数据,在数据接收完成后,将接收缓冲中的数据和测试逻辑中的比较缓冲中的数据通过硬件进行读取比较,比较完成后,根据结果上报中断到处理器;

(4)处理器响应中断,并增加相应的技术指,并按照约定频率(比如10次正确输出一次,单词错误输出并停止测试)通过UART输出测试结果;

(5)通过PC端的超级中断观察串口输出结果,并以此作为合格判据。

5 结束语

本文对FPGA 和MicroBlaze架构、工作原理及具体应用的实现方法分别进行了介绍。通过阐述,可知采用Xilinx公司FPGA的MicroBlaze 进行嵌入式系统设计,可以简化硬件电路同时提高系统性能,在应用上具有一定的价值。

参考文献

[1] 刘永健.软核嵌入处理器MicroBlaze [J].计算机与网络,2012.

[2] 何宾.王瑜. 基于Xilinx MicroBlaze多核嵌入式系统的设计[J].电子设计工程.2011.

刘军伟,中航工业西安航空计算技术研究所,工程师

作者简介