更多核心,更强总线

张平

一般来说,人们都很关注处理器的核心数量,比如四核、八陔等,但是又有谁知道支撑处理器核心数量、GPU规模的“幕后精英”呢?最近ARM发布了全新的CCI-550总线,可以支持更多的处理器核心以及CPU、GPU的完全一致性。

说起ARM,大家的第一反应多半会想到手中智能手机里的处理器。比如双核心的苹果A9、八核心的高通骁龙810以及最新拥有十核心的联发科Helio X20。在这些处理器中,人们津津乐道的往往是它们的核心数量、GPU规模,但是对另外一个决定处理器基本规格和允许规模的重要部件——总线,却没有太多了解。刚好,前段时间ARM发布了全新的CCI-550总线,为ARM未来处理器拥有更强性能,更多核心,迈向更广泛的应用空间埋好了伏笔。下面我们就来了解一下这款全新的总线。

CoreLink,串联ARM的大小核心

说起总线很多人会想到PC中的HT总线、DMI总线、PCI-E总线等等。顾名思义,总线就是不同设备间的连接线,它可以使一个系统的不同部分通过一种标准化的通道连接在一起,更好地实现设计所需的功能和目的。

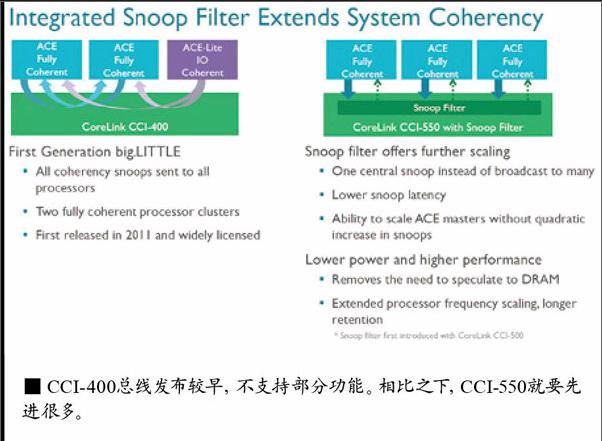

总线可谓是处理器中最重要的部分之一,在移动处理器上自然也不例外。目前在ARM架构的移动处理器中,广泛使用的是CoreLink CCI-400总线(下简称“CCI-400”)。令人惊讶的是,CCI-400的发布时间竟然是五年前的2010年11月11日。当时CCI-400发布的主要目的是为了充分发挥Cortex-A15和Mali-T604的性能,提高系统的吞吐能力和数据传输能力,降低传输瓶颈(虽然Cortex-A75的产品大约在三年后才正式发布)。为了达到这个目的,CCI-400设计了一个全新的可配置、无闭塞性、低延迟、低功耗的NIC-400网络,串联了处理器内部各个重要的部分,并且还加入了细链路设计,缓解内部布线拥挤。在内存方面,CCI-400搭配的DMI-400内存控制器支持DDR2、LPDDR2以及DDR3内存,可以为处理器提供充足的带宽。具体到产品来看,CCI-400总线大约从2011年开始逐渐应用到ARM架构的处理器上,从Cortex-A9到Cortex-A15,乃至目前最主流的Cortex-A53和Cortex-A57,甚至最新的Cortex-A72,者隅能看到CCI-400总线的影子。

不过CCI-400虽然经典,但在长达五年的时间中,处理器尤其是移动处理器有了高速发展,使得CCI-400无法支持许多全新的特性。同时CCI-400在很多关键特性上的缺失还使得ARM无法进入更高端的服务器处理器市场。因此,ARM决定研发一款全新的CoreLink总线,使得ARM能够继续在未来保持领先的优势。这个全新的产品,就是接下来要介绍的CCI-550总线。

实际上,在ARM发布CCI-550总线之前,曾于2015年2月推出了一款CCI-500总线。相较之下,CCI-550基本上继承了CCI-500的所有特性,并且加入了一些更新的关键性功能。因此,本文就不再重复CCI-500的功能,只针对CCI-550进行介绍。

嗅探过滤器——同步数据更高效

说起CCI-550的核心改变,怎么也绕不过全新的嗅探过滤器。在提及这部分内容之前,我们先来看看在多核心处理器之间的通讯和同步有哪些方式。

如果一个总线上连接了4个对等的处理器内核,这就意味着4个处理器内核都有能力修改、获取存储系统中的数据。但是每个处理器又有自己的缓存和关键性数据表。当某一个处理器修改了内存中的数据时,别的处理器缓存中如果有对应的数据,那么也应该修改才能保持同步。这个时候,应该如何让別的处理器也知道某个数据已经修改了呢?

有一种方法是这样的:让修改数据的那个处理器给出广播说明情况,通知其他处理器即可。简单来说,如果有四千人,每个人都在做“10+5+3”的算术题,但是有一个人想改成计算“10+6+8”,那么这个人需要拿着小喇叭告诉剩余的三个人——快別算“10+5+3”了,我们算“10+6+8”吧——这样其他三个人就知道了将自己的题目改成最新的即可。

这种方式叫做广播,简单来说是当某个处理器核心每一次更改数据时,都会通过总线告诉别的处理器:“我改数据了”。然后其他处理器根据广播内容修改数据并保持同步。广播看起来实现方法很简单,但问题也不少。因为高速运行的处理器资源本身就很紧张,如果某些处理器老是不停地等待别的处理器发出的广播通知,整体效率显而易见就会降低。再说处理器不断发出广播信息修改数据,并且无差別地发给所有处理器(即使某些处理器并不需要这个通知),也会带来信息的冗余和臃肿。

从应用角度来看,如果处理器核心数量少于4个,广播还算一种不错的解决方法,但是如果处理器核心数量高于6个甚至8个,广播效率就很低下了。现在在很多新的处理器中,核心数量都提升到了8个甚至10个,尤其是在big.LITTLE架构流行后。这样一来,广播就不怎么靠谱了。于是ARM改变了策略,在全新的CCI-550和CCI-500中改用了嗅探过滤器。

什么是嗅探过滤器呢?简单来说,ARM为多核心处理器增加了一个“通信员”并依靠这个“通信员”传递数据、同步内容。还是上面的例子,当四个人都在计算“10+5+3”的时候,有一千人告诉位于中间的通信员,题目改成计算“10+6+8”了。于是通信员就去挨个问:题目改了,你知道吗?如果回答的是“知道”,那么通讯员就走了;如果回答的是“不知道”,那么通讯员就告诉他实际内容。这样一来,既提高了效率,又节约了能耗,还节省了总线占用,一举多得。

根据目前的资料来看,全新的嗅探过滤器能够同时和所有缓存、核心进行通信,整体延迟更低,扩展性能更强,同时最多还能节约0.1瓦的能耗。这还不是最重要的,更重要的是它为更多核心的ARM架构处理器铺平了道路。endprint

核心扩展——支持最多24核心

说到多核心处理器,尤其是服务器级別的低功耗多核心处理器,一直是ARM梦寐以求的市场。服务器市场不仅利润高,关键是ARM目前的架构也很符合其需求。举例来说,随着移动计算技术的发展,很多用户在移动设备端往往只执行轻负载应用,比如邮件收发、信息推送、短消息互联互通等,这些轻负载应用在服务器端并不需要太强大的单核心性能,但是对多任务和多核心要求很高。ARM的处理器相比英特尔的“重型架构”处理器,其单核心性能不够出色,但是胜在功耗低、核心数量可以做得很多,刚好契合这一需求。因此ARM一直以来都想打入这个市场。

但是之前的CCI-400总线最多支持2个CPU簇,每个CPU簇最多支持4个CPU核心。这样一条总线最多支持8个CPU核心,如果要使用更多的CPU核心的话,那么就得布置更多的总线,这样一来总线之间的互通又成为了问题。但是在CCI-550上,ARM允许一个总线最多支持6个CPU簇,每个CPU簇依旧是4个CPU核心,这样最多就能支持24个CPU,使得ARM的服务器梦想又前进了一步。

此外,为了配合更多核心的产品,CCI-550最多可搭配六个DMC-500内存控制器实现对六通道内存的支持,内存寻址方面最多支持48bit,完全可以满足服务器对内存容量的需求了。内存速度最高支持LPDDR4-4267,兼容LPDDR3-2733,性能方面最高可提升27%,能够降低25%的CPU平均延迟。其他方面,CCI-550可以支持最多三个系统主界面,六个AC巨端口,基本能满足未来很长一段时间的需求了。

完全一致性支持——支持GPU和CPU异构计算

CPU和GPU的异构计算在很多场合都被反复提及。虽然从理论上来说,CPU更适合相关性复杂的单线程任务以及逻辑计算,GPU更适合相关性较弱的并行计算,但是如何使这两种计算模式有机并且高效率地结合在一起,一直都是业内的难题。尤其是AMD在APU上投入了这么多年的精力,目前也没有带来特別有效的商业和应用模式。不过技术终究是在发展的,在CCI-550中,ARM就为了支持异构计算,加入了对完全一致性的支持。

所谓完全一致性,是指CPU和GPU在存储数据时,数据在内存中使用完全单一的内存地址空间,不需要额外的数据管理模块,也不需要数据的拷贝和转移。传统的CPU-GPU结构中,CPU有自己的内存,GPU有自己的显存。数据在计算时需要从CPU发包到GPU,GPU计算完成后再发回数据,效率较低。但是在全新的完全一致性模式下,CPU和GPU共享相同的内存存储空间,数据的拷贝和更改都在一个空间内进行,大大提升了效率。

CCI-550对完全一致性的支持,使得ARM可以在HAS、Open CL 2.0等编程模型下有更好的表现,并且可以实现对应用的异构加速。不过目前ARM的Mali-T800系列GPU还不支持全部的完全一致性,现在只能支持I/O一致性。ARM预计推出的下一代代号为“Mimir”的GPU就能够支持完全一致性了,到时候用户有可能在手机上享受到HAS异构计算的加速效果。

什么时候才能用到CCI-550?

问题来了:什么时候用户才能享受到CCI-550带来的变化呢?据估计,CCI-550应该在2016年底配合全新的工艺在新的处理器中得到应用。具体到实际产品诸如手机、平板电脑上,可能需要等到2017年中期了——也就是说,用户还得大概等待一年半左右。从目前的情况来看,CCI-550整体技术和设计都比较先进,因此未来很长一段时间,CCI-550应该都将存在于我们的移动设备中。endprint