基于VPX的SRIO通信模块设计

谷晓鹏,杨玉亮,张 然(.海军指挥所,北京0084;.中国船舶重工集团公司第七二四研究所,南京53)

基于VPX的SRIO通信模块设计

谷晓鹏1,杨玉亮2,张然2

(1.海军指挥所,北京100841;2.中国船舶重工集团公司第七二四研究所,南京211153)

摘要:针对VPX下SRIO通信的需求,提出一种封装SRIO通信接口的方法,设计并实现了一种SRIO通信模块。SRIO通信模块采用软件模块化设计思想,在SRIO通信接口的基础上设计PowerPC板CPU之间的通用的数据通信方式,可实现PowerPC板内、板间的数据通信。该模块以库函数形式实现二进制重用,可移植于任意PowerPC程序设计中,实现通信参数的可视化配置,有利于软件结构化、模块化设计。测试分析表明,该模块具有良好的性能和二进制可重用性。

关键词:通信模块; VPX; Serial RapidIO;软件模块化

0 引言

随着技术的进步以及应用性能需求的不断提高,雷达系统各单元之间的通信对带宽要求不断提高。VPX各单元之间的Serial RapidIO(以下简称SRIO)总线由于传输带宽的优势,应用越来越广泛,因此SRIO通信越来越普遍。但是,直接使用SRIO通信接口函数存在很多不足:

(1)SRIO通信相关接口函数多,使用不方便,每个软件人员需花大量时间学习其使用方法;

(2)SRIO通信需要对CPUID、地址、门铃等进行约定,需各个软件相关人员进行讨论确定;当CPU之间需增加新的报文或者已有CPU与新的CPU进行通信时,整个项目相关人员可能都需对通信模块程序进行修改;

(3)程序运行过程中,SRIO通信出现收不到数据或者数据错误时很难进行定位和排查;

(4)每个软件人员对SRIO通信进行设计时未对自身程序的通信速度、稳定性等进行系统的测试,很难保证通信的可靠性。

针对上述问题,提出一种封装SRIO通信接口的方法,设计并实现了一种SRIO通信模块。该模块以库函数形式实现二进制重用,可移植于任意PowerPC程序设计中,实现通信参数的可视化配置,有利于软件结构化、模块化设计。

1 通信架构

VPX机箱中同一PowerPC板各单元之间通过Serial RapidIO高速串行总线进行互连,每个CPU都有一个SRIO接口,通过switch路由于背板。不同PowerPC板间通过机箱中交换板进行互连[1],如图1所示。

VPX6-8640D的每个RapidIO设备(8640D cpu)都有inbound SRIO memory windows,允许其他RapidIO设备来访问该设备。同时,还有outbound SRIO memory windows,允许该RapidIO设备去访问其他设备[2]。

图1 SRIO通信架构

2 模块设计

2.1需求分析与设计

SRIO通信时,首先需要对CPUID、地址、门铃等进行约定。当通信需求改变时,整个项目相关人员可能都需对通信模块程序进行修改。针对该问题,本模块设计并实现了一种通信参数的可视化配置方法,通过该方法同时增加了模块的通用性和可移植性

SRIO通信相关接口函数多,使用不方便,每个软件人员需花大量时间学习其使用方法。本模块提出一种封装SRIO通信接口的方法,有效地解决了该问题。

2.1.1通信参数的可视化配置方法

(1)配置文件设计

参与通信的CPU采用统一配置文件,完成对CPUID、地址、门铃等的配置。使用门铃作为每条配置信息的唯一标识。通信过程中,使用门铃完成配置信息的索引,进而实现CPU间数据到对应地址的映射。

各CPU的发送和接收窗口个数均有一定限制(发送窗8个,接收窗4个),需采用地址偏移方式实现多数据报文的通信。配置文件设计过程中,加入发送窗口和接收窗口建立标识,并通过地址偏移和门铃的设置实现窗口的复用。

每个CPU可配置多条配置信息,每条配置信息又可实现多种报文的通信。配置信息结构如图2所示。

图2 配置信息结构图

(2)可视化界面设计

参数配置程序用于生成或修改配置文件,效果如图3所示。

设置配置文件参数过程中,当参数设置不合理时将弹出提示对话框,例如地址越界、地址不对齐、地址重用等错误。

2.1.2SRIO通信接口封装方法[3-4]

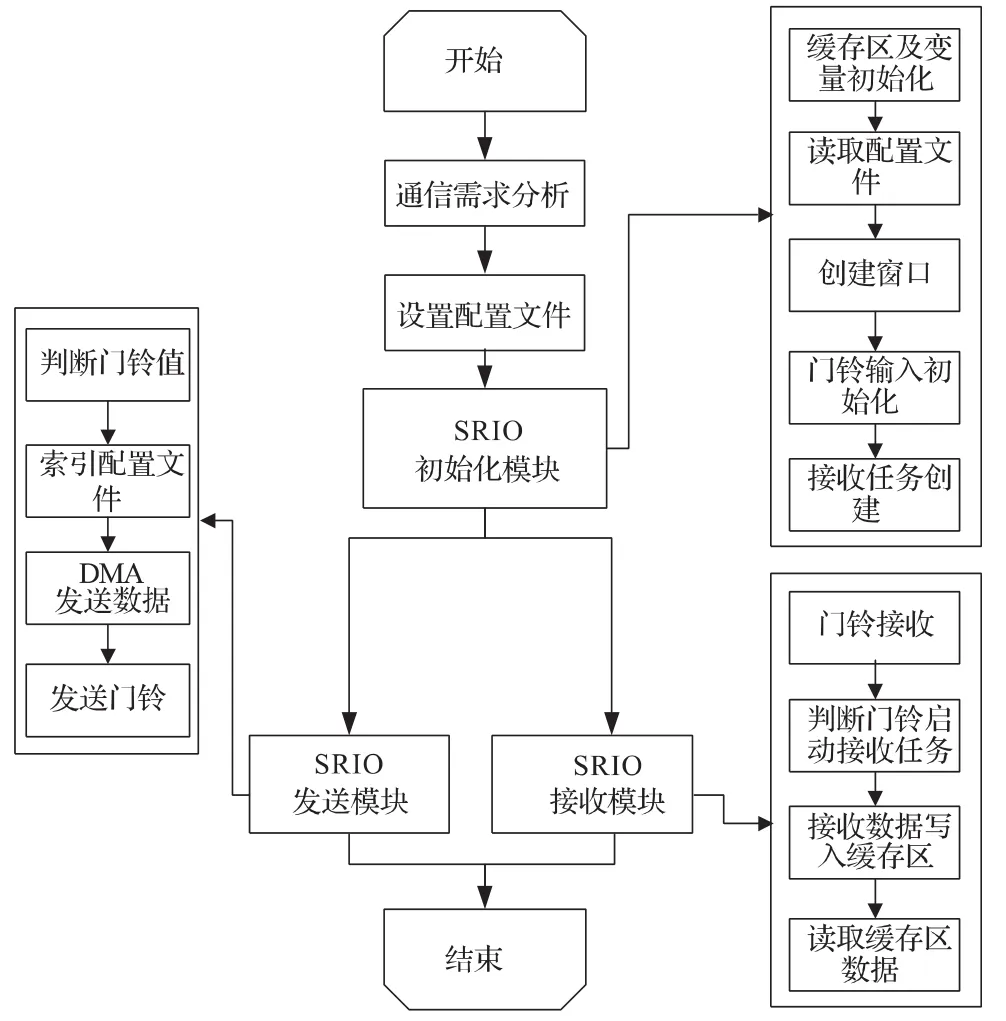

该模块设计提供3个功能模块: SRIO初始化模块、SRIO发送模块和SRIO接收模块,分别对应3个功能接口函数。通信流程如图4所示。增加新的报文或者增加新的通信CPU时仅需对配置文件进行修改。

图3 配置文件设置效果图

图4 SRIO模块通信流程

(1)SRIO初始化模块

初始化模块主要实现以下功能:

·SRIO接收窗口和发送窗口的创建;

·SRIO接收缓存区、信号量、相关变量的初始化;

·SRIO门铃输入的初始化,门铃中断处理函数的创建;

·SRIO接收任务的创建。

(2)SRIO发送模块

该模块设计流程为:

·将门铃作为唯一标识,从配置信息中查找到对应的发送地址;

·通过DMA传输方式,将待发送数据传输至发送地址中,完成数据到总线的映射;

·发送门铃中断通知接收端数据已更新。

(3)SRIO接收模块

该模块设计流程为:

·门铃中断输入函数接收门铃;

·判断门铃值,启动门铃对应的接收任务;

·接收任务读取对应接收地址中的数据值接收缓存区,接收地址通过门铃值索引得到;

·通过读取缓存区接口函数,读取缓存区数据。

2.2可靠性设计

模块设计中主要采取了以下几种方法提高模块的可靠性:

(1)模块编译成库函数的形式,仅提供给用户库函数和头文件;

(2)通过编译器的强类型检查,接口参数使用错误时,报送错误信息,避免运行过程中产生通信错误或者模块崩溃;

(3)配置文件设置过程中,对各配置参数的有效性进行检查,避免了配置的设置参数无效产生通信错误;

(4)通信过程中,数据包的最后16位作为校验位,以检验数据包的有效性。

3 主要特性

(1)可重用性

该模块通过库函数形式,可以实现二进制重用,用户无需对模块代码进行学习和了解,仅通过接口函数的调用,即可完成相应的SRIO通信。

(2)可靠性

模块设计过程中充分考虑了可靠性的设计。开发完成后,对模块完成了功能、性能和异常的测试,保证软件具有成熟性、容错性。

(3)可维护性

通信过程中出现故障时,通过检查接口调用方式,参数配置等方式来确定故障位置。硬件升级或应用环境能力改变,模块的升级不影响库函数的接口签名,使得模块易于升级。

4 性能测试

4.1模块功能测试

·测试硬件环境: VPX插箱,两块PowerPC板,1块交换板,CPU类型:8640D;

·8片CPU接收缓存区均设置为4 MB,单数据包大小设置为1200 B,发送速度20 MBps,设置配置文件(共56条配置信息),完成每片CPU分别与其他7 片CPU的通信,测试5 min;

·记录测试结果,发送接收数据一致;

·测试结果表明:参数配置程序完成了参数的可视化配置,同时模块实现了多个CPU之间的数据通信。

4.2通信速度测试

测试硬件环境: VPX插箱,两块PowerPC板,1块交换板,CPU类型:8640D。

4.2.1数据分类测试

接收缓存区大小为64 MB,单数据包大小分别为: 1200 B、65532 B、2 MB、8 MB、16 MB、32 MB时,设置配置文件,实现两PowerPC板上各一个CPU之间的通信,发送10 min,测试结果如表1所示。测试结果表明:该模块对各种类型报文的通信都具有良好的性能。

表1 数据分类测试结果

4.2.2通信能力测试

模块通信能力主要取决于DMA传输速度和内存拷贝速度,二者均受到硬件条件限制,下面分别进行测试。

改变单次发送数据包大小,分别设置为1 MB、2 MB、4 MB、8 MB、16 MB、32 MB,调用本模块发送函数循环发送,接收模块接收数据后循环拷贝至缓存,过程中分别计算DMA传输速度和内存拷贝速度。

计算方法: DMA传输速度记为(VDMA)MBps,发送次数(N)次,单次数据包大小(L)MB,传输时间(T)s,则: VDMA= N* L/T;计算20次结果取平均值。内存拷贝速度采用相同计算方法。测试结果如表2所示。

表2 模块能力测试结果

由表2得出以下结论:

(1)DMA传输速度>800 MBps,而内存拷贝速度峰值为110 MBps左右。该速度为通信过程中的峰值速度,大于该发送速度,接收端将不能及时读取数据至缓存;

(2)测试结果表明:模块通信速度受底层memcpy函数的限制,即硬件的处理能力,本模块具有良好的性能,满足通信需求。

4.3稳定性测试

上一节测试中,分别挑选3种情况进行长时间测试,结果如下:

(1)1200 B数据,0.2 ms/次发送速度,运行2 h,记录所有数据包的流水号,并分段将输入输出详细数据记文件,数据校验位正确,结果正确;

(2)65532 B数据,1 ms/次发送速度,运行2 h,记录所有数据包的流水号,并分段将输入输出详细数据记文件,数据校验位正确,结果正确;

(3)32 MB数据,500 ms/次发送速度,运行2 h,记录所有数据包的流水号,并分段将输入输出详细数据记文件,数据校验位正确,结果正确。

测试结果表明,该模块具有良好的稳定性。

4.4实用测试

该模块已应用于某项目中,VPX插箱中各CPU间SRIO通信均使用该模块,满足项目中所有通信需求。模块的易用性和可靠性节省了项目软件开发人员大量开发时间,并达到了所需的性能要求。

5 结束语

本文设计的SRIO通信模块具备良好的工程实用性,后期将会应用于更多的项目和产品中。其模块化的特点在项目和产品的软件开发中具有诸多优势,后续的应用反馈将使模块更加完善。本文的设计思想为工程应用中的软件模块化提供了参考。

参考文献:

[1]尹亚明,等.新型高性能RapidIO互连技术研究[J].计算机工程与科学,2004(12).

[2]Sam Fuller.RapidIO嵌入式系统互连[M].北京:电子工业出版社,2006.

[3]李春田.模块化研究[M].北京:中国标准出版社,2008.

[4]徐惠民.基于VxWorks的嵌入式系统及实验[M].北京:北京邮电大学出版社,2006.

Design of SRIO communication module based on VPX

GU Xiao-peng1,YANG Yu-liang2,ZHANG Ran2

(1.Naval Command Post,Beijing 100841; 2.No.724 Research Institute of CSIC,Nanjing 211153)

Abstract:According to the requirements of the SRIO communication for the VPX,a method of encapsulating the SRIO communication interface is proposed,and a SRIO communication module is designed and realized.The SRIO communication module adopts an idea of modularized software that the universal data communication mode between the CPUs of the PowerPC boards is designed based on the SRIO communication interface,which can realize the data communication between and inside the PowerPC boards.The binary system reusability for the module is realized in the form of library function.The module can be transplanted in any PowerPC programs,realizing the visualized configuration of the communication parameters and facilitating structural and modularized design of the software.The test results indicate that this module features good performance and binary system reusability.

Keywords:communication module; VPX; Serial RapidIO; modularized software

作者简介:谷晓鹏(1976-),男,工程师,硕士,研究方向:指挥自动化信息处理技术;杨玉亮(1987-),男,工程师,硕士,研究方向:雷达资源调度;张然(1989-),女,工程师,硕士,研究方向:雷达数据处理。

收稿日期:2015-03-03;修回日期:2015-03-18

文章编号:1009-0401(2015)02-0064-05

文献标志码:A

中图分类号:TN95