基于FPGA的高速固态存储器优化设计

杨玉华,刘兴俊,任俊杰

(1.中北大学 电子测试技术国家重点实验室,太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,太原 030051)

随着大容量固态储存器在航天航空系统、工业自动化、通信等行业的广泛应用和测量技术信息技术的快速发展,对大容量数据储存技术的要求也越来越高。现代雷达技术日益成熟,雷达信息的海量存储也成为了亟待解决的难题。雷达视频I、Q数据及图像遥测三路数据的采集带宽比较大、ADC采样速率比较高,实时产生大量的数据,如何将这些数据高速、实时地传输到存储设备成为了一个关键的问题。

1 高速固态存储器方案设计

高速固态存储器设计采用FPGA实现对LVDS高速接口以及数据的发送和接收的逻辑控制。FPGA强大的逻辑处理能力和丰富的片内资源成为了高速数据通信中最佳的逻辑控制处理器[1]。LVDS是一种效率极高的技术,能够提供高达3.125 Gb/s的数据率性能,其终结方法简单、功耗和噪声较低,使得LVDS成为数据率从数十Mb/s至3 Gb/s甚至更高的应用首选[2]。LVDS接口芯片组使用美国国家半导体的DS92LV1023和DS92LV1224,系统上电以后使能信号设置成有效状态,接收端和发送端必须同步之后才能进行高速数据传输。高速LVDS接口芯片数据传输速度可达660 Mb/s,功耗小于300 mW。

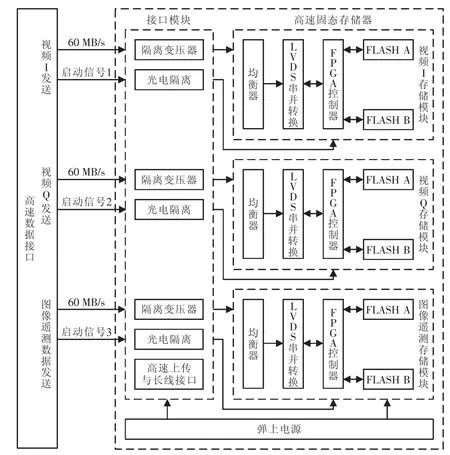

雷达视频I、Q数据及图像遥测3路数据须分别存储到对应的存储模块中。如图1所示为高速固态存储器优化后的原理框图,设计中采用了模块化设计,由1块接口板和3块高速数据存储板组成。各存储模块之间相互独立,电路组成结构相同,单个存储模块由LVDS接口控制模块和数据存储控制模块组成。接口板采取了隔离设计,弹上雷达系统输入信号隔离后的信号传给存储模块,存储模块控制信号采用光电耦合隔离,高速信号通过磁隔离变压器进行隔离。同时在接口板电路中设计了高速数据上传接口,将存储模块读取出的数据通过LVDS高速上传到地面测试台并通过USB接口将数据上传到计算机中实现数据分析与验证。

图1 高速固态存储器的优化原理Fig.1 Optimaization principle diagram of high-speed solid-state memory

2 高速固态存储器的优化设计

2.1 均衡加重技术

在高速数据的远距离传输中,传输电缆的信号衰减是产生存储数据误码的主要原因。因此为保证高速固态存储器接收数据的正确性和可靠性,在设计中采用针对特定数据速率和传输介质的信号调理技术,在模拟信号发送端采用了信号驱动器,在接收端使用信号均衡器。美国国家半导体公司的DS15BA101和DS15EA101电缆延展器芯片组采用了创新的设计,可以通过双绞线及同轴电缆驱动来自串行/解串器及FPGA芯片的串行数据流,能够优化在同轴、双绞线电缆中传输的均衡数据,速度高达 150 Mb/s~1.5 Gb/s[3-4]。 均衡器 DS15EA101 的自动均衡性能取决于发送器或电缆终端驱动器的发射幅值,对于100 Ω的差分电缆(双绞线电缆),最佳的发射幅值是±400 mV。均衡器DS15EA10的能量检测电路量化了输入的信号能量,将模拟信息反馈给自动均衡控制电路并把反馈信号与原始信号进行比较,基于比较的结果,控制均衡滤波器会将传输信号的高频分量提高一定量级的增益。

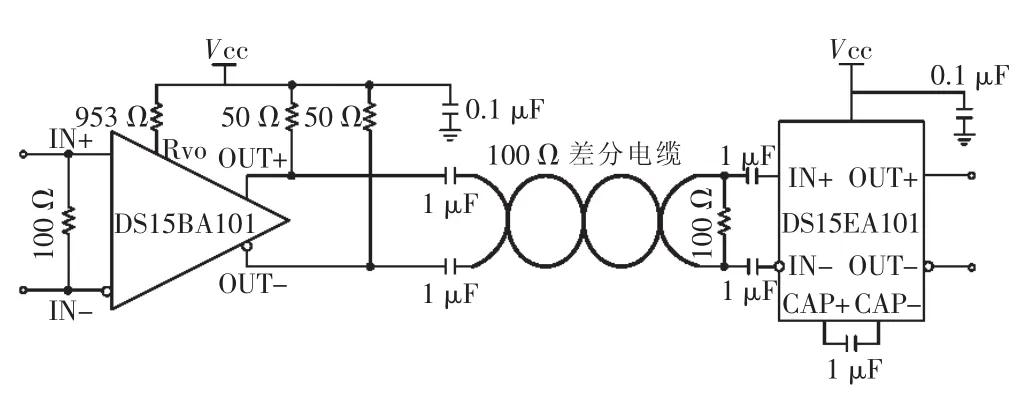

如图2所示为利用电缆延展芯片组和双绞线进行高速数据传输原理图。DS92LV1023输出通过1 μF电容交流耦合至驱动器DS15BA101中,在接收芯片前端接100 Ω负载,其在PCB布板时尽可能靠近DS15BA101输入端口。DS15BA101芯片输出端需要一个外置上拉电阻设定最佳发射幅值,需要2个50 Ω/1%精度的电阻上拉至VCC。同时,对于双绞线传输介质,其特性阻抗为100 Ω,交流耦合方式的输出增益调制上拉电阻值为953 Ω。同样,在传输电缆数据接收端也是交流耦合,芯片输入端需要一个外部交流耦合滤波电容,输入端口需要端接100 Ω阻抗匹配电阻。

2.2 分时加载操作的优化

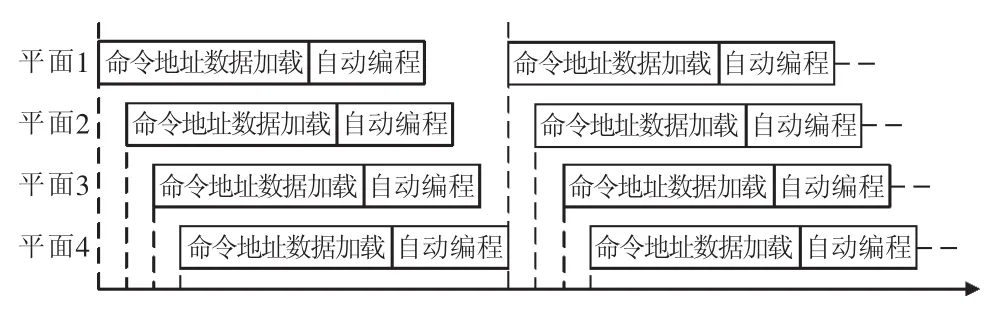

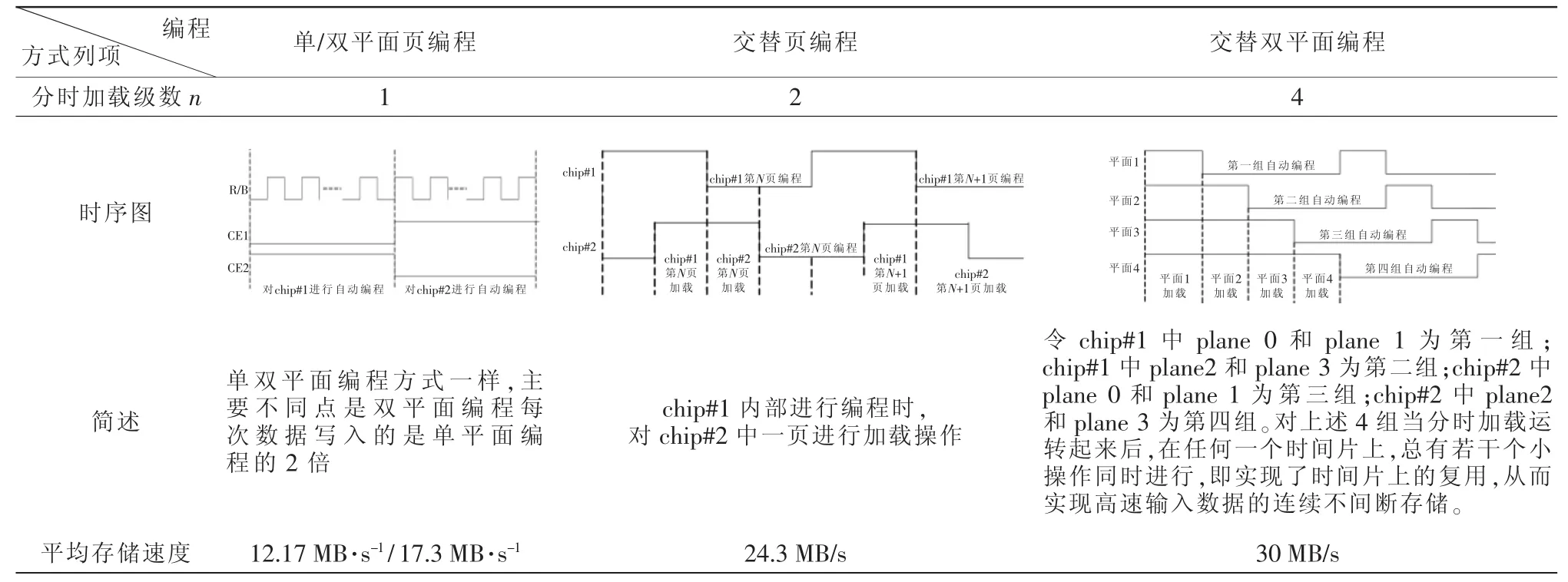

NANDFLASH是基于页编程、块擦除操作的,在此期间内不响应其他相关操作,因此必然会降低数据存储速度。FLASH页编程操作可以分为加载过程和自动编程过程。加载过程主要完成编程命令、地址下发以及将数据写入页寄存器的过程。在完成对FLASH的第一平面加载后,第一平面的指定页面进入自动编程时间,立即对第二平面进行加载,以此类推。当多个平面完成加载后,第一平面已经完成了自动编程操作,再次对第一平面进行加载操作,如此循环。采用分时加载操作可以保证输入数据被源源不断地写入芯片中,最大限度地提高了数据的平均写入速度。如图3所示为分时加载操作示意图。

图2 双绞线延长传输原理Fig.2 Extended twisted-pair transmission principle diagram

图3 分时加载原理Fig.3 Principle diagram of the time-sharing loading

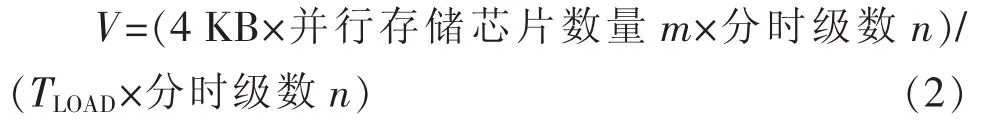

假设NANDFLASH的分时加载级数是n级,分时加载总时间要大于或等于最大编程时间,即:

式中:TLOAD为命令地址数据加载时间;TPROG为页自动编程时间。

分时加载操作模式下的存储器平均存储速度为

由表1中4种NANDFLASH的分时加载操作比较可知,交替双平面编程方式采用了4级分时加载级数,根据式(1)、式(2)得出平均写入速度最快达到30 MB/s,使用2片NANDFLASH进行存储器带宽扩展,平均存储速度可达到59 MB/s,即可满足高速固态存储器设计的要求。

表1 针对NANDFLASH优化后的分时加载操作比较Tab.1 In view of the NANDFLASH load operation is optimized

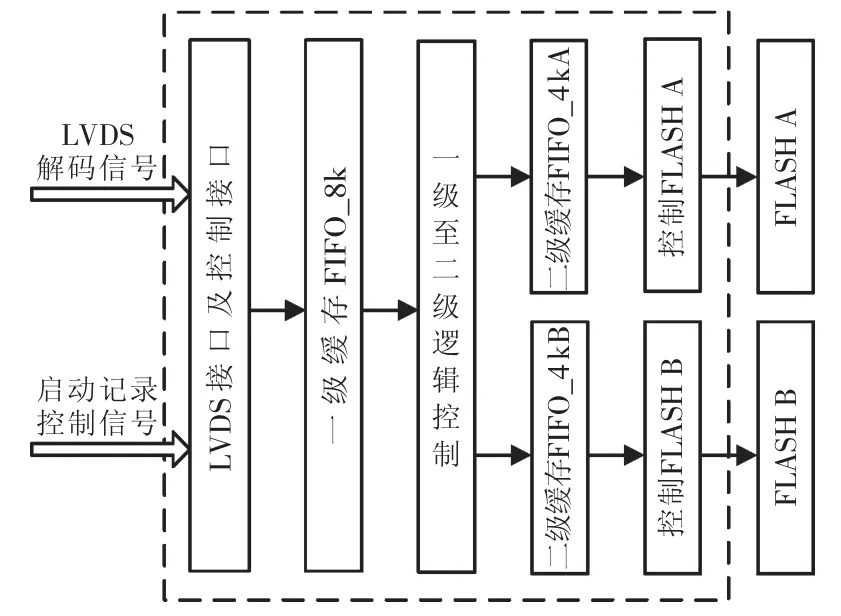

2.3 基于FPGA的二级缓存

本文使用的NANDFLASH单页容量为4 KB,根据自动编程的方式特点将二级缓存FIFO容量设置为FLASH一页的大小,2个二级缓存FIFO交替动作分别写入2片FLASH中。一级缓存FIFO设置为二级缓存容量的2倍。图4所示为基于FPGA的二级缓存逻辑示意图。

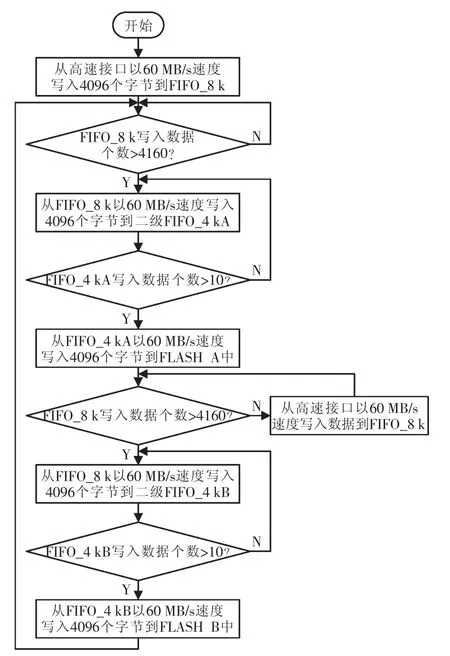

图5所示为基于FPGA的二级缓存的流程图,利用FPGA内部的双口FIFO资源[5-6],当接口模块接收到来自弹上的启动记录信号,雷达视频I、Q数据及图像遥测三路数据的LVDS解码信号以60 MB/s通过高速接口送入一级FIFO_8k,当写入数据大于4160字节后,将一级缓存的数据以60 MB/s的速度读出4096字节并写入二级缓存FIFO_4kA中,而FPGA内部控制FLASH的模块判断到二级缓存的数据量大于10字节后,则以30 MB/s的速度连续读取4096个数据写入FLASH A中;再次判断一级缓存的数据是否大于4160字节,若大于则将一级缓存的数据以60 MB/s的速度读出4096字节并写入二级缓存FIFO_4 kB中,以同样的方式将数据从二级缓存中读出并写入FLASH B中,如此交替,直至数据记录完成。

图4 基于FPGA的二级缓存逻辑示意Fig.4 Second level cache based on FPGA logic diagram

图5 基于FPGA的二级缓存流程Fig.5 Second level cache flow chart based on FPGA

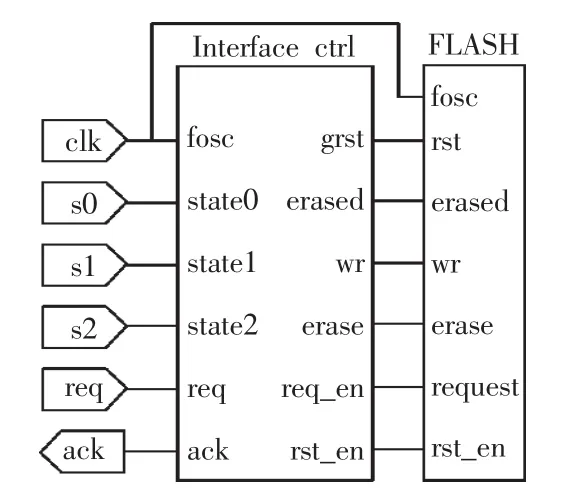

2.4 多线组合指令

采用多线组合逻辑指令控制能有效减少控制线的数量,简化硬件电路结构,同时能快速实现指令的扩充,方便设计人员设计和调试。

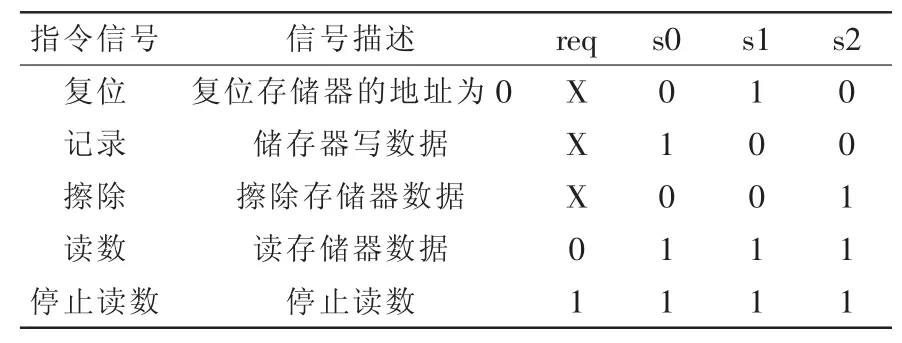

在高速固态存储器中,根据上位机发出的控制指令,使存储器实现相应的读、写、擦除、复位、停止读数等操作,控制指令的可靠性是实现存储器工作状态有效控制的首要问题。为保证指令发送的可靠性,上位机到存储器的指令采用并行发送的方式。指令个数N与状态控制线m需满足2m>N,高速固态存储器共使用6个指令,故使用3条状态线(s0,s1,s2)进行组合发送,在FPGA逻辑控制中使用三线制指令控制器,如图6所示。具体接口指令定义如表2所示。在对FLASH进行控制时,主要指令包括复位、读写、擦除及停止读数等控制指令,三线组合能组合不同指令,在不影响存储系统性能的情况下实现FLASH的可靠控制。

图6 三线控制器接口封装图Fig.6 Three wire controller interface encapsulation

表2 状态线组合指令定义Tab.2 Directive defines state line combination

3 试验结果

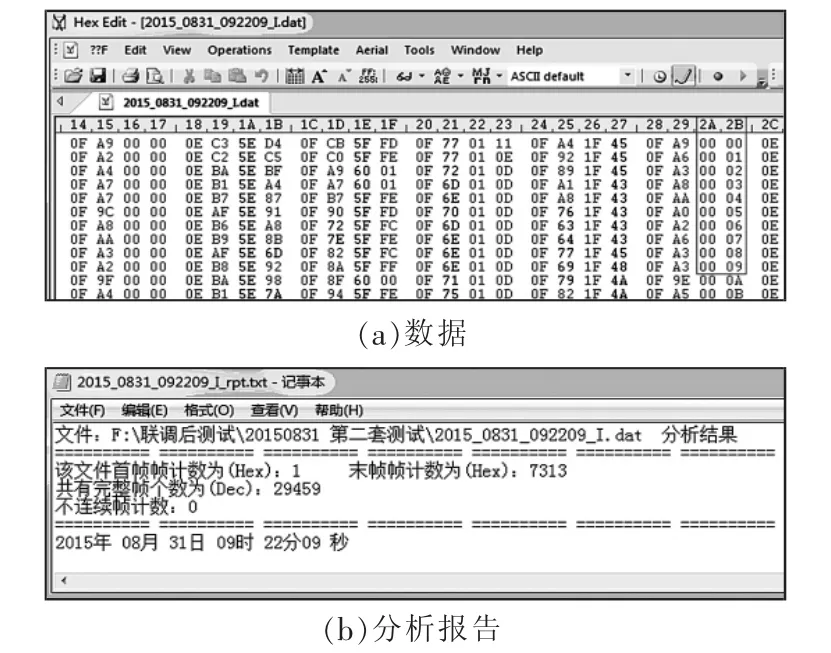

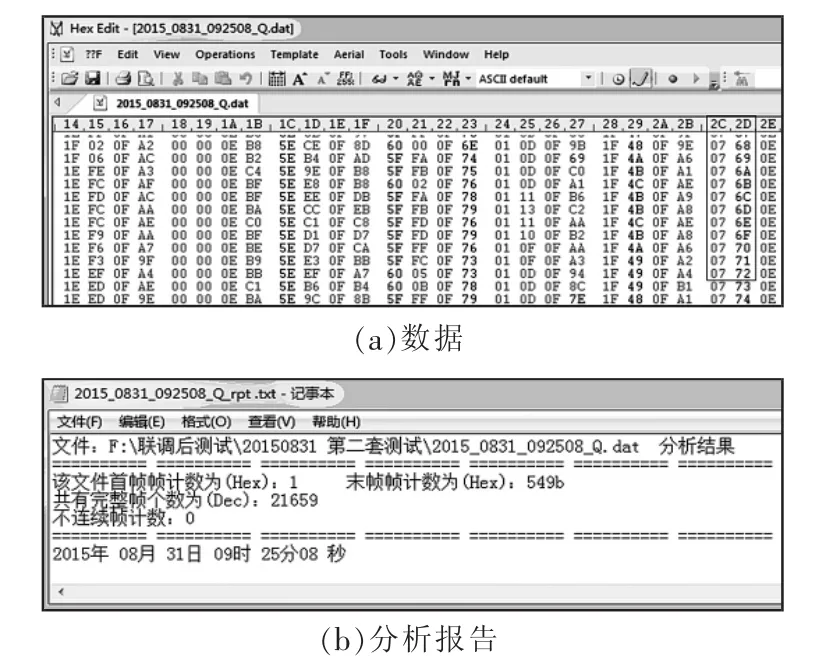

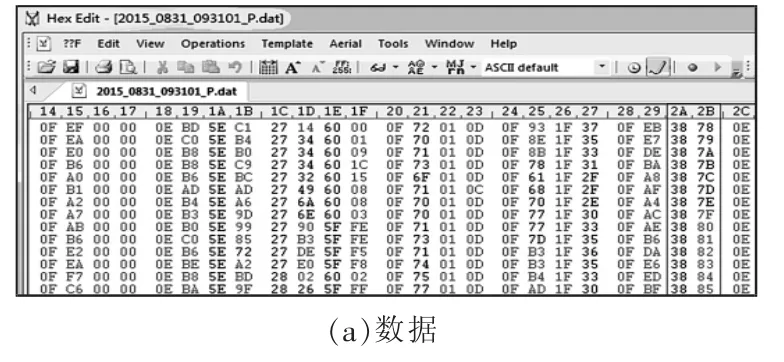

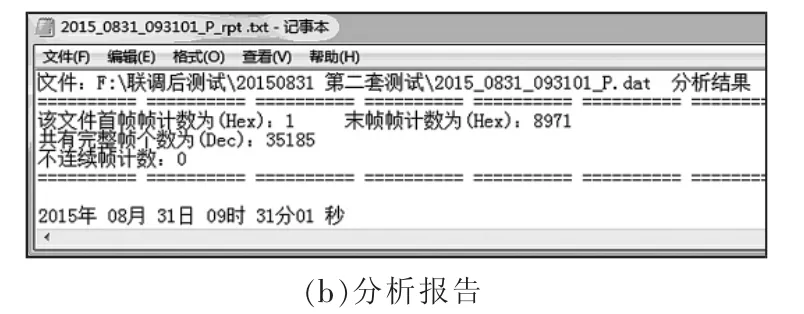

测试台信号源发送自加数送往采编器采编后存入高速固态存储器中,图7、8、9分别为回读到计算机中的雷达视频回波I路数据、回波Q路数据和图像遥测数据及分析报告。存储单元回读数据符合设计,数据传输和存储过程中帧计数连续、未出现丢数、误码等现象。

图7 雷达视频回波I路数据及分析报告Fig.7 Radar video echo I road data and analysis report

图8 雷达视频回波Q路数据及分析报告Fig.8 Radar video echo Q road data and analysis report

图9 雷达图像遥测数据及分析报告Fig.9 Radar image remote sensing data and analysis report

4 结语

对于高速LVDS传输电缆使用了均衡加重措施,提高了传输信号的质量,减小了信号存储数据的误码率;分时加载操作结合NANDFLASH的结构特点设计了双平面交替编程方式,最大程度地提高了平均存储速度;基于FPGA的二级缓存提高了数据的准确性;多线组合指令控制有效减少控制线的数量,硬件电路结构得到了简化。通过多种措施的优化提高了高速固态存储器的平均存储速度、可靠性和稳定性,对于高速存储记录器的设计具有的借鉴作用。

[1]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[2]美国国家半导体LVDS用户手册[Z],2008.

[3]The Datasheet of DS15BA101[Z],2007.

[4]王胜,王新宇.LVDS技术及其在高速系统中的应用[J].遥测遥控,2007,26(4):41-45.

[5]马游春,张涛,李锦明.FPGA集成FIFO在高过载存储测试系统中的应用[J].仪器仪表学报,2006,27(6):586-587.

[6]王可恕.模拟集成电路原理与应用[M].北京:电子工业出版社,2009.