基于FPGA的电能质量远程监测系统

(哈尔滨理工大学 自动化学院,哈尔滨 150080)

在供配电网络中,存在着含有大量的非线性、冲击性负荷的电力电子设备,在实现功率控制和处理的同时,都不可避免地产生谐波电流,引起电压波形畸变,因此需要对电能质量实时地检测分析[1]。目前我国研制的大多数电能质量监测装置都是以DSP为处理运算核心,但是DSP是串行的,在进行大点数FFT运算时,实时性不高。随着FPGA技术的发展,其强大的并行处理能力逐渐凸显出来,运用SOPC技术将Nios II处理器与用户自定义逻辑结合构成一个基于FPGA的片上系统,大大减少了设计成本与时间[2]。

本系统基于Altera公司的FPGA进行设计,由16位的多通道数模转换器实现6路信号的同步采样,数据采集与存储、FFT谐波运算、有效值运算、频率检测统一由有限状态机来进行时序控制,实现了对电网电能的频率、电压电流有效值、功率和各次谐波等电能参数的实时远程监测。

1 系统总体设计

该监测系统主要由信号调理模块、AD转换模块、过零检测模块、有限状态机模块、频率检测模块、Nios II模块、FFT模块、有效值模块、MAC模块、以太网模块和上位机等模块组成。三相电压电流信号经过互感器电路将大电压、大电流转换成弱电信号,然后通过抗混叠滤波电路处理,滤除检测范围以外的高频谐波,防止谐波分析时出现混叠现象,最后通过电平提升电路将信号电平提升到0~5 V,提供给数模转换模块进行转换和处理。同时经滤波后的信号一路输出给过零检测电路,输出与输入信号相同频率的方波信号,经过硬件锁相倍频模块处理,实现数据的同步采样。频率检测模块对过零检测模块输出的方波信号进行检测,采用频率周期测量法,对电网频率进行测量。模数转换结果缓存在输入双口RAM中,并行6通道FFT IP核模块和有效值模块读取缓存数据并分别进行每路256点的快速傅里叶变换和有效值运算,并将处理数据缓存在输出双口RAM中。当输入和输出双口RAM中数据准备完成后,以中断的方式通知Nios II处理器读取数据,并通过以太网的方式传输到上位机对数据进一步处理。系统总体设计如图1所示。

图1 系统总体设计Fig.1 Diagram of system overall design

2 主要功能模块设计

2.1 频率检测模块

频率测量的方法一般有周期测量法、频率测量法、正交去调制法等[3-4],其中周期测量法以高频的基准频率源fx作为基准,用基准频率源对Nw个周波长度的待测信号计数,则根据计数值Nx,可得被测信号源频率为fw=(fxNw)/Nx。由于电网频率在50 Hz左右,频率较低,并且本FPGA系统的工作时钟为100 MHz,所以采用周期测量法可实现较高的测量精度。

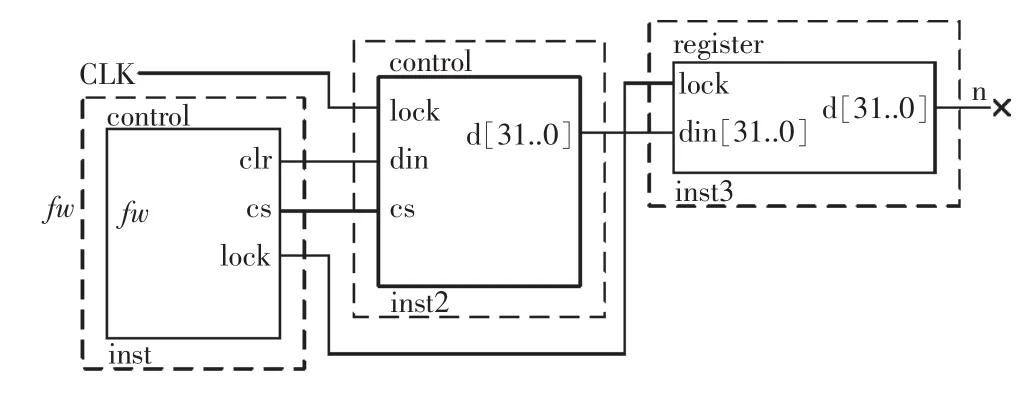

本频率检测模块包括3部分:测频控制器、计数器和锁存器。实现方式如图2所示。图中CLK为系统时钟100 MHz作为基准频率源,fw为被测信号源频率。输出结果n送给Nios II做进一步处理。对于测频控制器,被测信号二分频后产生控制信号cs和clr分别用于选通、停止并清零计数器,以及lock用于控制锁存器。计数模块,当cs高电平时,counter开始对标准时钟计数,在clr高电平时停止并清零结果。锁存器的目的是方便读取计数器的结果,cs由高变低时,lock置1,锁存计数器的结果。因此完成测频过程需要被测信号的2个周期,第1个周期计数标准时钟,第2个周期锁存结果然后清零计数器,得到测频结果。

图2 测频电路Fig.2 Schematic of frequency measurement

2.2 AD转换模块

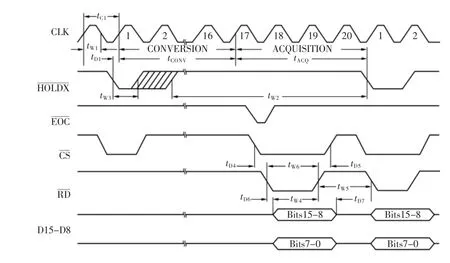

将三相电压、电流一共6路模拟信号转换为数字信号,选择的是TI公司的ADS8364转换芯片,每路转换精度为16位,转换速率为250 KSPS,具有一个高速并行输出接口,可实现6通道的同步采样[5]。6个通道被分成3个通道对A、B、C,每个通道对的采样控制信号分别为HOLDA,HOLDB,HOLDC,由于要进行6通道并行同步采样,所以将3个控制信号连接在一起组成HOLDX,统一进行采样控制。通过FPGA片内时钟分频,提供给ADS8364芯片5MHz的采样时钟,完成一次采样转换最多需要20个时钟周期,约为4 μs,系统的采样频率为12.8 kHz,约为78.1 μs,完全满足采样要求。采样过程为,当采样触发信号上升沿到来时,拉低HOLDX至少20 ns,启动采样(6个通道同时进行采样),当转换完成后,转换数据保存在6个寄存器中,读取信号RD至少要拉低50 ns,完成一次读取操作,并且在下一次读取操作前要至少保持30 ns的高电平,读取模式设置为循环周期读取模式,所以通过6次拉低拉高RD信号来实现对6路转换的读取[6]。ADS8364的控制时序如图3所示。

图3 ADS8364的控制时序转换图Fig.3 Diagram of ADS8364 control timing

2.3 有限状态机、FFT和有效值模块

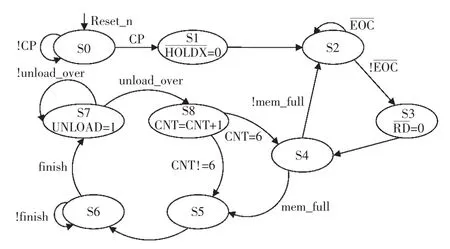

有限状态机控制模块实现对AD数据采集与转换、数据缓存、FFT与有效值处理模块的控制。有限状态机的状态转移图如图4所示。触发脉冲到来之前一直处于等待状态S0,当锁相倍频触发信号到来时进入S1状态,拉低HOLDX,启动AD转换,然后进入S2状态,在S2状态等待EOC,当EOC变为低电平时,表示转换结束,无条件转入S3状态,否则在S2状态持续等待[7]。在S3状态读取AD转换结果,并存入输入双口RAM中。S3在下一个时钟到来时进入S4状态,在S4状态判断输入双口RAM是否存满,若存满,则发出存满指示信号,进入S5状态,否则持续S2、S3、S4状态直至存满RAM。S5状态输出启动信号,用来启动FFT模块和有效值处理模块,然后进入S6状态,在S6状态等待FFT模块和有效值处理模块完成信号finish的到来,随后进入S7状态,输出高电平给UNLOAD信号,卸载FFT模块变换得到的数据,当unload_over信号为高电平说明卸载完成进入S8状态,准备下一轮转换,否则在S7状态持续等待。在S8状态对CNT开始计数,若CNT等于6,对其清零并跳进S4状态,若小于6则跳进S5状态。

图4 有限状态机的控制状态转移图Fig.4 FSM control state transfer diagram

FFT模块使用的是Altera公司的FFT IP核,目标器件选择Cylone IV系列[8],变换长度选择256点,输入、输出位宽精度和旋转因子的位宽精度都选择16位。选用此FFT IP模块能够缩短FPGA的设计周期和成本,提高系统的性能和可靠性。

被测三相电压电流信号的有效值也是电能质量的重要参数,以电压有效值的计算为例,离散化连续采样信号u(t),在一个周期T内,采样N点数据则电压有效值计算公式为[9]

式中包括平方、求和累加、开方和除法运算,在FPGA中除法是通过移位来实现的,导致处理结果误差较大,精度不高,所以上式中的除法运算在Nios II处理器中实现。当输入双口RAM中数据存储完毕后,256点数据同时送入FFT模块和有效值模块,在有限状态机的控制下,依次将6路数据进行处理。有效值模块的结构图如图5所示。

2.4 以太网传输模块

以太网模块由数据链路层(MAC)和物理层(PHY)组成,其中MAC使用的是FPGA提供的三速以太网MAC IP核控制器,PHY物理层选择的是Marvell 88E1111千兆以太网网络芯片[10]。MAC IP核通过Avalon总线与 Nios II处理器相连接,当Nios II处理器对采集的数据进行预处理后,通过MAC层根据TCP/IP协议栈对数据进行打包、组帧、校验等处理后,通过GMII接口传输给物理层PHY[11-13],将数据发送到上位机进行处理,实现对电能参数的远程监控。其中Nios II处理器在网络传输中主要分为3个部分:应用程序、TCP/IP协议和驱动程序。应用程序由用户调用协议栈接口程序来实现以太网数据传输,而以太网驱动程序为上层协议与三速以太网IP核架起了桥梁。千兆以太网设计框图如图6所示。

图6 千兆以太网设计框图Fig.6 Diagram of gigabit-ethernet degign

3 系统软件设计

软件部分包括有限状态机控制模块程序、Nios II处理器运行程序和上位机模块3个部分。有限状态机控制模块使用Verilog HDL语言进行编写,主要包括AD采样转换控制模块、输入输出RAM控制模块、FFT控制模块、有效值控制模块等控制逻辑。数据采集与存储、FFT与有效值运算都在有限状态机的控制下有序进行。Nios II处理器运行程序由C/C++语言编程实现,主要包括初始化模块、对中断的响应和对数据的以太网传输。当频率检测模块完成频率检测或是输出缓存存满时,以中断的方式通知Nios II处理器对数据进行读取,同时在Nios II处理器上嵌入应用程序、TCP/IP协议和PHY芯片的驱动程序,来实现数据与上位机的传输。本系统的上位机采用的是美国NI公司开发的面向计算机测控领域的虚拟仪器软件开发平台LabVIEW[14],利用丰富的版面功能和库函数来实现电能质量参数的计算与直观显示。

4 结语

本文提出了一种基于FPGA的电能质量远程监测系统,充分利用了FPGA强大的并行处理能力和高度集成的特点。运用硬件锁相环技术实现了对三相电压电流的同步采样,在有限状态机的整体控制下对数据进行谐波和有效值运算,并利用千兆以太网芯片将数据传输到上位机进行处理与显示。实现了对电网电能的频率、电压电流有效值、功率和各次谐波等电能参数的实时远程监测。

[1]陈宏.基于FPGA的电能质量监测装置的研究[D].哈尔滨:东北农业大学,2010.

[2]梁海霞.基于FPGA的电力系统谐波检测装置的研制[D].济南:山东大学,2008.

[3]刘明.电能质量检测算法研究与监测装置实现[D].秦皇岛:燕山大学,2014:8-11.

[4]杨秀增.基于Nios II的自适应高精度频率计设计[J].自动化与仪表,2009,24(7):13-16.

[5]TI.ADS8364数据手册.[EB/OL].[2013].http://www.ti.com.cn/product/cn/ads8364.

[6]马建荣.船舶电网电能质量监测系统研究[D].镇江:江苏科技大学,2013.

[7]郑争兵.基于FPGA的高速采样缓存系统的设计与实现[J].计算机应用,2012,32(11):3259-3261.

[8]钱文明,刘新宁,张艳丽.基于Cyclone系列FPGA的1024点FFT算法的实现[J].电子工程师,2007,33(2):12-14.

[9]韦宏,付友涛,孔凡鹏.基于FPGA的千兆以太网设计[J].现代电子技术,2012,35(18):56-59.

[10]于庆广,付之宝.电能质量指标及其算法的研究[J].电力电子技术,2007,41(1):10-12.

[11]李航.基于FPGA和千兆以太网(GigE)的图像处理系统设计[D].南京:南京理工大学,2014.

[12]Mahmoodi M R,Sayedi S M,Mahmoodi B.Re-configurable hardware implementation of gigabit UDP/IP stack based onspartan-6 FPGA[C]//Yogyakarta:InternationalConferenceon Information Technology and Electrical Engineering,IEEE,2014.

[13]FCOSTA,S CHAPELAND.The new frontier of the DATA acquisition using 1 and 10 Gbit/s Ethernet Link[J].Physics Procedia,2012(31):1956-1964.

[14]杨乐平,李海涛,杨磊.LabVIEW程序设计与应用[M].2版.北京:电子工业出版社,2005.