机载数据记录仪的1553B总线接口设计

靳 鸿 ,张志伟 ,崔建峰 ,王 建

(1.中北大学 电子测试技术国家重点实验室,太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,太原 030051;3.北方自动化控制技术研究所,太原 030006)

随着航空电子技术的飞速发展,对机载记录仪的要求日益提高,测试信号之间复杂度的不同,要求机载数据记录仪不仅要适应高压、高冲击的飞机环境、还要具备数据复杂度高、完整度高和系统可靠性高等特点。传统的数据记录仪大多采用RS232或USB2.0总线接口进行通信,实现测试数据的实时记录[1],这种方法具有操作方便、易于实现、成本低等优点,但当机载数据记录仪工作于飞行状态时,RS232或USB2.0总线通讯存在数据传输不稳定、数据失真等问题。在当今工业控制领域,现场总线的需求日渐突出,航空总线作为飞机的神经网络,在航空领域中发挥着重要的作用[2-3]。1553B总线标准被指定作为飞机内部的数据总线标准,具有抗干扰能力强、通信灵活、冗余容错能力强、可靠性高、传输效率高等优点[4]。本文提出一种机载数据记录仪的1553B总线接口设计与实现方法,当记录仪处于飞行状态时,机载计算机通过1553B总线控制记录仪的工作;当记录仪处于地面状态时,地面站通过地面计算机控制记录仪的工作,并实现记录仪的数据上传,以备事后分析。

1 系统构成及概述

记录仪采用了模块化思想[5],将1553B接口模块设计为功能独立的模块,接口模块与基板的连接采用自定义总线接口,接插件采用型号为HJ30J-18TJWP58的航空接插件。系统的工作过程为记录仪通过1553B接口模块接收到机载计算机(BC)的消息数据后,将消息数据解析出来的16位数据字发送给基板,基板接收到数据字后,统一管理其他记录模块的工作。系统结构如图1所示。

图1 系统结构Fig.1 Structure diagram of the system

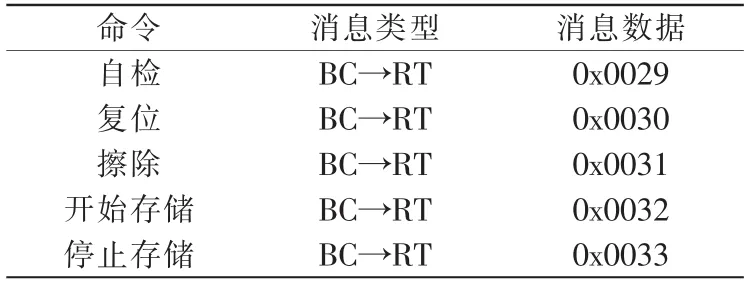

本系统中机载计算机作为总线控制端(BC),1553B总线接口模块作为远程终端(RT),RT地址设为1,子地址设为1,1553B总线报文传输采用BC→RT格式,记录仪自定义RT控制指令如表1所示。

表1 RT控制指令定义Tab.1 RT control instruction definition

2 1553B总线接口模块设计

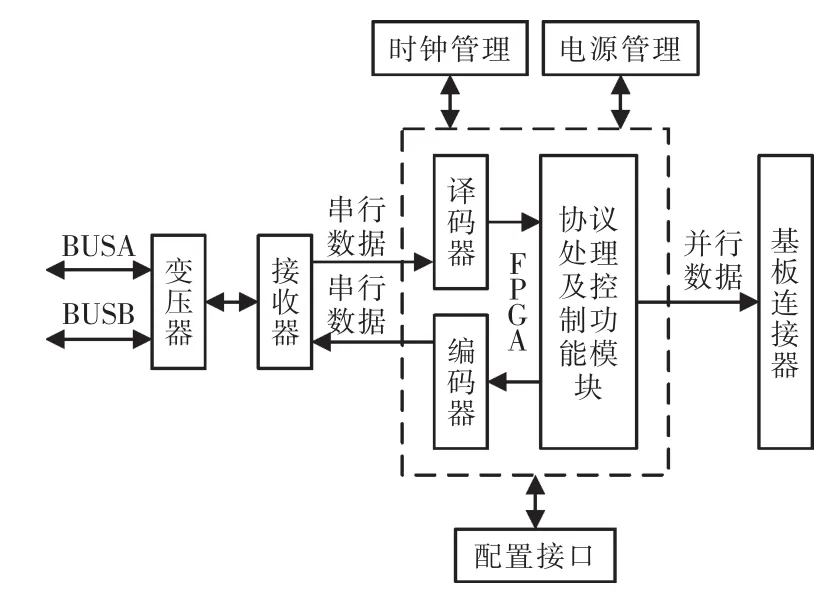

1553B总线接口模块主要完成记录仪与机载计算机的通讯连接,实现1553B总线协议处理功能,并将解析得出的数据字发送给基板。1553B总线接口模块结构如图2所示,其硬件电路主要由1553B总线接口模块、FPGA控制模块、电源管理模块、时钟管理模块、FPGA配置接口模块等组成。

图2 1553B总线接口模块结构Fig.2 Structure diagram of 1553B bus interface card

2.1 接口模块硬件设计

1553B总线接口电路原理如图3所示,接口模块采用“电气接口+1553B耦合变压器+1553B总线收发器”的结构,其功能为1553B总线上的数据通过总线变压器及码型转换后进入FPGA功能模块。1553B总线电气接口BUSA/BUSB采用单通道双冗余模式,该模式具有通信效率高,容错能力强的优点,接插件采用1553B总线专用连接器CJ450;BUSA/BUSB通道以变压器耦合的方式连接到总线控制器[6],这种方式比直接耦合方式更具有实际价值,耦合变压器采用PM-DB2725EX芯片;收发器用来收发双冗余通道的1553B消息数据,将数据总线上传至终端的双电平曼彻斯特码转换为单电平曼彻斯特码,或者将准备发送至总线的单电平曼彻斯特码转换为双电平曼彻斯特码,设计采用HI-1573收发芯片,该收发器拥有2个独立的收发模块,操作温度范围为-65℃~150℃,完全满足航天操作要求。

2.2 FPGA控制模块设计

1553B总线接口模块控制器采用Altera的FPGA芯片Cyclone EP1C12Q240作为核心控制器。本设计根据记录仪的功能需求,采用FPGA选择性地完成总线协议处理功能,即1553B接口模块只接收“BC-RT”类型的命令,系统响应后返回BC端状态字和数据字。此方法代替了传统价格昂贵的1553B协议芯片BU-61580[7],不仅简化了外围电路,提高了电路的稳定性,而且增加了设计的灵活性,同时降低了开发成本。

FPGA控制模块内部设计包括译码器模块、协议处理及控制功能模块、编码器模块。其工作流程为总线上传输的串行数据进入译码器后,经译码器解码后提供一系列有关当前被译码的字的信息,这些信息随后进入协议处理及控制功能模块,该模块进行进一步的辨别及处理,按不同情况做出回应,并将产生的状态字和数据字以及字格式信号发送至编码器,最终以符合1553B总线数据格式的方式传输至总线控制器BC。

2.2.1 译码器设计

译码器主要实现的主要功能是将1553B总线收发器上得到的串行数据经过同步头检测、曼彻斯特II型码转换、串并转换及奇偶校验后,提取出指令字格式、同步头检测错误信息、16位并行数据、奇偶校验错误信息等以供之后的模块使用。整个译码器如图4所示,包括同步头检测模块、码型转换模块、串并转换及奇偶校验模块。译码器模块设计首先考虑的是如何对1553B数据进行采样,由1553B总线协议标准可知,1553B数据总线的传输速率是1 Mb/s,而曼彻斯特II型码的每位数据编码都占2位,且同步头是在1.5位时有跳变,故需要1 MHz、2 MHz的时钟作为译码时钟,本设计中系统输入时钟选择50 MHz,采用25分频和50分频产生2 MHz和1 MHz的时钟。

图4 译码器结构框Fig.4 Structure diagram of the decoder

当同步头检测模块的使能信号en有效,清零信号clr无效时,同步头检测模块采用clk2信号(2 MHz)时钟对1553B总线串行数据信号rx、nrx(nrx为rx的反相数据)进行采样记录,若采样值为111000,表示消息数据为命令字/状态字,则输出字格式信号syn_type为1,且输出给码型转换模块的使能信号en1有效;若采样值为000111,则表示消息数据为数据字,输出字格式信号syn_type为0,并输出给码型转换模块的使能信号en1;若采样得到其他值,则输出的同步头检测错误信号syn_err有效,且使能信号en1无效。

码型转换模块收到使能信号en1后,采用clk1信号(1 MHz)时钟对输入信号rx进行异或非运算得到译码信号data,实现对曼彻斯特II型码的码型转换,以及下一模块的使能信号en2。

串并转换及奇偶校验模块得到使能信号en2后,采用clk1信号(1 MHz)时钟对译码信号data进行串并转换后,输出16位并行数据Dataout[15..0]和下一模块的数据使能信号Data_en,同时验证16位数据的奇校验位,输出奇校验错误信号odd_err,最终完成译码过程。

2.2.2 协议处理及控制功能模块设计

协议处理及控制功能模块实现的主要功能是对译码器发送的信息进行辨认及处理后,按不同情况作出回应,最后将生成的状态字和数据字发送给编码器,并将16位数据字发送给基板接口。协议处理及控制功能模块组成如图5所示,主要包括协议处理模块、状态字寄存器模块和数据整合模块。

图5 协议处理功能及控制模块组成Fig.5 Composition diagram of the agreement processing and functional control module

协议处理模块的输入信号分别有时钟信号clk、系统清零信号clr、同步头类型信号syn_type、同步头错误信号syn_err、奇校验错误信号odd_err、译码完毕数据使能信号data_en、16位并行数据信号datain[15..0]、终端地址信号 RT_addr[4..0]以及终端子地址信号RT_zaddr[4..0]。输出信号分别有状态字寄存器模块使能信号en1、状态字消息错误标志信号z_err、数据字输出信号q_[15..0]、清零信号z_clr。

协议处理模块根据译码完毕后的数据使能信号Data_en和同步头类型信号syn_type确定输入的数据datain[15..0]是否为命令字,如果syn_type为1(表示命令字),则将 datain[15..0]的 16位有效数据按命令字标准格式进行分析,将datain[15..11]与系统输入的终端地址信号RT_addr[4..0]做比较,同时将datain[9..5]与系统输入的终端子地址信号RT_zaddr[4..0]做比较,若都相同,则说明该命令是总线控制器发给本系统的命令,准备下一阶段工作;若不同,则说明命令不是发给本系统的,系统不对其进行响应。终端地址信号可由FPGA内部设定也可由外输入设定。datain[10]是T/R位,为发送/接收位,接收时为逻辑0,发送时为逻辑1,本系统只具有远程终端功能,故该位保持1,即收到datain[10]为 1 的命令时系统给予响应;datain[4..0]为数据字计数,表示本系统应接收的数据字个数,系统应准备接收数据字。在命令字分析过程中,若出现同步头检测错误、奇校验错误以及协议处理模块在处理命令字的过程中产生的错误,则状态字消息错误标志信号z_err有效。如果syn_type为0(表示数据字),且无同步头检测错误和奇校验错误,则根据命令字中解析出的数据字计数,依次将datain[15..0]写入协议处理模块内部容量为32×16的fifo缓存器,以备数据整合模块读取数据字;若出现同步头检测错误或奇校验错误,表明数据字无效,fifo为空。

状态字寄存器模块的主要功能是生成有效的16 位状态字 z_data[15:0],其中 z_data[15:11]是远程终端地址,该位由系统终端地址信号RT_addr[4..0]决定;z_data[10]是消息差错位,该位由消息错误信号z_err来决定,若错误时该位置1,反之为0;其余各标志位根据使用状况分别置位。

数据整合模块首先通过输出fifo读使能信号rdreq和fifo读时钟信号rdclk读取协议处理模块中的数据字缓存器fifo;数据整合部分将读取的数据字 q[15..0]、状态字输入 z_data[15..0]进行整合处理,最后输出本系统响应的数据dout[15..0]、同步头类型信号encode_sys_type、使能信号encode_en给编码器,同时输出数据字s_data[15..0]给基板。

2.2.3 编码器设计

编码器设计实际上是译码器设计的逆过程,其主要功能是将协议处理及控制功能模块得到的16位状态字和数据字通过并串转换和码型转换得到曼彻斯特II型码,并添加相应同步头以及奇校验位,最终以串行方式和1 Mb/s的传输速度发送至1553B总线上,具体设计过程与译码器设计相似。

2.3 其他硬件模块设计

其他硬件模块主要包括电源管理模块、时钟管理模块、FPGA配置接口模块等。电源管理模块根据各元器件的供电要求,将5 V的输入电压经电源转换芯片29302T6产生所需的电压值3.3 V和1.5 V;时钟管理模块主要为FPGA提供20 MHz的时钟;FPGA配置接口模块采用JTAG配置方式,配置芯片选择EPCS4N。

3 系统测试结果

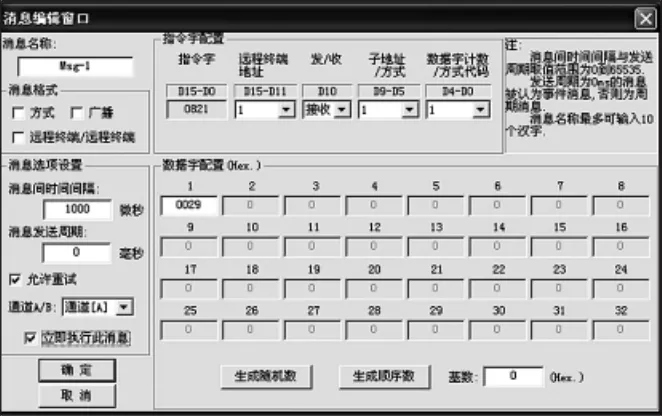

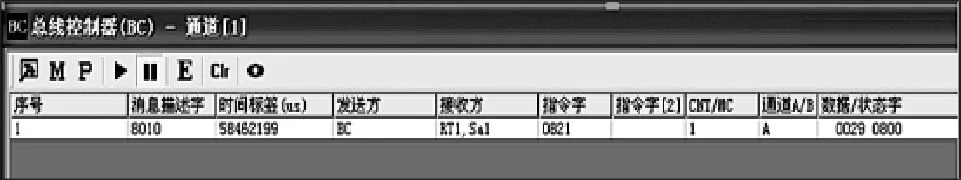

采用地面站对记录仪进行了测试。将装有1553B通讯板卡的计算机设置为BC端,向RT地址为0001h、子地址为0001h的记录仪发送自检命令0029h,消息配置如图6所示,生成的命令字为0821h。消息命令发送后,BC端收到记录仪回复的状态字和数据字,如图7所示,图中显示状态字为0800h、数据字为0029h。经计算可知记录仪返回正确的状态字,由此表明记录仪与BC端通讯成功。

图6 BC端的消息配置Fig.6 BC port of the message configure

图7 BC端的消息记录Fig.7 BC port of the message record

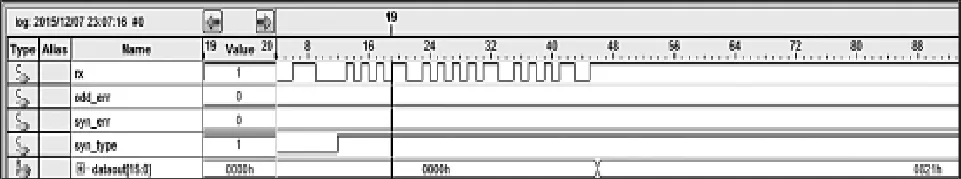

为验证FPGA内部1553B协议处理的正确性,同时使用QuartusⅡ内部集成的SignalTapⅡ Logic Analyzer软件,观测FPGA内部译码器和协议处理及控制功能模块的工作状态。BC端发送命令字0821h后,SignalTapⅡ观测译码器的主要信号如图8所示,从图中可知译码器译出的数据为0821h且同步头类型信号sys_type为1,表示0821h为命令字,故译码过程正确。

图8 SignalTapⅡ Logic Analyzer观测编译器主要信号Fig.8 SignalTapⅡLogic Analyzer observer compiler main signal

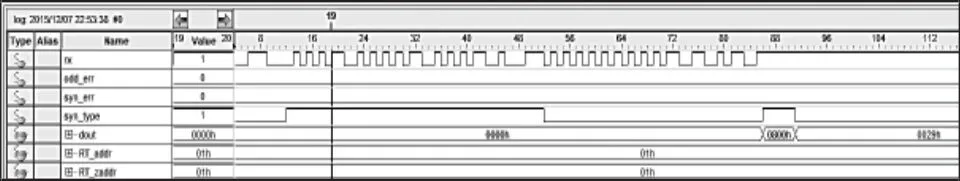

图9所示为SignalTapⅡ观测协议处理及控制功能模块的主要信号,从图中可知命令字0821h以及数据字0029发送后,协议处理及控制功能模块首先回复状态字0800h,然后回复数据字0029h,与图7中记录的状态字和数据字完全一致,且状态字的同步头类型sys_type显示为1,数据字的同步头类型sys_type显示为0,证明了该模块的正确性。

图9 SignalTapⅡ Logic Analyzer观测协议处理及控制功能模块主要信号Fig.9 SignalTapⅡLogic Analyzer observer agreement processing and control functional module main signa

经过多次机载测试试验,记录仪均能完整、准确地接收和响应机载计算机的消息数据,从而验证了记录仪的1553B总线接口设计的有效性。

4 结语

本文提出了一种机载数据记录仪的1553B总线接口设计,记录仪通过1553B总线接口接收机载计算机的消息数据,控制记录仪的工作,避免了飞行时使用RS422或USB2.0总线进行通讯存在数据传输不稳定、数据失真的问题。接口模块以FPGA为中央控制器实现记录仪的功能需求,并采用Signal-TapⅡ工具代替传统的逻辑分析仪对系统设计进行在线测试。通过多次机载测试,测试结果表明,该设计实现了系统功能,从而验证了记录仪的1553B总线接口设计的可行性。

[1]张旭.带多接口的多通道数据采集记录仪研究与实现[D].西安:西安电子科技大学,2013.

[2]陈瑜,李爱军,王雯,等.一种机载大容量总线监控器的设计研究[J].计算机测量与控制,2014,22(6):1815-1817

[3]龙志强,李讯,李晓龙,等.现场总线控制网络技术[M].北京:机械工业出版社,2011.

[4]尹占芳,曹宇,杨福广,等.基于FPGA的1553B总线终端设计[J].计算机测量与控制,2013,21(5):1288-1290.

[5]王欢,靳鸿,陈昌鑫,等.模块化和柔性化的机载数据记录仪设计[J].工程设计学报,2014,21(4):373-377.

[6]张惠宇宸,王晓曼,刘鹏,等.基于FPGA的1553B总线接口设计[J].吉林大学学报,2015,33(2):26-30.

[7]赵杰,甄国涌,王宇,等.基于FPGA的1553B总线测试系统设计[J].科学技术与工程,2013,34(13):10337-10343.